- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于流水线结构的DDS多功能信号发生器设计

摘要:在应用FPGA进行DDS系统设计过程中,选择芯片的运行速度优化和资源利用优化常常是相互矛盾的,从发展趋势和运算要求看,系统速度指标的意义比面积指标更趋重要。基于此,介绍了一种流水线结构来优化传统的相位累加器,在QuartusⅡ开发环境下搭建系统模型、仿真及下载,并采用嵌入式逻辑分析仪分析和验证了实验结果。该系统可以完成多位频率控制字的累加,能够产生正弦波、方波和三角波,具有良好的实时性。

关键词:流水线技术;超高速集成电路硬件描述语言;现场可编程门阵列;相位累加器

随着现代电子技术的不断发展,在通信系统中往往需要在一定频率范围内提供一系列稳定和准确的频率信号,一般的振荡器已不能满足要求,这就需要频率合成技术。DDS是第3代频率合成器,它采用全数字技术,具有频率切换时间短、频率精度和分辨率高、输出相位连续、易于控制等优点。

现场可编程门阵列(FPGA)器件具有工作速度快、集成度高、可靠性高和现场可编程等优点,并且FPGA支持系统现场修改和调试,采用FP GA设计的DDS具有电路简单,性能稳定等特点,也能满足绝大多数通信系统的使用要求。而在DDS相位累加器的设计当中,传统的累加器采用多位全加器直接相加的方式来实现,但随着频率控制字位数的增加,系统的实时性会大幅降低。针对这一问题,本文提出了一种流水线结构的相位累加器,该结构能够缩短运算时间,提高整个系统的实时性。

本文介绍了DDS的基本原理,阐述了基于流水线结构的累加器的设计方案及具体的设计方法,采用嵌入式逻辑分析仪分析了正弦波、方波、锯齿波和三角波等波形,并给出了计算机仿真和实验结果,最后总结了该系统的特点。

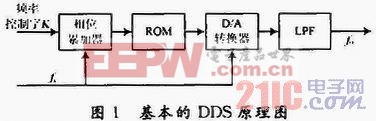

1 DDS基本原理

如图1所示,基本的DDS结构一般由4个模块构成,分别是相位累加器、波形存储器ROM,D/A转换器和低通滤波器LPF。

系统时钟fc为基准频率源,K为频率控制字,通过改变K的数值可以改变DDS的输出频率,在fc上升沿到来时,相位累加器会对频率控制字K进行相位累加,累加结果即是波形存储器ROM中幅值的地址数据,经过寻址,幅值由ROM输出到D/A转换器中,D/A转换器将由二进制编码的数字信号转换为模拟信号输出,该模拟信号再经过低通滤波器的滤波就可以得到平滑的波形曲线。

DDS的输出频率为:

fo=(K/2N)fc (1)

式中:N为相位累加器的位数;fc作为基准频率源一般是给定的数值,因此,决定DDS输出频率的因素分别是频率控制字K和相位累加器的位数N。当K取最小值1时,DDS的输出频率即是它的最小分辨率:

fo=fc/2N (2)

2 流水线相位累加器的设计

相位累加器是DDS的重要组成部分,在基准时钟控制下,它用来实现线性数字信号的逐级累加,信号范围从0加到累加器的满偏值,由此得到相应的相位数据,而相位累加器的频率就是DDS输出信号的频率。在通常的电路优化设计中,累加器模块采用超前进位加法器,这种结构克服了串行进位引起的时间滞后,很大程度上提高了加法器的运算速度,但仍有不足。为了提高DDS频率转换速度和实时性,本文提出了一种流水线结构来优化DDS的相位累加器。

FPGA的结构特点很适合采用流水线设计,以Altera低成本系列CycloneⅡ为例,不仅有最多达68 416个逻辑单元(LE),每个LE均含有1个四输入查找表LUT、1个可编程触发器等。设计中可将1个算术操作分解成一些小规模的基本操作配置到LUT中,将进位和中间值存储在寄存器中,在下一个时钟内继续运算,整个系统只需要极少或不需要额外的资源成本。

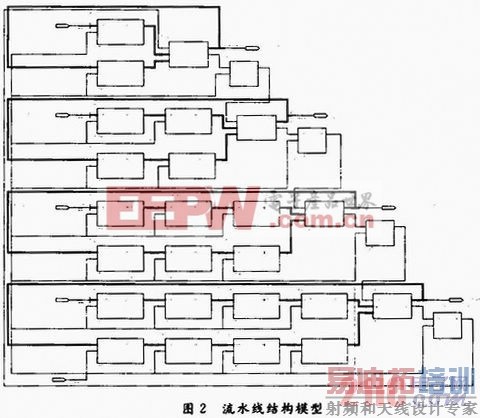

流水线结构的基本原理是将整个电路划分为若干个流水线级,每级之间设置寄存器锁存上一级输出的数据;每一级只完成数据处理的一部分,一个时钟周期完成一级数据处理,然后在下一个时钟到来时将处理后的数据传递给下一级。第一组数据进入流水线后,经过1个时钟周期传到第二级,同时第二组数据进入第一级,数据队列依次前进。每组数据都要经过所有的流水线级后才能得到最后的计算结果,但对整个流水线而言,每个时钟都能计算出一组结果,所以平均计算一组数据只需要一个时钟周期的时间,这样就大大提高了数据处理速度。图2为在QuartusⅡ开发环境下用原理图输入法搭建的流水线相位累加器结构图。该结构由四级流水线构成,每一级流水线的输入字节为8位,分别由8位数据锁存器,8位数据全加器,1位数据锁存器构成,整个系统可实现32位输入控制字的相位累加功能。根据流水线相位累加器的工作原理,首先将32位输入控制字a由低位到高位平均分为4段,每一段为8位,分别以a[0..7]到a[24..32]来命名。将a[0..7]作为第一级的输入控制字输入到8位数据锁存器reg8中,在时钟信号clk上升沿到来之时,reg8暂存的控制字会送入到8位数据全加器adder8中与另一个加法数和进位信号进行全加运算。另一个加法数是来自本级运算结果的反馈,为保持时钟节拍的一致性,该反馈先输入到另一个reg8中暂存,然后在时钟上升沿到来之时输入到全加器进行运算;进位信号来自第四级,该信号也是先暂存在一个1位数据锁存器reg1中再输入到全加器中进行运算。

[p]

第一级流水线经过全加器之后得出运算结果sum[0..7]和进位信号,sum[0..7]作为本级的输出,它是整个累加结果的最低8位,而进位信号经过一个reg1之后作为下一级全加器的输入。

第二级流水线的输入信号是a[8..15],因为上一级共由两级数据锁存器构成,所以在做全加运算之前先分别将输入信号和本级的反馈信号经过2次数据锁存,然后再与来自上一级的进位信号进行全加运算,运算之后的结果作为本级的输出sum[8..15],同时产生进位信号参与下一级的运算。第三级与第四级的工作原理同上,系统每增加一级流水线结构,锁存器也会随之增加一级。

图3为在QuartusⅡ环境下得到的四级流水线仿真波形,时钟信号的频率是200 MHz,占空比为50 %,偏移量为0。为观察方便,输入控制字a和累加结果sum均用无符号十进制数来表示,且输入控制字设定为32,由波形图可见,该系统可以实现32位的相位累加。

3 任意波形发生器的设计及实现

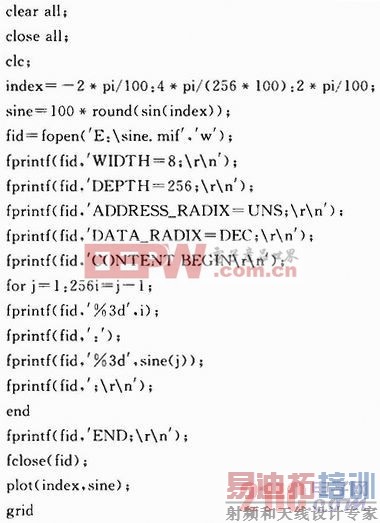

DDS可以根据ROM中存储数据的不同产生多种波形。在QuartusⅡ开发环境下搭建DDS系统模型需要订制波形存储器ROM,根据所需精度的不同,ROM中存储的采样点数也不同。当所需波形数据非常简单时,可以在QuartusⅡ中定制ROM时直接将数据写入新建的mif文件,然后保存即可,当所需波形数据较为复杂时,可以通过Matlab来自动生成所需波形的幅度数据,然后再通过调用mif文件来达到预期目标。以256个点的正弦波为例加以分析说明。

产生正弦波的Matlab程序如下:

width定义的是位宽,depth是深度,也就是将来生成的mif文件含有多少个存储单元,在此处,设定了数据宽度为8位,存储单元数为256,将来在QuartusⅡ中定制ROM时也要相应地将存储单元数设定为256,根据DDS的基本原理,随着设计点数的增加,所得的波形数据会更加准确,通过D/A转化后在示波器上观测的波形也越精准,但所需ROM的存储空间将会呈指数增长,所以要根据实际的需要来综合考虑存储单元的个数。将上述指令在Matlab环境中运行之后就能够得到所需mif文件。

在mif文件生成之后需要将此文件添加进入DDS系统的ROM中,然后进行全局的编译,编译通过后就可以进行工程的下载。具体的波形可以通过示波器来分析,或者使用Quartus Ⅱ自带的嵌入式逻辑分析仪来分析。在使用嵌入式逻辑分析仪分析和观察时,采样信号要根据DDS的时钟信号来确定,待测信号设定为DDS的输出信号,当工程下载到FPGA芯片后,待测信号通过USB-BLASTER反馈至嵌入式逻辑分析仪中,选择不同的数据类型,可以观察到以十进制数据表示的数字信号或者以实际波形表示的模拟信号。

[p]

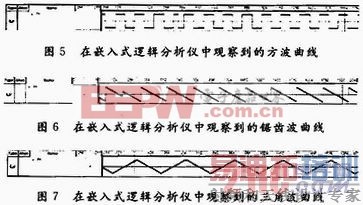

图4为在在嵌入式逻辑分析仪中观察到的正弦曲线。由波形图可以看出,该设计方案可以实现正弦信号发生器的功能。按照相同的方法,修改产生mif文件的Matlb运算指令可以获得方波,锯齿波,三角波等波形。

图5~图7为能产生方波,锯齿波和三角波波形的工程文件下载到FPGA芯片后通过嵌入式逻辑分析仪得到的波形图。由波形图可以看出,该系统能够实现任意波形发生器的功能。

4 结语

本文将流水线相位累加器引进到DDS的设计中,利用电子设计自动化技术进行系统设计,并从嵌入式逻辑分析仪分析和观察了相应的波形,仿真和硬件实验验证了设计方案的正确性。该系统具有结构简单、运行速度快和占用芯片资源少等特点。随着ROM查找表的扩大以及越来越多的直接计算波形数据的方法不断被提出,对DDS整体实时性的要求也越来越高,尤其像目前较为流行的cordic算法及改进的其它插值算法,由于算法本身随着级数的增多,整个系统的频率转换效率就会降低,而流水线相位累加器结构可以很好地解决这一问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:存储器件软误差解决方案

下一篇:Protel使用中遇到的问题说明