- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的光纤通信系统的设计与实现

摘要:光纤通信是现今数据通信系统的主要通信方式,其性能的好坏直接影响数据通信系统的质量。本文采用Verilog语言实现FPGA光纤通信系统的功能。光纤通信系统又包含位同步时钟提取模块、8B/10B编解码器模块和NRZI编解器模块;这些模块都利用了DA(Design Analyz er)、Quartus II以及Modelsim等EDA工具来完成综合与仿真,从仿真的结果可以看出该设计方法很好地满足了系统的要求。

关键词:光纤通信;FPGA;位同步时钟;Verilog

光纤收发器与FPGA技术相结合的方案是现在光纤通信系统的主流解决方案。目前,在超高速光纤通信中还多采用专用的ASIC芯片,但最近各FPGA厂商也相继推出了40Gbps、4x10Gbps、100Gbps和10x10Gbps等FPGA芯片,使基于FPGA超高速光纤通信的实现成为可能。FPGA的可编程特性,具有ASIC芯片无法比拟的优越性。所以基于FPGA的光纤通信有很大的现实意义。

1 光纤通信系统结构设计

光纤通信系统主要由位同步时钟提取模块、8B/10B编解码器模块和NRZI编解器模块组成.主要功能框图如图1所示。数据经8B/10编码后,能在很大程度上平衡位流中0与1的个数,而NRZI编码又做了进一步的平衡,主要是为了使信号状态变化趋于频繁以便位同步时钟提取模块更好、更快的提取出位同步时钟。编码后的信号为LVTTL电平信号,先经电平转换模块转换为PECL电平信号,再由光发送接收模块转换为光信号送入光纤传输介质。经光纤传输后,在接收端先经光发送接收模块把光信号转换为PECL电平信号,再由电平转换模块把PECL电平信号转换为LVTTL电平信号,同时位同步时钟提取模块提取出同步时钟,为解码模块提供参考时钟。最后,接收到的数据经解码后数据输出。

2 位同步时钟提取的FPGA实现

在数字通信系统中,任何消息都是通过一连串的码元序列传送的,所以接收时需要知道每个码元的起止时刻,以便在恰当的时候取样判决。这就要求接收端必须提供一个位定时脉冲序列,该序列的重复频率与码元速率相同,相位与最佳取样判决时刻一致。这种提取定时脉冲序列的过程称为位同步。同步性能的好坏直接影响通信系统的性能,出现同步误差或失去同步就会导致通信系统性能下降或通信中断。

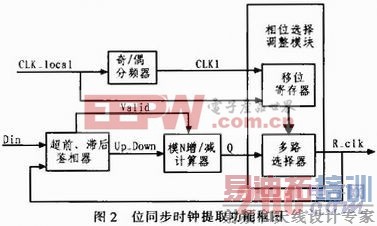

提取位同步信号有多种方法,其中最常用的是数字锁相法。其基本原理是:在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。本设计采用数字锁相法提取位同步时钟,主要由鉴相器、分频器和相位选择调整模块等几大部分组成。其功能框图如图2所示。

[p]

CLK_local是利用FPGA内部的锁相环倍频后得到的高稳定度、高频时钟。CLK1是CLK_local经N次分频后得到的,分频系数N要求满足分频后的时钟CLK1等于所要提取出的位同步时钟R_clk。Din为接收到的码元。Valid为超前、滞后鉴相器的使能输出,Up_Down为超前、滞后鉴相器的比较输出,Valid为逻辑0时关闭模增/减计数器,Valid为逻辑1时开启模增/减计数器,如果位同步时钟滞后时Up_Down的输出为逻辑0,使模增/减计数器进行减计数,如果位同步时钟超前时Up_Down的输出为值为逻辑1,使模增/减计数器进行增计数。

接收到的码元经超前、滞后鉴相器后,如果位同步时钟滞后则计数器减计数,从而通过多路选择器后减少一个单位的延迟,反之如果位同步时钟超前则计数器进行增计数,从而通过多路选择器后增加一个单位的延迟。

3 直流平衡8B/10B编/解码的FPGA实现

8B/10B编码(以下简称8B/10B)作为一种高性能的串行数据编码标准,其基本思想就是将一个字节宽度的数据经过映射机制(Mapping Rule)转化为10为宽度的字符,但是平衡了位流中0与1的个数,也就是所谓的直流平衡特性。同时规定位流中0或1的游程长度(Run Length)的最大值不能大于5,以使得传输过程保持足够高的信号变换频率,这样不仅确保了时钟恢复也使得信息流的直流频谱分量为零或近乎为零,而正是这些特性使得8B/10B编码特别适合光纤等介质的连接和信息传输。

3.1 直流平衡8B/10B编码

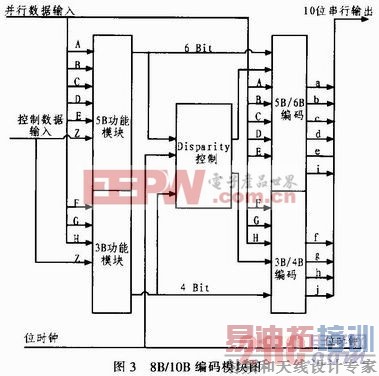

如图3所示,通信适配接口的输入由一个字节的数据(ABCDEFGH)、一个控制信号(Z)以及一个时钟信号组成,其中时钟采样以字节为单位。控制信号Z是数据信号或控制信号的标示位。输入数据ABCDEFGH被分成两部分,其中ABCDE经5B/6B编码生成6比特字符abcdei,而FGH经3B/4B编码得到fghi,最后组合输出得到10比特的传输字符abcdeifghi。

[p]

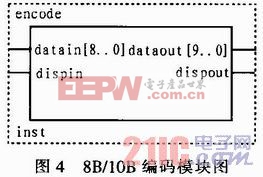

3.2 编码器设计

从编码的种类看,直流平衡8B/10B编码可分为数据字符编码和控制字符编码两种,但是从编码的组成看,它又可分为3B/4B编码、5B/6B编码两部分。根据图3 8B/10B编码模块图将编码器设计划分为3个模块:3B/4B编码模块、5B/6B编码模块和Dispartity运算模块。基于Verilog语言的8B/10B编码模块图,如图4所示。

datain[8:0]为编码数据输入引脚。datain[4:0]为5位5B/6B编码数据输入端,即为ABCDE,其中E为最高位,分别用ai、bi、ci、di和ei表示每一位。datain[7:5]为3位3B/4B编码数据输入端,即FGH,其中H为最高位,分别用fi、gi和hi表示每一位。datain[8]为控制字符编码标示位,用ki表示,ki为1表示为控制字符编码,为0表示为数据字符编码。dispin为8B/10B编码前的RD输入引脚;dispout为8B/10B编码后的RD输出引脚。dataout[9:0]为编码数据输出引脚。dataout[5:0]为8B/10B编码后5B/6B编码模块对应输出引脚。dataout[6:9]为

8B/10B编码后3B/4B编码模块对应输出引脚。

8B10B编码器ModelSim仿真波形如图5所示。其中datain、dispin、dispout和dataout分别为图4编码模块图对应的信号。仿真时选取了D31.2(RD+)、D31.0(RD-)、D28.0(RD+)和K28.0(RD+)作为仿真输入信号。

4 NRZI编/解码的FPGA实现

NRZI(Non-Return to Zero Inverted不归零反转)编码是在数据位1时发生跳变,为0时保持不变的一种编码。在光线通信中,由于光纤固有的特性,信号长时间的置0或置1容易造成数据传输错误,应当尽量避免这种情况发生,NRZI编码能够很好地解决这一问题。前面的8B/10B编码已经在很大程度上缓解了这个问题,但为了进一步提高数据传输质量,在8B/10B编码的基础上加入一级NRZI编码。

4.1 NISEI编码器设计

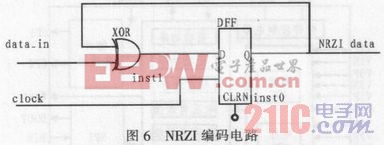

NRZI的编码规则是:数据位为1时发生跳变,为0时保持当前状态。图6为本设计采用的NRZI编码电路。其中,DFF为D触发器,XOR为异或门;data_in为数据信号输入端,数据来自编码后的8B/10B码;clock为NRZI编码时钟,clock时钟频率为data_in码元速率的2倍频(由FPGA倍频电路实现);NRZI_data为NRZI编码器输出。

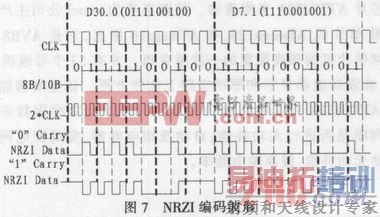

下面以一具体实例说明NRZI的编码过程。8B/10B码D30.0(011110 0100)和D7.1(111000 0100)编码后的波形图如图7所示。经NRZI编码后信号状态变化更加频繁,这些状态变化使得接收器能够持续地与输入信号向相适应,这样就保证了发送设备和接收设备之间的同步。由于8B/10B码的有效编码中都至少有4位“1”,从而保证了传输的信号至少发生4此跳变,以利于接收端的时钟提取。

[p]

NRZI编码器ModelSim仿真波形如图8所示。data_in输入数据分别为D30.0和D7.1。

4.2 NRZI解码器设计

NRZI解码器设计是NRZI编码器的逆过程。图9为本设计采用的NRZI解码电路。其中,DFF为D触发器,XOR为异或门。NRZI_data为信号输入端,数据来自经光纤传输的NRZI码;clock时钟频率同编码起时钟频率,即为NRZI_data码元速率的2倍(由FPGA倍频电路实现);data_out为解码器输出。

NRZI解码器ModelSim仿真波形如图10所示。NRZI_data输入数据分别为D30.0和D7.1编码后的数据。

5 结束语

文中主要用Verilog语言编写了位同步时钟提取模块、8B/10B编解码模块、NRZI编解码模块等来实现光纤通信。8B/10B编码很好地平衡了位流中0和1的个数,特别适合光纤介质的信息传输;NRZI编码使信号的状态变化更加频繁,进一步增强了发送设备与接收设备的可同步性;位同步时钟提取使得发送设备与接收设备保持同步,同时为接收端解码器提供可靠的时钟参考。这几大模块相辅相成,共同维持光纤通信系统可靠、高效的运行。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电器设备中功率因数校正问题仿真方案

下一篇:EDA在数字系统设计中的应用