- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的电梯控制器系统设计方案

本文首先提出了一种基于有限状态机的电梯控制器算法,然后根据该算法设计了一个三层电梯控制器,该电梯控制器的正确性经过了仿真验证和硬件平台的验证。本文的电梯控制器设计,结合了深圳信息职业技术学院的实际电梯的运行情况,易于学生理解和接受,对于工学结合的教学改革,是一个非常好的实践项目。另外,本文提出的电梯控制器算法适合于任意楼层,具有很强的适应性和实用性。

电子设计自动化技术是19世纪末21世纪初新兴的技术,其在数字电路设计和日常的控制系统中已经体现了强大的功能和优势。随着EDA技术的高速发展, 电子系统设计技术和工具发生了深刻的变化,大规模可编程逻辑器件FPGA的出现,给设计人员带来了诸多的方便。HDL(硬件描述语言)是随着可编程逻辑器件(PLD)发展起来的,主要用于描述数字系统的结构、行为、功能和接口,是电子设计自动化(EDA)的关键技术之一。它通常采用一种自上而下的设计方法,即从系统总体要求出发进行设计。

目前从期刊杂志中看到一些采用FPGA实现电梯控制系统的设计文章,在这些文章中看不到针对任意楼层的控制器算法,而针对任意层数的控制器算法是保证控制器实用性和适用性的关键。因此,本文尝试采用EDA技术来设计一个N层电梯控制系统,具体思路是:首先给出电梯控制器的算法,然后在硬件平台上实现并验证。

1 电梯控制系统要求

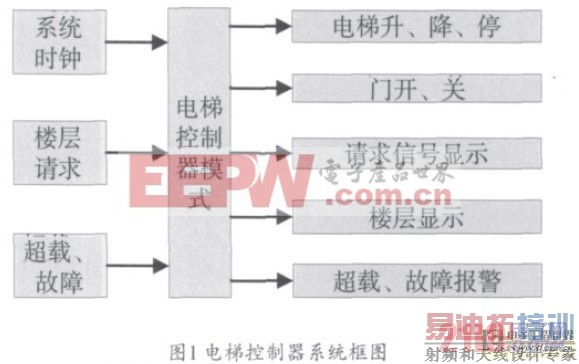

电梯控制系统通常包含图1中的功能:电梯升、降、停;电梯门开、关;请求信号显示、楼层显示;超载、故障报警。其中超载、故障报警需要用到传感器,该控制相对比较简单,因此本文不再展开讨论。

本文着重讨论涉及其他功能的控制器算法。

针对深圳信息职业技术学院第一教学楼的电梯,其电梯控制器实现了以下功能:

(1)电梯内部每层均有相应的STop按钮;电梯外部除顶层外每层都有up按钮,除底层外每层都有down按钮;up按钮被按下表示该层有人要去高层,down按钮被按下表示该层有人要去低层,stop按钮被按下表示该层有人要出电梯。对于stop、up、down按钮,当被按下后,相应的指示灯亮,直到该请求被满足后,指示灯才灭;

(2)电梯运行过程中,上升、下降、停止时相应的指示灯要亮,楼层随时显示;

(3)电梯上升过程中,首先满足向上的需求,对于低层或者向下的需求,在电梯上升过程中会记录该需求,然后在电梯向上需求全部满足后电梯再次下降的过程中给予满足;

(4)电梯下降过程中,首先满足向下的需求,对于高层或者向上的需求,在电梯下降过程中会记录该需求,然后在电梯向下需求全部满足后电梯再次上升的过程中给予满足。

本文设计的电梯控制器,其基本要求就是满足上述实际运行电梯的要求。

2 电梯控制系统实现

2.1 整体方案设计

整体设计由四个模块组成,各模块功能具体描述如下:

a. 分频器模块:该模块实现了任意时钟频率输入,任意频率输出的功能,输出频率精度为1Hz;模块输入为系统工作时钟clk,系统复位信号rst,输出为分频时钟。模块定义如下:

module freq_div(reset,clk,keyclk,liftclk);

模块中keyclk为处理按键时钟,liftclk为电梯运行控制时钟。

[p]

b. 按键请求模块:该模块实现了记录并处理各楼层的up、down和stop按钮被按下的情况,模块端口如下:

module key_req(

reset,keyclk,

stop, //电梯间内部各层按钮,每1位代表1层,当相应位置1时表示指示该层的按钮被按下;

up, //各楼层up按钮(顶层无),每1位代表1层,当相应位置1时表示该层up按钮被按下

down, //各楼层down按钮(底层无),每1位代表1层,当相应位置1时表示该层down按钮被按下;

stop_r, //电梯内各层按键信息

up_r, //电梯外各层向上按键信息

down_r //电梯外各层向下按键信息

);

c. 电梯控制器模块和指示模块:该模块根据各层按钮被按下的情况,控制电梯运行,并设置指示灯。模块定义如下:

module Lift_cONtrol(

keyclk, //处理按键时钟

liftclk, //电梯运行控制时钟

reset, //电梯复位按钮,复位后电梯停在一楼;

stop_r, //电梯内各层按键信息

up_r, //电梯外各层向上按键信息

down_r, //电梯外各层向下按键信息

position, //当前楼层位置,每1位代表1层,当相应的位置1时表示电梯运行至该层;

stoplight, //内部各层按钮指示灯,每1位代表1层,当相应位置1时表示指示该层指示灯亮;

uplight, //除顶层外各层外部按钮指示灯,每1位代表1层,当相应位置1时表示该层up灯亮;

downlight, //除首层外各层外部按钮指示灯,每1位代表1层,当相应的位置1时表示该层的down指示灯亮;

doorlight); //用于开门指示灯,为1表示开门,为0表示关门

d. 显示模块:该模块用于译码显示当前电梯所在楼层,模块定义如下:

module Display(liftclk,position,disp);

[p]

2.2 模块设计与实现

对于分频器模块、按键请求模块、电梯控制器模块和指示模块和显示模块这四个模块,电梯控制器模块和指示模块涉及到电梯各种运行情况的处理,其算法是最复杂的,也是最容易出错的。本文采用使用有限状态机来设计该模块,具体的算法描述如下。

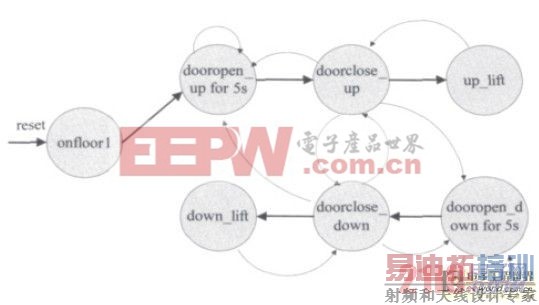

将电梯运行定义为7个状态,具体的状态定义如下:

S0:onfloor1,表示在楼层1;

S1:dooropen_up,上升过程中,电梯开门5s;

S2:doorclose_up,上升过程中,电梯关门;

S3:up_lift,表示电梯上升一层;

S4:dooropen_down,下降过程中,电梯开门5s;

S5:doorclose_down,下降过程中,电梯关门;

S6:down_lift,表示电梯下降一层。

各状态在满足一定的条件下转换,具体状态转换如图2所示。

图2 电梯控制器状态转换图

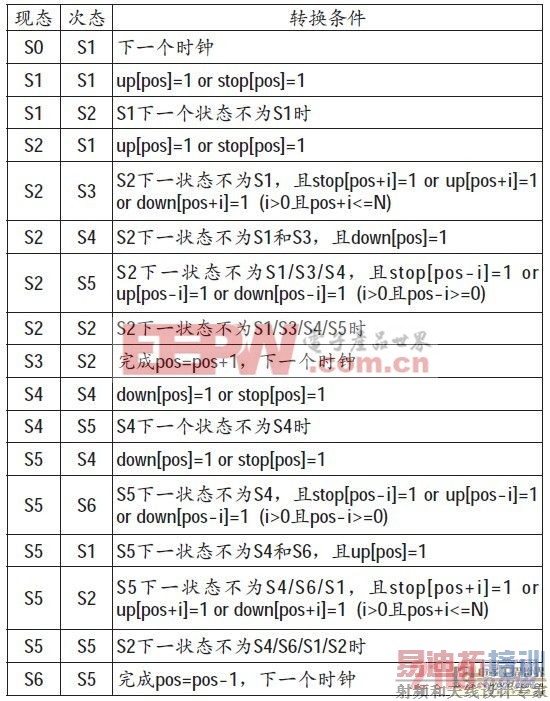

表1 电梯控制器状态转换条件

上表中, pos 表示当前楼层, up[pos ] 、down[pos]、stop[pos]分别表示当前楼层的向上、向下、和停止铵钮的状态。

显然,上述算法并未对楼层数作限制,也就是说该算法适合于任意楼层的电梯控制器。

2.3 仿真验证

本文根据上述算法,采用Verilog HDL语言在FPGA上实现了一个三层电梯控制器。对于实现来说,三层电梯或者多层电梯的控制器只是Verilog代码数量的不同,其算法则完全是本文提出的算法,没有区别。本文只所以实现了一个三层电梯控制器,是因为硬件开发环境的资源(包括按钮的数量、指示灯的数量)仅满足三层电梯控制器的验证。

[p]

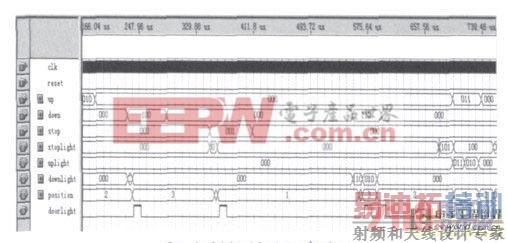

三层电梯控制器的仿真波形如图3所示。

图3 三层电梯控制器的仿真波形

仿真波形说明:电梯内外按钮,当其值由0变为1即表示被按下。图中,各层电梯间内外的铵钮被按下是随机发生的。

由仿真波形可以看出,电梯的运行符合设计要求。

2.4 硬件验证

本文的设计经引脚锁定并下载到硬件开发环境中,经测试完全正确。

具体硬件开发环境为GW48-PK2实验开发系统。

CLK选择clk0,频率可选择为256Hz。

键1、2、3对应电梯内各层的按钮;键4、5对应一二楼层电梯外的向上铵钮;键6、7对应二三楼层电梯外的向下铵钮;键8对应系统复位键;灯1、2、3指示电梯内各层的按钮被按下;灯4、5指示一二楼层电梯外的向上铵钮被按下;灯6、7指示二三楼层电梯外的向下铵钮被按下;灯8指示开门。

电梯所在层数由数码管1指示。

3 结论

本文的电梯控制器设计,结合了深圳信息职业技术学院的实际电梯的运行情况,易于学生理解和接受,对于工学结合的教学改革,是一个非常好的实践项目。另外,本文提出的电梯控制器算法适合于任意楼层,并在FPGA开发环境中进行了验证,具有很强的适应性和实用性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...