- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

印刷电路板叠层基本的经验法则

印刷电路板的叠层用于具体说明电路板层的安排。它详细指定了哪一层是完整的电源和地平面,基板的介电常数以及层与层的间距。当规划一个叠层的时候,也要计算走线尺寸和最小走线间距。

生产限制会严重地影响叠层,通常,电路的走线密度越大,每一英雨的生产成本就会越高。

本文将详述规划叠层的一些基本的经验法则。

1、电源和地的规划

首先设计电源和地层。规划一个电源和地系统时,首先要确定信号的上升时间,信号的数量,以及电路板的物理尺寸。

在物理尺寸中包括推测走线的宽度。在这一阶段,走线宽度的假设并不是特别严格。

下一步,利用完整的、平行的和指状的地平面模型估计自感和互感。此时,通过已经清楚了哪个模型更适合设计。注意,对于指状的地模型,所有的走线都相互影响。此时通常已经清楚了哪个模型更适合设计。注意,对于指状的地模型,所有的走线相互影响。对于平行的模型,沿着同一平行栅格由放的走线相互影响。对于完整的地平面模型,只有相邻的走线相互影响。

如果要使用一个完整的地平面,应安排地和电源平面成对使用。在一个叠层设计中,完整平面对称使用。可以帮助避免电路板的变形。如果一个板子只有一个完整平面,偏一侧,则将使板子明显变形。

如同地平面一样,电源平面可以作为信号返回电流的低电感路径。假设在电源和地之间有足够的旁路电容,传输线跃起在电源平面上的布线,与电源地平面上的布线方法相同。带状传输线的布线可以在一个电源层和一个地层之间,或在两个电源层之间。

2、机框层

有时候需要在数字系统之外走一个信号。对于这种应用,可以选择一个低速或上升时间受控的驱动器。这是一个好的选择,因为它减少了外部的辐射,对于满足FCC的规定会有所帮助。

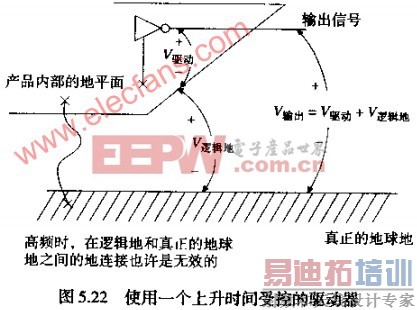

如果驱动器的地连接到通常的数字逻辑地上,有效的驱动输出等于它的设计驱动电压加上任何出现在数字逻辑地上的噪声电压,如图5.22所示。

众所周知,数字逻辑地的高频噪声电压非常严重。地传递的波动电压是由许多返回信号电流通过它们的自感引起的。对于数字电路,这些高频波动很小,不足以产生问题,但是大大超过了FCC的限度。任何引出机壳的线,如果连接到数字逻辑地,在FCC测试时几乎总是失败的。

如果没有其他的预防手段,上升时间受控的驱动器会显著地拾取地噪声并在机箱外广播。

解决这个问题的一种方法是在叠层中加入一个机框平面。这一平面紧贴一个接地平面,使时间受控的驱动器附近,沿着一个连续的轴线,将机械平面通过螺丝钉焊接或熔接到外部机框,在高频部分,我们已经有效地把数字接地一面短接到机框。这样,在这个点上就减少了数字噪声的数量,也减少了上升时间受控的驱动器传到外部的噪声。

因为普通电容的引脚电感太大,所以不能用它们实现机框地和数字地之间的短路功能。只有在机框平面和数字地平面之间有非常大的宽而平行的表面面积,才有足够低的电感,从而有效地把两个平面答非所问在一起。

采用机框平面方式,在低频部分,数字逻辑和外部的机框保持着隔离,对于安全或其他方面,这都是非常必要的,如果隔离无关紧要,简单地直接把数字逻辑地短接到机框即可,而不必使用一个单独的机框层。

连接过程可以沿着受控的驱动附近的连续轴线,通过螺丝钉焊接或熔接到外部机框来完成。

当使用一个机框平面的时候,在叠层中要和其他一些完整平面均衡使用。因为机械原因,在叠层中总是倾向于对称地安排平面。[p]

3、选择走线尺寸

把走线尽量挤在一起可以增加电路密度。非常密集的设计只需要较少的电路板层。既然印刷电路板费用与层的数目和板子的表面面积成正比,所以我们总是希望能够使用最少的层数来达到这个目的。

走线越细,间隔越近,产生的串扰就越多,所能输送的功率也就越小,这种在串扰、走线密度和功率之间的权衡,对低成本的产品设计非常关键。

让我们首先来处理功率输送能力的问题,因为这个约束条件最简单。

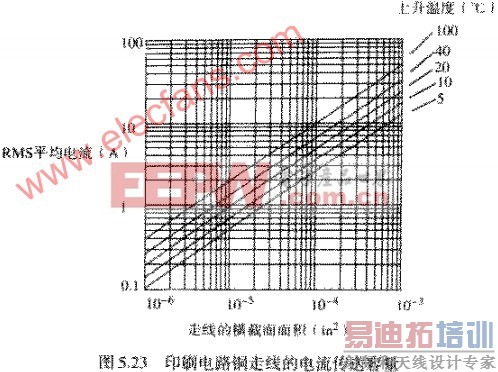

印刷电路走线的功率输送能力主要取决于它的横截面面积和容许的上升温度。对于一个给定的横截面面积,一条走线上高于环境的温度的粗略地与它耗散的功率成正比。升温在高是不可靠的,而且会使附近的数字电路变热。在数字产品中,保守的走线加热上限是10℃。

图5.23描述了最大的功率输送能力和温度上升的关系。在图5.23中,水平轴显示的是横截面面积,单位为IN的2次方,纵轴显示的是该线在给定升温值时的允许电流。

举例来说,一个0.010IN宽的1OZ的铜走线(0.001 35IN厚),在温度升高10℃的情况下,可以安全地通过750MA的电流。

除了大的电源分配总线,功率很少成为一个重要的约束条件,随着薄膜技术的广泛使用,由于其走线的横截面面积非常小,布线的加热限制可能变得更普遍。

走线宽度上的第二个不太重要的限制来自生产制造过程。表5.1列出了在各种不同的生产过程中可达到的最小走线宽度。

对于任何生产过程,当线宽接近可达到的最小走线宽度时,生产量将会降低,而且费用将会上升,这个因素将阻止大多数的设计者使用可达到的最小线宽。

其他一些因素会使走线宽度增加,腐蚀程序控制得不好,会造成线宽的变化比较大。在小线宽时,线宽变化的百分比决定着阻抗容限的百分比,有时这种变化可能是无法接受的,要想精确控制阻抗,可能需要使用比可达到的最小走线宽度字贡得多的线。

对于功率,费用和阻抗容限的考虑通常促使选择特定的线宽。给于给定的线宽,阻抗约束决定层高。

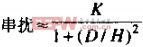

然后使用关于串扰的公式,参见式 ,算出相邻走线间隔的最小值,这个值称为最小走线间距。在走线之间的未用距离称为走线间隔。走线间隔加上线宽等于走线间距。

,算出相邻走线间隔的最小值,这个值称为最小走线间距。在走线之间的未用距离称为走线间隔。走线间隔加上线宽等于走线间距。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...