- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

从StratixIII及CycloneIV开发板谈FPGA配置

最近为了给几个新同学介绍实验室所使用的两个开发板——StratixIII开发板和DEII-CycloneIV实验箱,所以整理了下关于两个板子FPGA的配置过程,从中自己也获益很多。两款芯片的配置方式算是代表了如今Altera主流的方式吧。

首先介绍下CycloneIV实验箱。

实验箱提供了简单的配置流程,首先简单介绍下CycloneIV的配置部分电路。

图中圈起部分及为FPGA配置部分电路图解,其中重点是其使用的配置芯片为EPCS64,这也是最为常用的配置方式。

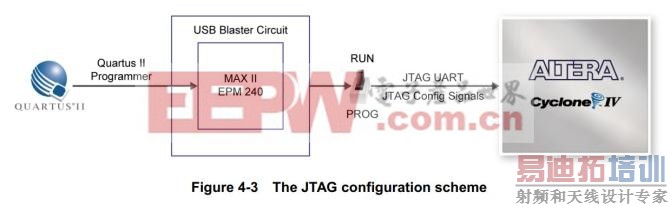

首先对FPGA可以通过USB Blaster然后以JTAG模式进行下载,如下图:

图中有个拨码开关,其中有两个可选端,一个是RUN,一个是PROG,简单的理解就是运行和程序配置。这里我比较认同RUN的含义,老师们给我们讲的时候都把将程序之间“烧”到FPGA也称作配置。但我个人觉得,运行“这个词很贴切,就好像我们是把一个文件写入到FPGA在其中运行一样。这个过程很简单,每个工程编译完成后都会生成一个sof文件,将它烧到FPGA里面就行了。

可是这样的配置每次掉电后都需要重新烧写,所以这里就需要配置芯片EPCS64来起作用了。我们把程序烧写到它里面,每次上电后,就自动由它来对FPGA进行配置,这样就不需要我们一次次的上电烧写了。

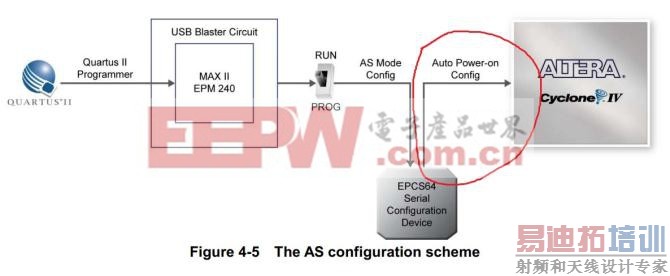

下面介绍下EPCS64的烧写了。手册中给出了它的AS模式配置:

[p]

如图,将拨码开关拨至PROG端,就可以用PC对EPCS64配置芯片进行烧写了。

1、先生成一个pof配置文件。在File下选择Convert Programming File,这部分操作后面也会提到。

2、将拨码开关拨至PROG,在Programmer中将模式选择为AS mode,选择pof文件。

3、Start,开始烧写。这里可以发现,过程较sof文件的烧写要漫长得多。

这里需要注意的是,其实上面图中圈起部分是很容易引起误解的。EPCS64要对FPGA进行配置时,拨码开关仍然需要拨回到RUN端,可以理解成,只是换成了配置芯片把程序烧写到FPGA中运行”罢了。

下面介绍另一种对EPCS64的配置方式,我们希望通过JTAG模式来对EPCS64进行配置。我们暂且称它为jic文件模式。这里我们可以简单把EPCS64当做一个Flash存储器,既然是存储器那肯定可以利用FPGA来对它进行写入操作。这种模式下,就是通过JTAG对FPGA进行写入操作,然后让FPGA来对配置芯片进行写入操作。

首先,还是通过Convert Programming File来生成一个jic文件。

我们可以看到在下面Input files to convert设置的时候,其中比之前的pof文件生成多了一个Flash Loader,也就是说,这里选的FPGA就是用来Loader配置芯片的。

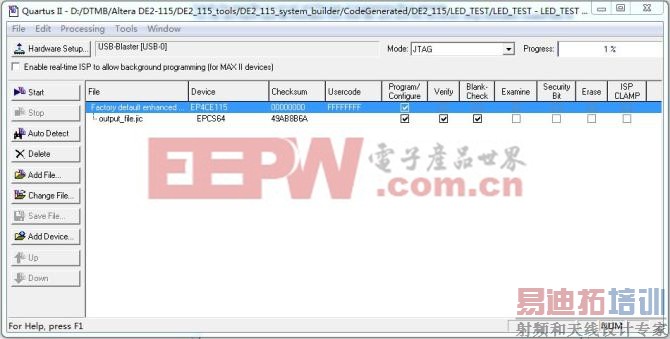

生成了jic文件后,在Programmer中选择JTAG模式下载就行了,如下图:

这里也有整个过程的体现,上图的下面也显示了整个烧写过程的简单示意图。

[p]

Start之后,就完成了我们对EPCS64的烧写了。其中并不需要再去拨动拨码开关了,我们只需一直在RUN下面用JTAG就可以对两者进行烧录了。

这里出现了个小插曲,上面过程都是在10.0里面完成的,在使用Quartus9.0的时候一直不能成功,如下图:

中途报错了,提示:

对于这个问题一直纠结了很久,后来无奈得认为是Quartus版本bug,对比两个版本Programmer里面可以看到,9.0下面Checksum部分都为0,可见它无法检测。只要换到10.0就行了,后来发现,其实别的版本也都可以,唯独9.0不行……甚是不解。

另外在网上看到很多朋友说不要勾取Verify和Blank-Check的选项可以下载成功,可是我们试过之后虽然可以下载成功,但是却无法配置FPGA,程序烧进去没有任何反应,所以还是觉得Quartus版本的问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:防止印制板翘曲的方法

下一篇:光电PCB技术介绍