- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

NIOS开发结构基础简介

我们使用VHDL语言,根据FPGA管脚与数码管和按键管脚的连接,通过一系列的语句控制管脚电平的高低,从而让FPGA实现数码管显示功能。可见,对于比较简单的功能实现,可以像这个例子中那样,直接控制最底层资源,甚至对每个管脚在每个时刻的电平输出了如指掌。

但是,如果设计稍显复杂,那么对底层细节的过多关注就会成为一种累赘。

试想我们平时在电脑上编写C程序,比如在显示器上输出一行字,我们只用一句printf()即可完成,至于打印命令怎么传到显示芯片上,哪个芯片管脚怎么 变化,又怎么传到显示器上输出,诸如此类涉及底层硬件的问题,我们没必要关注太多。于是,我们把用printf()这类高级语言描述设计逻辑的工作称为软 件设计。显然,软件只是一种抽象的看不见摸不着的东西,它的结构接近于人类思维逻辑。无论软件再怎样构思精妙,只有在硬件上才能体现出实际效果。

做计算机开发应用程序的时候,硬件是现成的,软硬件之间的桥梁早就由操作系统给你搭好了,我们只需专心完成软件的构思和设计就OK。

显而易见,软硬件的分工会给电子设计带来极大的方便,自然有人把这种分工方式引进FPGA设计领域,琢磨着怎么在小小的FPGA上也搞个软硬件协同设计,负责硬件设计的和负责软件的各司其职,最后pia一整合,效率倍增。

来看看nios是怎么做的。拿出DE2开发板,上面很多外设接口和与之连接的芯片,那是硬件,中间有一块大的CycloneII芯片,里面是空的,等着我 们编写程序下载到里面运行,前篇文章我们用最原始的方法写了个数码管控制器,这次我们换种方法,同样是数码管控制器,用软硬件协同设计来完成。

跟计算机对比,硬件我们有了,软件就用C语言来写,但是nios系统可没提供WinXP,也就是说软件和硬件之间的那座桥还得自己解决。

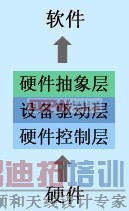

看上图,这座桥分为3个层次:硬件控制层,设备驱动层,硬件抽象层(简称HAL)。既然是软硬件的过渡部分,那么这3层的设计需要对硬件和软件都有一定程度的了解,姑且称之为“软硬件混杂设计”吧。

每一层所要完成的任务,就是整合和简化硬件操作细节,整合,再整合,使其一目了然。

1> 硬件控制层

与硬件直接打交道的是硬件控制层。

上面提到,搭“桥”的目的是让软件设计人员可以完全忽略硬件操作细节,因此,我们希望所有的硬件细节都能在这层解决,并向设备驱动层提供整齐的“接口”。之前的例子可看作硬件控制器的雏形,但还缺少与设备驱动层的接口。

何为“整齐”呢?比如说,设计数码管控制器,我想让它显示数字“5”,最好的方法是,我将数据“5”和表示“显示”的命令从设备驱动层传给硬件控制层,直 接告诉它:我要“数码管”“显示”“5”。至于要控制哪个管脚电平高低才能显示“5”,全由硬件控制层负责。

类似这样分工合作的例子在日常生活中屡见不鲜。比如说,邮局要将一封信送给家住A小区的张三,邮递员把信放入A小区的信箱,小区物业再去确认张三的具体住处,把信最终送到张三手中。

类比可见,邮局相当于设备驱动,物业相当于硬件管理器,张三则是具体的硬件,邮局和物业之间的接口是物业提供的信箱,设备驱动和硬件管理层之间的接口,我们称之为“寄存器”,同样由硬件管理层提供,“寄存器”是两层之间得以明确分工和相互联系的关键。

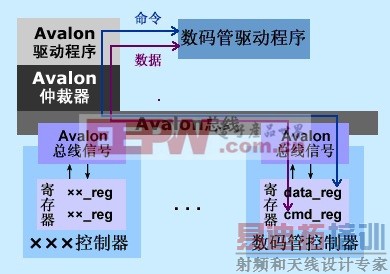

设备驱动开发人员眼中的硬件就是一组寄存器的抽象,通过读写寄存器间接控制硬件行为。

那么,在数码管控制器里加入一个数据寄存器和一个命令寄存器:![]()

data_reg存储待显示的数据,cmd_reg为‘1’时显示,为‘0’时清空。

2> Avalon总线

你可能会说,这有什么?在每个硬件管理器和设备驱动之间都建立一个通道呗。这是最直接的办法,但显然不是最好的办法。试想,城市为什么要建高速公路呢?多 修几十根羊肠小道不也一样能跑车吗?有人回答:为了收养路费呗。$%@! 小路上开车,速度慢且不说,管理协调是个大问题,是一条大公路容易管理,还是几十根羊肠容易理顺?

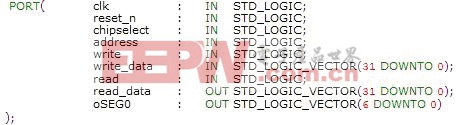

好了,回到正题,nios系统需要一条“高速公路”,称为“总线”,“总线仲裁器”则行使“交通管理局”的角色,控制数据的进出,并为每个硬件提供一个进 出“高速公路”的接口,用“地址”来标识这个接口的位置。nios采用的是Avalon总线,它有着一套接口规范:

同步时钟 clk

片选信号 chipselect

地址 address

读请求 read

读传输 readdata

写请求 write

写传输 writedata

这些是比较重要的接口信号,其它的不一一列举了。硬件控制器要接入总线,必须遵循接口规范,就像高速公路出口必须摆个收费站一样。

那么在数码管控制器里加入Avalon总线信号:

既然加入了两个寄存器和avalon信号,就需要对硬件逻辑进行必要改动,大致过程是,当chipselect和write有效时,将 write_data赋给address对应的寄存器;当chipselect和write有效时,将address对应寄存器的值赋给 read_data。另外,根据这两个寄存器的内容决定数码管输出信号oSEG0。代码不贴出来了,具体见工程压缩包。

3> 设备驱动程序

其实,“总线仲裁器”也可看作一种硬件控制器,只不过它管的不是具体的硬件,而是负责数据的传输。那么它也有自己的设备驱动,封装了总线操作的细节。既然总线是现成的,我们秉承“拿来主义”的原则,甭管它怎么实现的,会用就行。

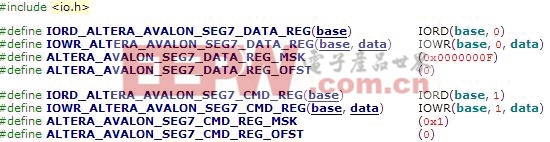

例如,数码管设备驱动要把数据“5”和“显示”命令传给数码管控制器,设计两个函数,由于数据和命令的传递必须经过总线,那么需调用总线驱动函数IOWR(基地址, 偏移量, 数据),另外,读取寄存器用到IORD(基地址, 偏移量),这两个函数在io.h>里。

io.h>的路径是..alterakits ios2_60componentsaltera_nios2HALinc。

至此,“桥”搭完。

函数功能从字面上很好理解。刚才定义两个寄存器时,data_reg在前面,所以偏移量是0,cmd_reg在后面,偏移量是1。××_REG_MSK称 为掩码,avalon总线数据接口共32位,但我们设计的data_reg位宽是3,cmd_reg位宽为1,掩码的作用在于告知寄存器宽度,知道就行, 实际上用不着。××_REG_OFST是寄存器内的偏移量,这里同样用不着,先写上吧。

OK,我们的数码管设备驱动文件正式出炉了,看看是不是简洁明了很多啊?

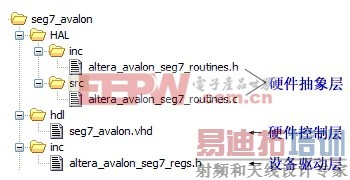

4> 硬件抽象层(HAL)

设备驱动程序封装的仅仅是对某个寄存器的一次读写操作,功能单一,需要在硬件抽象层再做一次封装。

直接将这些函数列出来,一目了然,不作多余的解释了。 [p]

[p]

至此,“桥”搭完。

接下来在把我们的“数码管控制器”加入sopc builder系统中。

现在几乎所有讲nios的书都会提及自定义用户外设,而且用的都是altera官方提供的例子PWM,本文的“数码管控制器”就是照着它依葫芦画瓢改过来 的,呵呵,惭愧惭愧,之所以想改它,一是因为它用的是verilog而不是VHDL,而大多数人先接触却是VHDL;二来PWM的显示效果似乎不太明显, 改成数码管显示相对比较有成就感;第三,PWM的逻辑稍微有一点点复杂,我们的重点在于说明怎样自定义外设,当然例子越简单越好。

既然是照着PWM原样改的,所以本文工程的结构与之保持高度一致,将其加入sopc builder的步骤也差不多,这里我就不再码字了,各位照着书上做吧:

《SOPC嵌入式系统基础教程(周立功等著)》第8章……

再接下来,建立一个包含“数码管控制器”的nios系统,并编写应用程序,实现从0到9计数。

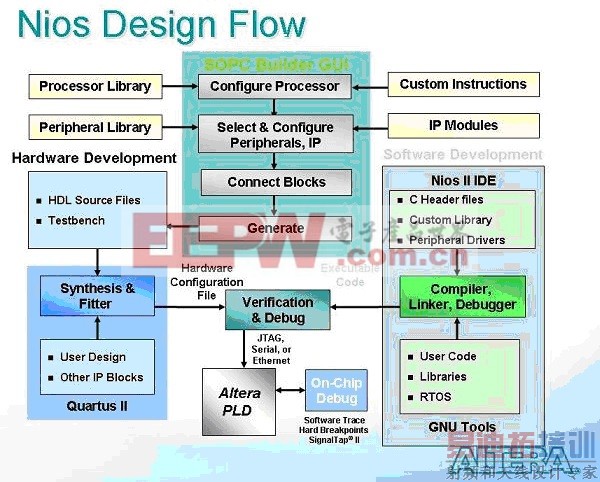

贴张官方的nios设计流程图,看起来很漂亮是吧,不愧是altera的东西,大而全而不乱。

先说最中间的SOPC Builder,它的任务是建立一个“以Nios CPU为核心,以Avalon总线为纽带,将各种硬件设备连接起来”的nios系统;这个系统要在FPGA中运行,所以必须挂靠一个Quartus II工程,用左边的Quartus II进行分配引脚等等工作,生成硬件系统;接着,右边的Nios II IDE就可以在这个硬件系统上设计应用程序了;最后将硬件系统和软件程序分别下载到FPGA芯片上,大功告成。

下面step by step

1> Quartus II 新建一个工程名,工程名DE2_SEG7。

2> Tool → SOPC Builder 打开SOPC Builder。

3> System Name: nios2_system 选VHDL。

一个包含“数码管控制器”的最小系统至少由3部分组成:CPU必不可少,RAM存储代码,还有刚才设计的seg7_avalon。

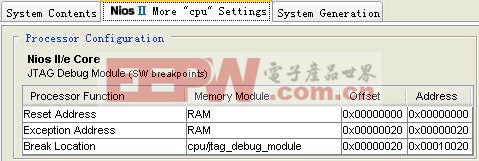

4> 加入Nios II Processor,选Nios II/e,精简型够用了。

5> 加入On-Chip Memory,类型选RAM,位宽默认32 bits,Total Memory选48Kbytes,等会儿软件要占用四十多K空间。

6> 加入seg7_avalon。

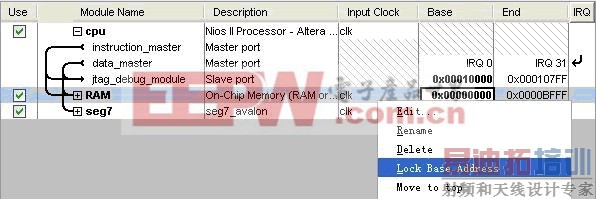

7> 将这三个组件的名称改好看点,然后设定RAM的基地址为0x00000000,再右键锁定基地址,如图:

为什么要锁定RAM的基地址为0呢?点选第二个选项卡,可以看到Reset Address对应着RAM,系统的复位肯定要从地址0开始。

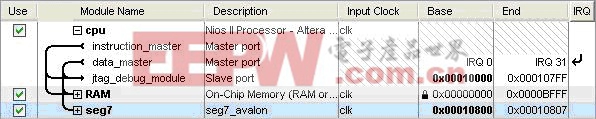

8> 由于刚才人为改动了地址分配,弄乱了,让系统自动再分配一次,当然被锁定的RAM基地址是不会变的。System →Auto-Assign Base Addresses。最终系统组件列表如下:

注意,seg7的地址范围是0x00010800→0x00010807,占8个地址,nios系统的地址按字节分配,也就是说,每个字节占用一 个地址,数码管控制器中定义了两个寄存器,avalon总线规定每个寄存器占32位(实际上是不是32位它就不管了,反正按最大32位分配),这样两个寄 存器共占去8个字节,自然需要8个地址。

9> 点击Generate生成nios系统,回到Quartus II。

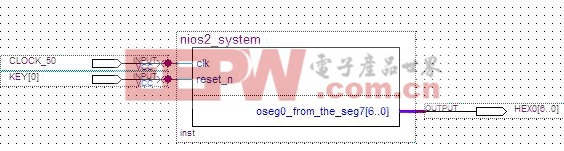

10> 新建一个顶层文件File→New→Block Diagram/Schematic File,引入nios II系统,增加输入输出引脚。然后,Assignment→Import Assignment,添加引脚分配文件(在DE2光盘目录下的DE2_tutorialsdesign_files DE2_pin_assignments.csv),改动顶层文件的引脚名称使其与.csv文件中保持一致。

11> 编译,查看编译报告,可见,48K的RAM占用了芯片83%的memory bits,差不多耗光了。

12> 硬件部分已经搞定,关掉Quartus II,打开Nios II IDE,切换到工作目录下。

13> File→New→C/C++ Application,SOPC Builder System选择nios2_system.ptf(就是刚才Generate Nios II系统生成的东东),再选模板Hello World(纯属偷懒 ),顶上的name改成seg_example,Finish。

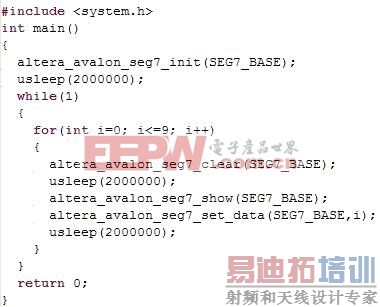

14> 改动hello_world.c,代码的功能为:先初始化数码管,等待2秒钟,再进行0-9的循环,循环过程中穿插2秒钟的清屏。SEG7_BASE的宏 定义在system.h中,实际上就是在SOPC Builder中的seg7_avalon的基地址0x00010800。

15> Project→Build Project,得到编译报告,软件占用了7K空间……![]()

16> 下载到DE2板上,运行,数码管不停地闪啊闪。

OK,从硬件到软件的一条龙讲完了。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:项目教学在电子工艺实训环节中的应用分析

下一篇:IPC-7351

LP软件使用指南