- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Logical Effort理论的全新IC设计方法

本文分析了传统IC设计流程存在的一些缺陷,并且提出了一种基于Logical Effort理论的全新IC设计方法。

众所周知,传统的IC设计流程通常以文本形式的说明开始,说明定义了芯片的功能和目标性能。大部分芯片被划分成便于操作的模块以使它们可以分配给多个设计者,并且被EDA工具以块的形式进行分析。逻辑设计者用Verilog或VHDL语言写每一块的RTL描述,并且仿真它们,直到这个RTL描述是正确的。

得到RTL描述之后,接下来就是利用逻辑综合工具来选择电路的拓扑结构和门的大小。综合工具比手工花更少的时间得到优化路径和电路图。综合的电路通常逻辑功能是正确的,但时序是基于近似负载模型评估得到的。

电路设计完成之后,开始版图的实现。版图通常可以定制也可以用自动布局布线工具产生。接下来,DRC、ERC、LVS等被用来验证版图,后版图时序验证工具用从版图提取出来的电阻、电容数据来验证设计是否满足时序目标。如果电路设计阶段的时序评估不精确,版图后的时序肯定不能满足,电路必须被修改,再执行综合到版图的过程。

在电路设计过程中,最大的挑战是满足时序说明,即时序收敛。如果时序没有问题,电路设计将变得更加容易。目前的EDA界都意识到这一点:要想在版图阶段达到时序收敛,通常应该在综合阶段就考虑更多的物理设计信息。因此,现在很多工具在综合阶段进行预布局布线,以便在综合阶段尽可能多地了解后端信息。

其实这样做并不是从本质上解决问题,因为在综合阶段的时序评估还是基于负载模型的理论,只是现在的模型比以前的要精确一些,但是与实际的版图提取的负载还是有误差,因此得到的时序收敛并不一定可信。不过这些方法可以减少迭代次数,但不能真正消除迭代。

为了预知时序,其实应该建立一个非常可信的延迟预算模型,也就是这个模型的延迟预算应该非常可信。可信是指如果它预知电路1比电路2要快,那么实际中确实是这样。但是基于负载模型的方法不是非常可信,它需要精确的寄生参数信息,但在版图没有得到的情况下,你是不可能有精确的寄生参数信息的。因此需要建立另外一个延迟模型,使得它不需要寄生参数信息也能得到可信的延迟估算。

Logical Effort方法采用的延迟预算模型就是这样的一个模型,Logical Effort方法是评估CMOS电路延迟的一个简单方法。该方法通过比较不同逻辑结构的延迟来选择最快的候选者,该方法也能指定一条路径上适当的逻辑状态数和逻辑门的最好晶体管大小。它是设计早期评估可选方案的理想方法,并且为更加复杂的优化提供了一个好的开始。

Logical Effort延迟模型

建模延迟的第一步是隔离特定的集成电路加工工艺对延迟的影响。通常,把绝对延迟表示为两项之积:一项是无单位的延迟d,另一项是特征化给定工艺的延迟单位τ。即dabs=dτ。τ可以计算出来,例如在0.6μm工艺下τ大约为50ps。

延迟d通常由两部分组成,一部分叫本征延迟或寄生延迟,表示为p,另一部分正比于门输出端负载的延迟,叫做effort延迟,表示为。即:d=f+p。

effort延迟依赖负载和逻辑门驱动负载的特性。我们引入两个相关的项:Logical Effort(LE)捕捉逻辑门的特性,electrical effort(g)特征化负载的影响。即f=LE*g,所以d=LE*g+p。

Logical Effort捕捉逻辑门的拓扑结构对它产生输出电流的影响,它独立于晶体管的大小。electrical effort即门的增益,描述门的电子环境(即与门连接的东西)怎样影响它的性能,也可以说门中晶体管的大小怎样决定门的负载驱动能力。增益的简单定义是:g=Cout/Cin。其中Cout为逻辑门输出端负载的电容,Cin为逻辑门输入端的电容。

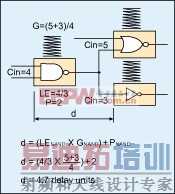

至此,我们可以如图1所示那样来计算延迟d。

从这里我们看到,延迟依赖门的增益,而不是它的精确寄生参数。同时,Logical Effort理论中还有两个非常完美的结论。

少的逻辑状态不一定能产生最快的电路延迟。那么多少个逻辑状态将产生最快的电路延迟呢?对于反向器组成的电路,Sutherland指出:最快的反向器结构发生在Cout=3.6Cin。当Cout=3.6Cin时,我们称反向器的负载为完美负载。我们可以定义门的增益为Gain=Cout/(3.6*Cin),并把它作为电路单元(cell)的延迟预算。

最快的电路拓扑结构有一致可变的Gain,因此在物理综合阶段,可以通过仔细调整Gain的值,保持时序不变。 [p]

全新的IC设计方法

在进行IC设计过程中,最重要的就是怎样快速从RTL得到GDSⅡ。利用Logical Effort理论,我们将建立新的IC设计方法。

首先对综合库进行分析。库可以是.lib、LEF、GDSⅡ等。库中每个功能的cell会有不同的尺寸表示不同的驱动能力。我们将为这一族cell建立一个抽象cell,叫做supercell。这个supercell有固定的本征延迟和可变的大小。在对库进行分析时,我们会给supercell的延迟再加上一个可变延迟。可变延迟依赖门的负载。通常库分析得到的可变延迟是每个cell驱动它的完美负载得到的延迟,也叫做理想可变延迟。

supercell库建好之后,利用这个库和RTL代码、设计限制等就可以进行综合了。综合的关键部分就是创建好的逻辑结构。任何设计都有许多种功能正确的电路结构。综合算法的目标是发现最好的电路结构来满足时序目标。时序优化过程就是使每个可变延迟尽可能靠近它的理想可变延迟。

例如一个非常简单的库,仅仅由五个基本逻辑门组成:反向器、两输入的AND、NAND、OR和NOR门。让我们进一步假设反向器有8个版本,而其它的门有4个版本,不同的版本表示不同的尺寸,能提供不同的驱动能力。现在我们考虑一个简单功能的RTL表示,例如w=!((!x+y)Z)。这个功能可以用不同的逻辑门拓扑结构来实现,如图2所示的三种结构。

利用supercell代替库中的门,gain-based的综合只需要快速评估a、b、c三个结构,gain等于1的结构就能提供最好的时序解决方案,而传统的方法对于电路a就有128种选择。因此gain-based的综合时间将大大减少,并且非常简单,比传统的综合方法有更大的处理容量。

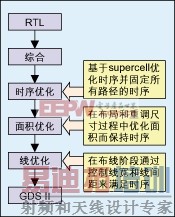

延迟计算就是利用上一节的gain-based的方法。基于supercell,时序优化设计完成之后,然后固定时序,使得接下来的布局布线与逻辑综合操作在同一平面内。

综合之后,设计进入到size-driven布局、load-driven布线阶段。这个时候是supercell真正表演的时候。首先利用supercell来布局,同时确保指定的时序保持常数。必要的时候插入buffer,并且时钟、电源布线开始。线的负载是基于网的全局布线结构来决定。基于每个supercell看到的实际负载,动态调整supercell的大小来满足时序预算。supercell的大小调整好之后,就把supercell用库中有适当驱动能力的cell来代替。这里关键的一点就是最小可能大小的门被选取来满足时序预算。结果芯片不再臃肿。因而会减少空间竞争,减少功耗和信号完整性问题。

最后利用详细的布线工具来调整线宽和线的间距,以保持原始的时序预算,并且确保信号完整。当然,在整个物理综合过程中,我们也会利用DRC、ERC、LVS等工具来验证各个阶段的版图,也会利用参数提取工具在各个阶段来提取参数,为supercell的大小调整以及supercell的gain调整提供信息。

利用supercell技术,从RTL到GDSⅡ的实现的几个主要步骤见图3。

这就是基于Logical Effort理论的新设计方法,特别适合于设计快速的CMOS电路。在这里我们只简单描述了它的设计思想。由于只是初步研究,肯定会有很多错误和问题,欢迎大家指出并讨论。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...