- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种改进的对抗软错误电路结构设计

摘要:给出了一种改进的基于时钟沿的自我检测和纠正的电路结构,以纠正由单粒子翻转(SEU)引起的数据错误。简单概述了已有的检测和纠正SEU的电路结构,并在该电路的基础上提出了改进的电路结构.以实现对触发器以及SRAM等存储器的实时监控,并可以及时纠正其由于SEU引起的数据错误。采用内建命令进行错误注入模拟单粒子翻转对电路的影响。改进的电路与原来的电路相比,以微小的面积和较少的资源换取更高的纠错率。

关键词:SEU;检测和纠正;时钟沿;FPGA;触发器

0 引言

在一些电磁环境比较恶劣的情况下,一些大规模集成电路常常会受到干扰,导致不能正常工作,特别是储存单元,使原来存储的“0”变为“1”,或者“1”变为“0”,即单粒子翻转效应(SEU)。随着集成电路的发展,超大规模集成电路(VLSI)是必然的发展趋势。但是,单粒子翻转效应已经严重影响了VLSI的发展。

由于单粒子翻转对电路稳定性的影响,新的电路设计结构必须减少其对电路稳定性的影响。在这些新提出的电路结构中,比较常用的检查和纠正单粒子翻转的方法是三模冗余(TMR)和软件错误检测和纠正电路。三模冗余是解决SEU影响的最有效方式,其设计原理是将要保护的电路复制成完全相同的三份,同时运行这三部分电路,并且对该三部分电路的运行结果进行大数表决,表决出一个置信度高的结果输出,同时检测出那个冗余逻辑块翻转并进行修复。但它的最大缺点是需要消耗大量的资源,才能实现该电路结构。软件错误检测和纠正电路的原理是根据不同的编解码方式,实现对所存储数据进行检测和纠正。最常用的海明码方式,其设计原理是在存储的数据源码中加入一些冗余码,使这些数据源码和数据源码之间建立一定的关系,一旦数据源码或是冗余码出现某种错误时,数据码和冗余码之间的关系被破坏,就形成非法编码。接收端可以通过检测数据码和冗余码来检测数据码的正确性,并对检测出来的错误数据源码进行修改。

近来,一种基于时钟沿来检测和纠正单粒子翻转的电路结构,实现了检测单元占用更小的面积,使用更少的逻辑单元,实现相近的检测和纠正率。本文在基于该文提出的检测和纠错原理的基础上,提出了一种新的可以多次检测和纠正单粒子翻转的电路结构。

1 时钟沿检测和纠错电路原理

1.1 时钟沿产生原理

基于时钟沿的检测和纠正电路原理可知,对于触发器来说,只有在时钟上升沿的时候,输出数据发生转变才是有效的正确数据,而其他任何时刻的变化都是由于外界原因引起的信号错误(本文主要是针对SEU引起的错误)。该电路结构就是基于上述原理,通过对比数据与时钟的转变沿来对数据进行检测和纠正的,其过程可描述为时钟沿经过3个非门的延时,产生信号not_clk,该信号和时钟信号相与产生1个上升沿脉冲。

1.2 错误检测和纠正电路

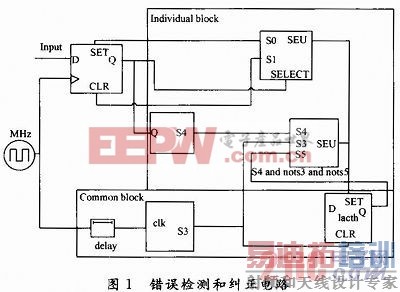

另外一个需要解决的重要问题就是错误的检测和纠正。首先,该文信号的错误检测原理图如图1所示。时钟产生的脉冲与数据翻转产生的脉冲进行比较。比较单元的核心部分可由如下表达式表述:

SEU_O=Data_pulse×Clk_pulse’ (1)

式中:Data_pulse是数据信号经过沿检测电路后的信号;Clk_pulse是时钟信号经过沿检测电路后的信号。在时钟上升沿时,Clk_pulse会产生一个正向脉冲,如果此时数据发生翻转,Data_pulse也会产生一个正相脉冲,SEU_O将保持0不变,当SEU影响,使数据发生翻转时,Data_pulse会产生一个脉冲,而此时由于不是在时钟上升沿,信号Clk_pulse将保持为1,此时的输出信号SEU_O就被置为1。由上述分析可知,当没有SEU错误发生时SEU_O为0;当发生SEU错误时SEU_O为1;

该文的错误纠正电路原理如图1所示,该部分电路的核心是运用一个多路输出选择器来纠正触发器的错误输出信号。多路输出选择器的输入信号为SEU_O,输出选择信号为触发器的输出信号,两个输出信号分别连接到触发器的复位端和清零端。

由上面的分析可知,检测到有错误发生时,SEU_O的值为1。此时,如果Q值为1(正确值应该为0),那么就把SEU_O的值1赋给S1,触发器被清零,Q被置为0;如果Q值为0(正确值应该为1),那么把SEU_O的值1赋给S0,触发器被置1,Q被置为1,从而实现对Q值的纠正;如果没有错误发生时,SEU_O的值为0,此时不论触发器的输出信号Q为1或0,都不会对Q值产生影响。

为了避免检测电路把纠正之后的Q值作为SEU引起的错误值来进行处理和纠正,该电路添加了一个触发器,用以锁存以前的电路状态,如图1所示。信号SEU_O与信号S3,S4,S5有关,可以由下述表达式表示:

SEU_O=S4×S3’×S5’ (2)

由原理图可知,每一个时钟上升沿到来时就会对触发器清零,电路可以对数据进行检测和纠正。若在一个时钟周期内,第1次发生单粒子翻转并被检测到SEU_O由0变为1,同时触发器被置1,进而SEU_O的值又变为0,纠正后的数据产生数据沿脉冲不会对SEU_O的值产生影响,从而完成这一次的数据检测和纠正。[p]

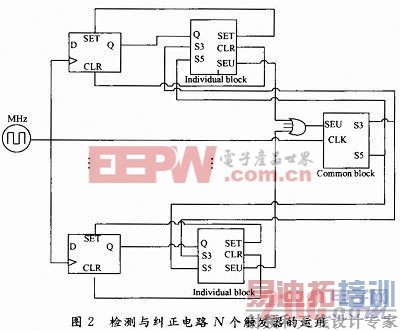

上述基于时钟沿检测和纠正电路是针对一个触发器的情况,但是一个系统设计必定会包含多个触发器。如图2所示为该电路结构应用到多个触发器的原理图。电路结构可以分为独立模块和公用模块两个部分。时钟是整个电路系统公用的部分,所以时钟沿单元是可以公用的。此外,锁存器是存储前一个时刻的电路状态,所以也是可以作为公用单元使用的。

N个单独模块产生的错误检测信号SEU_O,通过N位的或门输入给公共模块,进而对电路中N能发器的输出进行修改。由图2可知,任何一个触发器检测出有SEU错误产生,该触发器的单独模块输出信号SEU_O变为1,那么公共模块的输入信号SEU变为1,进而通过各个模块的S5信号对状态进行保存,使其对改变后的值不进行错误处理。

2 多次检测单粒子翻转的电路结构

由第一节可知,该方案虽然可以以较小的面积和使用较少的逻辑器件实现单粒子翻转的检测和纠正。但是它存在两个问题,第一个问题是对于数据转变沿的检测只可以检测0到1的转变,不可以检测到1到0的转变,以至于对由于SEU引起的由1变为0的数据错误翻转无法检测,影响电路系统的稳定行;第二个问题是该电路结构设计的假设条件,每1个时钟周期只发生1次单粒子翻转引起的数据错误。由图2可知,当一个时钟上升沿来临,锁存器的输出Q被清零,SEU_O的值只与数据沿和时钟沿有关。当任何一个触发器的输出由于受到SEU的影响发生翻转时,通过各个独立模块的错误检测电路,检测出有错误发生。此时,该独立模块的SEU_O变为1,并对该模块中的触发器输出进行纠正。同时,公共模块的锁存器被置为1,由前面的式(2)可知。SEU_O变为0,并且与S3和S4无关,直到下一个时钟上升沿到来时,锁存器才被再次置为0,才会随着S3和S4发生变化。由上述分析可知,该电路结构在一个时钟周期内只可以检测和纠正一次单粒子翻转引起的数据输出错误。

在只有一位触发器的情况下,电路在每一个时钟最多发生一次翻转的假设是可以接受的。但是,随着现在电路规模和功能要求的增加,这将限制电路对数据的检测和纠正,严重影响电路系统的可靠性。

2.1 数据沿的产生

针对第一个问题,本文对数据转变沿的检测采用下述结构。该电路结构采用2个非门和1个异或门。利用两个非门来产生延时,异或门对延时后的信号和原来的信号进行比较,进而在上升沿和下降沿时产生一个脉冲,用于数据沿的检测。

2.2 多次检测和纠正错误数据电路

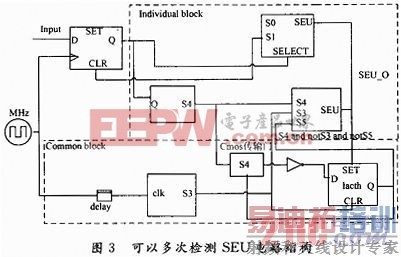

针对第二个问题,本文添加了少量的逻辑电路,以实现对由SEU引起的错误数据的多次检测和纠正。原理图如图3所示,与参考文献提出的电路原理相比,该电路结构只是在公共模块上增加了1个非门和1个CMOS传输门,用于检测数据修改是否完成,并对锁存器赋值,使电路在数据纠正完成以后,让锁存器输出变为0,即恢复到没:有检测到错误发生的状态。该电路可以对下一个由SEU引起的数据翻转进行检测和纠正,进而大大提高电路的稳定性和可靠性。

电路原理:当时钟处于上升沿时,信号S3产生一个高脉冲,此时锁存器被清零。锁存器输出0时,CMOS传输门被关闭,不传输数据。当检测到由于SEU引起的Q值翻转时,SEU_O变为1,此时锁存器被置为1。当SEU_O变为1时,对数据Q进行纠正,Q值发生翻转,会产生一个高脉冲。当锁存器被置为1时,CMOS传输门导通,SEU_O又变为0。数据Q被纠正,发生翻转产生1个高脉冲,此时CMOS传输门被导通。数据Q产生的脉冲经过传输门和非门,变为低脉冲,该脉冲传输到锁存器的输入端,进而锁存器的输出变为0。此时,CMOS传输门关闭,信号SEU_O只与S4和S3有关,电路的错误检测和纠正电路恢复到没有发生错误时的状态,准备检测下一个数据沿。[p]

由上述分析可知,该电路可以实现电路对多个SEU引起的数据错误翻转进行检测和纠正,从而提高电路的可靠性。

如图3所示,该电路分为两个部分,上虚框内是每一个数据单独具有的错误检测和修改部分;下虚框内是该电路的公用部分。

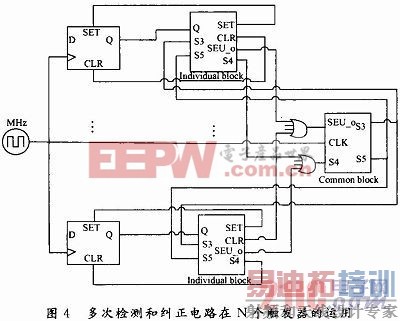

该电路结构运用到N位触发器的原理框图如图4所示。与原来的设计类似,该电路结构有N个独立模块和一个公用模块。由图可知,每个单独模块输出的信号SEU_O通过一个N输入或门,得出的逻辑值传输给公共模块的SEU信号,以控制各个单独模块的数据纠正。当检测到SEU发生后,触发器的输出变为1,CMOS传输门被导通。

此时,各个单独模块的信号S4通过一个N输入或门,得出的逻辑值传输给公共模块,以改变锁存器的输出,进而各个模块的信号SEU_O也只与各个模块的数据沿和时钟沿有关,回到了错误检测和纠正的准备状态。从而达到多次检验和纠正SEU引起的错误数据翻转。

3 仿真结果

为验证多次检测和纠正电路的可靠性,使用仿真器的内建命令进行了错误注入,运用TB文件对输入数据进行控制,以模拟真实情况下的SEU。在不是信号上升沿的时候,使触发器中输出信号Q发生翻转,模拟SEU引起的错误输出,通过观察信号Q的值,进行检验电路的检测和修改功能。

图5是基于上述电路结构和错误注入的仿真结果。从图中可以看出,随着触发器的输出信号Q的变化,检测和纠正电路的工作状态。在左侧椭圆标示的位置,是正确的数据翻转。此时产生了数据脉冲和时钟脉冲,检测信号SEU_O和锁存器的输出(LATCH)没有发生变化,保持0的状态;在右侧椭圆标示的位置可以看出,是错误的数据翻转引起Q变为0。

此时,检测电路检测出其为错误的数据翻转,信号SEU_O由0变为1,锁存器输出信号变为1,CMOS传输门导通。当信号SEU_O为1时,纠正电路对Q值进行纠正,Q值恢复为正确值,与此同时,信号S4(即Q_pulse)产生一个正脉冲。由于CMOS传输门此时导通,所以信号S4经过一个CMOS传输门和一个非门传输给锁存器,锁存器的输出信号变为0,CMOS传输门关闭。由于在SEU_O信号由0变为1时,锁存器被置为1。此时,信号SEU_O变为0,信号SEU_O和锁存器的输出(LATCH)恢复错误纠正前的状态。由上述分析可知,信号SEU_O跳变为1的时间间隔很短,如图5所示。

4 结语

本文提出的电路结构可以实现对SEU引起的数据错误翻转进行多次检测和纠正,完善了参考文献所述电路结构,打破了该电路的1个时钟只可以纠正1次SEU引起错误的局限性。在提高电路结构的检测和纠正能力的同时,本文提出的电路结构只是增加了极少的资源消耗。为了更好地检测SEU引起的错误翻转,在每个单独模块中只由原来的与门替换为异或门;为了实现对电路错误翻转的多次检测,仅在电路的公共模块上增加了一个N输入或门,即整个电路只是增加了一个或门。因此,仅占用较少的面积和资源,就能对触发器的错误翻转进行实时监控。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:同一组合内模块电源和线性电源的电磁兼容性的主要

下一篇:某探测系统的电磁兼容性分析