- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Xilinx-Spartan6 FPGA的MultiBoot设计的实现

摘要 介绍了Multibool的两种实现方法。通过Xilinx Spartan-6 FPGA的Multiboot特性,允许用户一次将多个配置文件下载入Flash中,根据不同时刻的需求,在不掉电重启的情况下,从中选择一个来重配置FPGA,实现不同功能,提高器件利用率,增加系统安全性,降低系统成本。

关键词 MultiBoot;Fallback;重配置

Xilinx公司出品的Spartan6系列FPGA所具有的MultiBoot特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,有选择地从存储于Flash中的多个配置文件中加载其中的一个,对FPCA在系统重配置,实现不同的功能。MultiBoot特性使得用户可以在某些场合选择较少逻辑资源的Xilinx FPGA,实现需要较大逻辑资源且较昂贵的FPGA或ASIC才能实现的功能,从而提高器件利用率及系统安全性、降低系统成本。

1 基本概念

Spartan-6 FPGA在上电时从片外Flash加载mcs文件进行配置。根据所包含的bit流文件的个数,mcs文件分为两类:一类是南单bit流文件生成的mcs文件,即该mcs文件中只包含一个bit流文件,用此类mcs文件配置FPGA时,只能实现一种功能;另一类是由多个bit流文件生成的mcs文件,即该mcs文件包含多个bit流文件。用此类mcs文件配置FPGA时,可根据需求有选择地加载其中的某个bit流文件对FPGA进行系统重配置,即MultiBoot特性。

Spartan-6 FPGA拥有专用的MultiBoot逻辑配置模块,来实现MultiBoot和Fallback操作。MultiBoot操作是在各配置bit流文件能正常加载的前提下,通过ICAP设置配置模块中的相关寄存器并触发IPROG命令,实现在不同配置bit流文件中的切换,达到FPGA实现不同功能的目的。Fallback操作是在从配置A切换到配置B的过程中出错时,用另一个比较“安全”的bit流文件代替配置文件B配置FPGA的操作。这个比较“安全”的bit流文件称为Golden。

FPGA的重配置操作,是通过专用的ICAP_SPARTAN6原语向配置模块发送IPROG命令来实现的。重配置操作可由FPGA外部的处理器、微控制器、计算机和按键等“智能”终端触发。在应用设计中,只需在每个应用程序中例化一个ICAP_SPARTAN6原语来实现相关命令序列即可实现MultiBoot特性。

Spartan6的多bit流配置可通过SPIx1,x2,x4及BPI模式实现,文中只介绍基于SPI模式的MultiBoot特性的实现,用配置文件代替应用程序。

2 MultiBoot操作相关寄存器简介

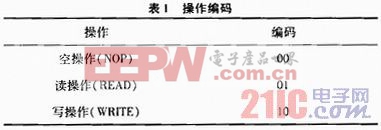

(1)所有Spartan-6 FPGA的bit流控制命令都是通过读写相关配置寄存器实现的。配置数据都是16位宽的字,也有一些数据是多字的,配置数据包含的3个主要命令如表1所示。

(2)所有的操作数据可分为两种:

TYPE1包含两部分:Header,Data。

TYPE2包含3部分:Header,Word Count,Data。

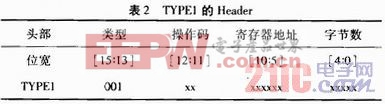

用TPYE1就能实现MultiBoot和Fallback操作,故只介绍TYPE1。TYPE1的Header是个16位字,用其中6位表示相关寄存器的地址,如表2所示。

其中Operation位[12:11]是表1中所列的操作码,寄存器地址[10:5]如表4所示,字节数[4:0]表示操作所需的字节数。

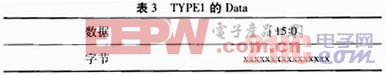

TYPE1的数据部分形式如表3所示。

(3)Spartan-6 FPGA的MultiBoot常用配置寄存器及功能列表如表4所示。

[p]

寄存器功能介绍:

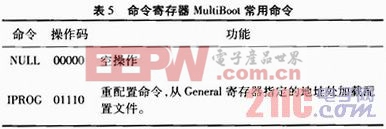

1)命令寄存器CMD。命令寄存器CMD存储配置控制命令,以产生全局信号执行其配置功能。在MultiBoot操作中,常用的CMD命令如表5所示。

2)General寄存器。触发IPROG命令后,General1、General2中存放用于对FPGA进行重配置的下一个bit流文件的地址,其中General1存放地址的低16位,General2的高8位存放SPI操作码,低8位存放地址的高8位。General3、General4存放FMlback时的配置文件地址,其中Gener al3存放低16位地址,General4的高8位存放SPI操作码,低8位存放地址的高8位。General5中存放MultiBoot或Fallback时的用户自定义数据。

3)模式寄存器MODE_REG。MODE_REG模式寄存器主要用于重配置时的一些模式设置,如SPI总线的位宽。模式寄存器中各位的功能如表6所示。MultiBoot和Fallback操作需对[13:8]进行相应设置。

4)控制寄存器CTL、配置选项寄存器COR2。因CRC校验错误也可能触发Fallback操作,因此为安全起见,如果可能发生CRC校验错误,需将CTL寄存器的CRC_EXTSTAT位清零,使能CRC校验,并将COR2寄存器的RESET_ON_ERROR置1,使能CRC错误时的Fallback操作。但如果能确定不发生CRC错误,可不设置这两位。

3 MultiBoot原理

如上所述,Spartan-6 FPGA内置有专用的MultiBoot逻辑控制模块,来实现MultiBoot(IPROG)和Fallback操作。当触发Fallback或IPROG时,片内会产生一个复位脉冲,使片内配置逻辑复位,但不会使专用的MultiBoot逻辑和BOOTSTS、MODE、G1-G5复位。

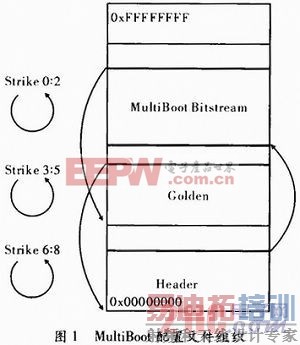

实现MultiBoot特性时,存储器中的配置文件组织模式如图1所示。

如图1所示,第一部分是Header,这个小的bit文件中包含同步字、下一个配置文件的地址以及IPROG命令。此段必须位于Flash存储器中的0地址处。该部分可由命令文件生成。第二部分是MultiBootBitstream,由用户的多个bit流配置文件组成,其地址可在生成mcs文件时指定到符合Flash操作要求的任何地方。进行MultiBoot操作时只需通过ICAP向MuhiBoot逻辑控制模块发送IPROG命令,之后控制模块就会根据Gene ral1、General2指定的地址,加载下一个需要的配置文件。第三部分是Fallback或Golden配置文件,地址可由General3、General4指定。

Header、MultiBoot配置文件、Fallback配置文件在加载过程中,如果出错,FPGA会根据相应寄存器的值,从配置文件的起始地址重新加载3次,加载次数的计数保存在BOOTSTS寄存器的[15:12]位,名称为strike。

Header在加载过程中分配有3个strike计数值:6、7、8。当检测到CRC错误,且RESET_ON_ERROR为1、strike9,则strike计数器加1,并重新开始配置过程。若看门狗计时器超时也会触发相同操作,但此时会忽略RESE_ON_ERROR的状态。若strike等于9,则停止配置,且将INIT和DONE引脚拉低。

MultiBoot配置文件在加载过程也分配有3个strike计数值:0、1、2。当在加载过程检测到错误时,如果strike3且RESET_ON_ERROR为1,则strike计数器加1,且从General1、General2指定的地址处重新加载配置文件。若strike计数器等于3,则触发Fallback操作。

Fallback或Golden配置文件在加载过程也分配有3个计数值:3、4、5。当在加载工程中检测到错误时,若strike计数器值6,则strike计数器加1,并从General3和General4指定的配置文件地址处重新加载配置文件。若strike计数器为6,则从0地址处加载Header配置文件。此时,FPGA会执行循环加载过程:Header→MultiBoot→Fallback(或Golden)→Header,每次循环都会使strike计数器加1,最多3次。若其间某

个配置文件加载成功,则停止循环,否则直到strike计数为9,停止加载过程。Strike计数器只能通过复位或重启系统清零。

Fallback是一种出于安全性考虑的操作。一旦该操作被触发且加载Golden成功,若再想退出Golden加载其他用户配置文件,只能复位FP GA或重启系统。

[p]

4 MultiBoot实现简例

实现MultiBoot操纵有两种方法:(1)基于ICAP的寄存器编程实现。(2)通过在生成bit流文件时,设置相关选项实现。

4.1 基于ICAP的寄存器编程实现

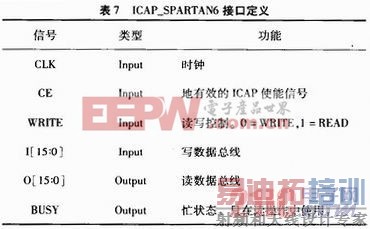

如上所述,通过ICAP_SPARTAN6原语发送IPROG命令,其发送命令序列如下:(1)发送同步字。(2)配置General1-General4,指定相关操作所需配置文件地址及操作码。(3)发送IPROG命令。ICAP_SPARTAN6原语接口定义如表7所示。

在主SPI模式下,ICAP_SPARTAN6的输入数据在从总线I[15:0]输入前,要进行字节范围内的位交换,即16位宽的字分为高8位1 Byte,低8位1 Byte,各字节的最高位[7]和最低位[0]交换,位[6]与位[1]交换,其他以此类推。

通过ICAP触发IPROG的命令序列举例如表8所示。

IPROG命令后需经过一段时间后,FPGA内部才会产生相应的重配置信号,因此在IPROG命令后需跟几个空操作命令,一般为4个。GENERA L2、GENERAL4中的操作码:0x0B、0x3B、0x6B分别为SPIx1、SPIx2、SPIx4。

ICAP逻辑模块是FPGA中的专有逻辑模块,因此在生成bit文件的各源文件中必须都实例化一个ICAP模块。一般情况下对ICAP模块的控制操作通过状态机实现。

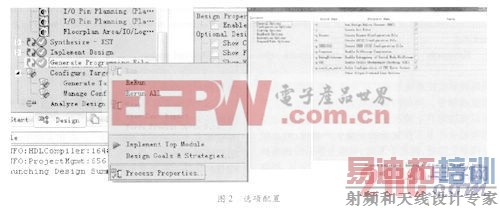

4.2 选项设置实现

实现MultiBoot功能所需配置的所有寄存器,均可在生成bit文件时通过添加相关的生成设置选项实现。在进程菜单中单击Generate Pro gramming File,选择Process Properties,弹出配置窗口如图2所示。

5 结束语

介绍了实现MultiBoot操作的两种方式,一种是基于ICAP的寄存器编码配置方式。可通过源代码中的注释,使后续开发维护人员阅读代码、扩展功能时思路清晰,缺点是需编写大量代码,并需对ICAP的操作与命令序列有一定了解。第二种通过在生成bit文时添加相关设置选项实现,方便简单,但需大量的文本注释,以便后续的开发与维护。当然,实际的应用开发过程中可同时使用这两种方法,实现更高效便捷的编码开发。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:高性能维特比在卫星导航接收机中FPGA实现

下一篇:proteus如何移动整块电路