- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种多通道时钟分频和触发延迟电路的设计

摘要:在EAST分布式中央定时同步系统中,时钟分频和触发延迟电路是分布式节点的核心。为了完成对基准时钟信号进行多路任意整数倍的等占空比的分频,并对输入的触发脉冲进行多路任意时间的延迟输出,本设计中采用VHDL语言进行编程,实现了多路时钟分频信号的输出和多路延迟输出,特别是提高了奇数分频和触发延迟的时间精度,最后在QuartusⅡ9.0软件上时设计的波形进行分析,验证了该设计的可行性。

关键词:EAST;时钟分频;触发延时;FPGA

0 引言

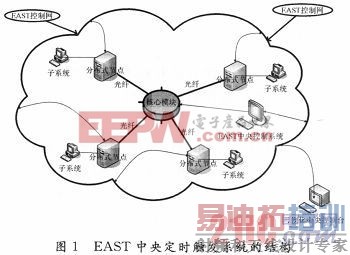

EAST(先进实验超导托卡马克)是我国自行设计研制的国际首个全超导托卡马克装置。中央定时同步系统是EAST托卡马克装置的重要组成部分。EAST中央定时与同步系统为分布广泛的数据采集系统和其它子系统提供精确的方波时钟信号,以及精确的同步触发信号,控制各子系统按照预设的时序流程工作。该系统主要由EAST可视化中央控制台,时序信号光纤网,核心模块,若干个分布式节点以及外围隔离驱动设备组成,见图1。核心模块负责向各分布式节点发送同步的基准系统时钟和系统触发信号。分布式节点根据设置对核心模块发送的基准时钟信号进行分频,得到所需要频率的时钟发送到子系统。通过设置的触发延迟模件参数可以得到子系统所需要的触发时刻。

目前,进行分频电路设计主要采用定时器来实现,8254计数器所支持的最高时钟频率有限(最高为10 MHz)以及误差较大也不是理想的实现方案。可编程逻辑器件FPGA是当今最热门的逻辑开发器件之一,它在工作最高频率、集成度、时序控制能力上具有无与伦比的优势。因此选用FPGA芯片来实现时钟分频和触发延迟电路是当前的主流。在使用FPGA做时钟分频设计时,文献设计计数器的时候用VHDL做了分频器的设计,但是只讨论了偶数的分频;文献在运动控制系统中使用Verilog描述语言在FPGA环境下对通用整数分频器进行了设计,但在通用任意整数分频器中分频系数的设置稍显复杂,不利于分布式中央定时系统,并且主要讨论的都是单路输出;文献在FPGA上实现了奇数和偶数的通用分频器,将半整数,奇数,偶数放在一个模N计数器里进行预置,这样分频系数的设定比较方便,但输出奇数分频时钟信号时的误差过大,达不到分布式定时同步系统的精度。而对触发延迟输出方面,之前这方面的研究主要采用的是模拟电路实现的方法,不易进行远程控制和更改。

本文首先介绍中央定时同步系统的基本组成结构,随后具体给出了时钟分频和触发延迟电路的逻辑设计。利用FPGA芯片来实现对输入基准时钟信号进行多通道任意整数倍的等占空比分频输出,同时对触发脉冲进行任意时刻延迟的多路输出。本设计主要采用VHDL语言来设计,利用QuartusⅡ9.0对设计进行了仿真分析,结果表明该设计满足分布式定时触发系统的分频延迟功能。

1 系统组成

EAST定时与同步系统主要由一个核心模块和多个分布式节点构成,核心模块给分布式节点提供一道基准时钟信号和一道基准触发信号,各分布式节点负责对基准时钟和触发进行分频和延时处理,为子系统系统提供它所需要的时钟和触发。总体系统结构如图1所示。

[p]

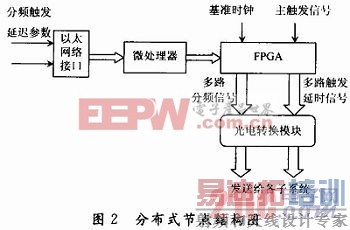

分布式节点是该中央定时触发系统的核心,而时钟分频和触发延迟也是分布式节点最重要的任务。分布式节点主要由微处理器和FPGA组成,外围由以太网络端口,光电转化模块等等组成。微处理器接收核心模块发送的分频系数和延迟参数,FPGA主要根据微处理器传输来的参数对输入的基准时钟进行相应的分频,并对核心模块发送的主触发信号进行延迟输出。时钟同步系统分布式节点结构如图2所示。

2 时钟分频设计

对基准时钟的整数分频主要分为等占空比偶数分频和等占空比奇数分频,它们的分频原理也是不同的,必须要分别对待。对于单通道偶数分频,设计比较简单,之前已经有很多这方面的研究,在此不再赘述。在本设计中,由于EAST定时触发系统需要多路分频信号,可以在程序设计的时候采用VHDL里面的类属参量和元件例化语句,类属参量Generic是一种端口界面常数,常以一种说明的形式放在实体或块结构体前的说明部分。类属参数映射的综合处理较简单,所有的参数配置都通过Generic map来传递,子模块内部只需要根据上层模块指定的参数进行综合即可。整数时钟分频电路需要在一个程序中可以同时对基准时钟进行奇数和偶数分频,所以在顶层文件中需要声明元件的语句格式如下:

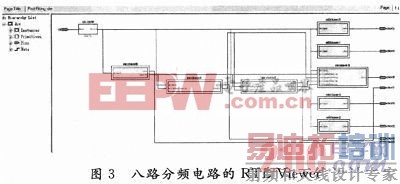

时钟分频设计的RTL Viewer,即在FPGA中所设计的电路原理图如图3所示,所有的计数分频模块都采用同样的基准时钟,以保证每路时序信号能够完全的同步。

[p]

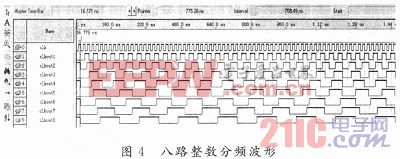

等占空比奇数分频设计所采用的方法是:假设所需要的分频系数为n(n为奇数),首先定义2个buffer类型的信号端口clk1和clk2,在上升沿敏感的情况下,当从0计数到(n-3)/2时,给clk1赋值1;当从(n-3)/2计数到n-1时,给clk1赋值0;同样的,在下降沿敏感的情况下,0到(n-3)/2时给clk2赋值1,(n-3)/2到n-1时给clk2赋值0。由于VHDL语言中process里的语句都是并行执行的,所以再将2路信号相或输出便得到分频数为n的分频信号。为了实现多路的触发延时,和前面所述多路分频电路一样,在顶层文件中做个例化,取各种不同的奇数来验证输出结果。下图4中clkout1~clkout8分别为2,3,4,5,6,7,8,9次分频,可以看到所输出的信号均为同步等占空比的分频信号。更多路、其他分频信号的实现可以稍加修改顶层程序即可。

实验采用50 MHz晶振,时钟周期为20μs。从图4中可以看出每路分频信号均为等占空比,由于偶数和奇数分开进行分频,因此是对奇数分频的输出是很精确的,例如clkout6输出的7分频信号里刚好是7个基准时钟周期。系统中在放电前需要设定分频参数时,只需要发送相应的指令改动顶层文件中的n值即可。

3 触发延迟设计

时钟分频电路是为了使各子系统能够更好的做到时序同步,而触发延迟电路是对子系统进行定时启动和停止各正在运行的子系统。触发延迟模块主要是将输入的原始触发信号按延时参数进行延时输出,为EAST中的数据采集和其它子系统提供精确的同步触发信号。本设计采用VHDL中移位寄存器来实现触发延迟功能。首先定义一个类属参数delay_count,在顶层设计实体中可以设置延迟参数。然后在延迟程序模块的结构体中定义一个移位寄存器trigger_r(delay_count-1 downto 0),其中delay_count代表所要延迟的位数。然后每隔一个时钟让寄存器左移一位,直至将原始触发信号放到寄存器trigger_r的最后一位,最后再把它输出,结果便是延迟了delay_count个单位时钟的触发信号了,该移位寄存器的功能语句如下所示:

4路延迟仿真结果如图5所示。图中每个时钟周期为20 ns,其中,delclk1是延迟10 ns×10=0.1μs的触发信号,delclk2是延迟0.3μs的触发信号,delclk3和delclk4分别是延迟0.9μs和1.2 μs的延迟信号。其他任意时间的延迟都可以这样方便的实现,延迟误差在ns级范围。

4 结语

本文所使用的时钟分频和触发延迟实现简单,充分发挥了FPGA逻辑器件的高集成度、高速、高可靠性和并行处理能力的优势,方便每次放电时设定时钟和触发参数,非常适合EAST分布式中央定时同步系统中分布式节点的设计。在FPGA上的分频延时设计与仿真工作已经完成,接下来的工作就是要把设计文件下载到芯片中,使设计工作赋予实际。结合FPGA的高效性和嵌入式系统的以太网通信功能,便可以实现EAST分布式中央定时同步系统的时钟同步和触发延迟功能,满足EAST分布式节点对各子系统的同步触发的要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:反辐射导弹抗诱骗性测试系统UI设计

下一篇:FPGA设计中常用的低功耗技术