- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

封装行业面临的挑战

随着现代印刷电路板(PCB)、多芯片模块(MCM)、堆叠式片以及硅通孔(TSV)器件上封装器件越来越密集、越来越复杂,遭遇封装器件失效的可能性也越来越明显、越来越成问题。

失效分析工程师一直在不断地设法优化工具、算法和电路编辑的效率以提高良率。SystemNav™是微捷码设计自动化有限公司专为设计师和失效分析工程师提供的一款新工具,它可彻底隔离造成封装器件失效或性能降低的源头。其中部分是通过让用户从片到系统层并从系统层到片地快速追踪信号,实施故障隔离和修复;追踪到信号后再让工程师从物理上将失效分析工具导航到X、Y位置,确认失效的根源从而实现。

传统上,封装器件是由金属引线框架和通过绑定线与金属引线框架固定的裸片所组成。这项技术现已非常成熟且失效机制也广泛被接受。随着一个器件中包含100多个连接以及一个系统包含多个器件这些状情况的接连出现,封装器件需要进行重大改变才可满足目前封装技术需求。半导体器件可直接贴装在PCB上,完全替代引线架构封装。许多的PCB也可贴装到传统引线框架封装中,此项技术即是众所周知“介入物(interposition)”。

由于这类封装密度大、复杂性高,因此制造商主要负责最后封装产品的质量和良率;这就需要质量保障(QA)团队与失效分析(FA)团队紧密协作,对封装产品上多个器件加以分析。

封装器件随着尺寸发展, IC失效分析算法和工具变得尤为重要。除了多个堆叠式片和硅通孔(TSV)器件以外,多PCB层中的嵌入式被动元件又将QAFA复杂性和挑战提到了一个新的高度。目前,标准的封装一般都超过1,000个连接。所有上述提及的技术变化给FA工艺带来了新的挑战。

微捷码进一步扩展了Camelot™基于IC的CAD导航工具的功能,加入了IC失效分析功能以进行封装器件失效分析,加入了电路编辑功能以实现与芯片和PC板的系统级无缝导航和CAD支持的故障定位。它可从电路板到芯片或从芯片到芯片地追踪电信号;追踪各类连接,比如:倒装芯片贴装、线焊(wire bond)和TSV;它可将内嵌缺陷图和热像图叠加到版图数据上;通过3D横截面分析和电路图交叉映射等附加功能,还能够实现小区域内多个层面可视化。此外,它还可通过叠加内嵌图像到电气痕迹上、交叉映射电路原理图到版图上以隔离并研究故障机制,再传达给故障分析(FA)工具以实现精确的CAD导航。

就职于半导体公司的失效分析团队主要负责最终封装工作,即在PCB上贴装一个或多个硅芯片。分析装置上CAD支持的导航是CAD数据查看和基于CAD分析的“实际”标准。CAD导航技术范围现已得到了进一步扩展,不仅分析芯片,而且芯片贴装所在的PCB也在其分析范围内。

STMicroelectronics 公司的Quentin Saulnier强调说:“随着芯片功能越来越多、芯片空间越来越窄,封装方面多芯片模块和系统的引入让我们一直不断地面临新的挑战。这些新挑战来源自封装内的片与专属堆叠式片之间的互连。尽管如此,我们仍不得不引入更多这类技术以完善封装,微捷码的SystemNav正是一款能够解决上述所有问题的工具。这也就是为何我们已着手评估SystemNav是否可行的原因所在。”

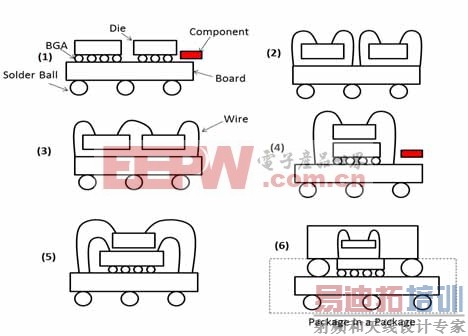

多芯片模块/PCB可按以下配置进行设计:

(1) 板上多个片(BGA)

(2) 板上多个 片(线焊)

(3) 片与片连接

(4, 5) 堆叠式片(线焊/BGA)

(6)系统化封装

下图描述了PCB内层的一个并行面,图中显示一个裂缝已贯穿了所有这些铜痕迹。采用SystemNav,用户在此图上隔离、调整并叠加此层面;接着再通过与客户配置接口(聚焦离子速)沟通,实施必要的电路重新编辑以修复故障。[p]

显示有裂缝的 PCB内层并行面。

来源:Sem Lab公司

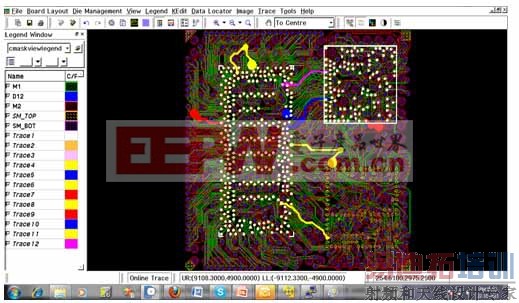

PC板的CAD视图

上图显示了一个PCB版图的图型用户界面(GUI)。白色节点代表了位于电路板上片的PAD层连接。红色、黄色、粉红色和蓝色信号代表的则是所选定的网路痕迹。需注意的是,粉红和蓝色痕迹代表的是位于相同电路板上两个片间连接。

正如本文所强调的,封装器件上失效情况正日益普及,失效分析 工程师正寻找一种可优化其工具效率以提高良率的方法。微捷码的SystemNav可彻底隔离造成封装器件失效或性能降低的源头。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:智能咖啡壶系统

下一篇:FPGA一体化高级设计方法