- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高精度相位差测量算法实现

摘要:首先介绍了两种高精度相位差测量算法,一种是基于直接数字频率合成(DDS)的相关测量法,另一种是基于快速傅里叶变换(FFT)的FFT测量法。其次,通过理论仿真分析两种算法在不同信噪比和数据长度下的性能,并在此基础上给出了硬件平台的设计方案。最后,基于高性能的FPGA芯片XC5SX95T,搭建了硬件实验平台,完成了两种相位差测量算法的硬件实现。经过实测,该硬件平台能够达到良好的相位差测量精度。

关键词:相位差;相关;FFT;FPGA

0 引言

两个同频信号的相位差测量在工程上有着广泛的应用。近年来,精密测量、雷达定位、目标识别等领域的高速发展对相位差测量精度和速度都提出了很高的要求。目前,理论上比较成熟的相位差测量算法主要利用相关原理和快速傅里叶变换(FFT)原理。但由于硬件环境的复杂性和不稳定性,传统硬件测量的精度往往大大低于软件计算精度,而高性能FPGA芯片的发展为硬件提高相位差测量算法的精度提供了新的方向。

本文首先介绍了两种相位差测量算法,一种是基于直接数字频率合成(DDS)的相关测量法,另一种是基于快速傅里叶变换的FFT测量法。在软件仿真的基础上,利用高性能的FPGA芯片搭建硬件实验平台,完成了两种算法的硬件实现。

1 算法原理和理论仿真

1.1 相关测量法

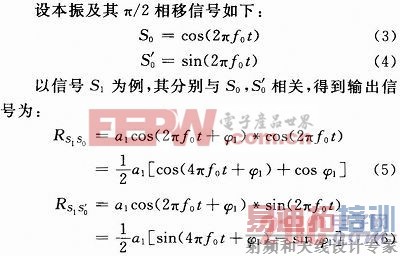

首先在接收端利用本振信号与接收信号进行相关,再经过数字低通滤波器滤除高频分量,分别得到两路接收信号的相位信息,最后相减得到相位差。由于噪声与本振信号相关性很小,所以能够很好地加以抑制。设被测信号为:

![]()

式中:f0为被测信号频率;φ1,φ2分别为两路信号的相位。两路信号的相位差△φ=φ1-φ2,即为所求。

式中,a1为相关后输出信号的幅度,由于两路本振信号的幅度一致,故相关后输出信号的幅度也可认为相等,通过低通滤波器滤除高频分量后可得: [p]

[p]

1.2 FFT测量法

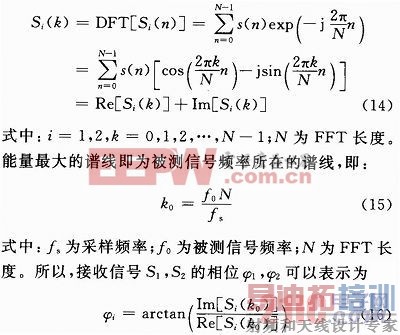

假设两路接收信号同式(1),式(2)所示,则信号Si(n)(i=1,2)在经过FFT之后得到离散频谱Si(k),其频率所在点的谱线的实部和虚部分别包含了信号相位的余弦信息和正弦信息。基于快速傅里叶变换的FFT测量法正是利用这两项信息分别求得两路被测信号的相位值,最后相减得到相位差。由于噪声是宽带的,在被测信号频率点处的噪声干扰影响并不大,不会产生很大干扰。FFT是离散傅里叶变换(DFT)的快速算法,根据DFT的原理:

式中:i=1,2;k0可通过在FFT频谱上搜索最大值的方法确定。最后将两路被测信号的相位差值相减即可得到相位差△φ:

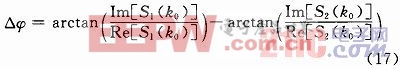

1.3 理论仿真

在PC环境下用Matlab软件仿真两种相位差测量算法的性能,分别就以下两种情况进行性能仿真:一是白噪声干扰条件下,二是不同数据长度N条件下,这两项指标分别决定了测量算法的高精度和实时性。假设两信号的相位差△φ为30°,被测信号频率f0为1 MHz,数字采样频率fs为8MHz。

仿真结果如图1所示,其中图1(a)是在不同信噪比白噪声干扰条件下两种测量法的仿真结果比较;图1(b)是在不同数据长度N条件下两种测量法的仿真结果比较。

仿真结果表明,在较低信噪比高斯白噪声干扰条件下,FFT测量法对白噪声的抑制能力要强于相关测量法,在高信噪比时两种算法均可达到较高测量精度,其性能也趋于一致。在不同信号数据长度N条件下,相关测量法的精度随着N的增加而提高,FFT测量法在N等于2的整数次幂的时候,其测量精度要高于相关测量法,在N不等于2的整数次幂的时候会发生由数据截断引起的频谱泄漏,使其性能变差,这是因为要与硬件实现相统一,对所有数据长度均作2的整数次幂的FFT运算,所以在硬件实现的时候,FFT长度N应该控制在2的整数次幂。

[p]

2 硬件实现

2.1 系统构建

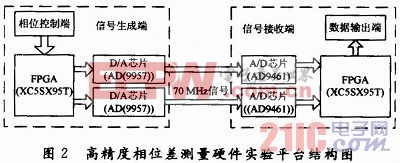

如图2所示,本实验平台由信号生成端和信号接收端两部分组成。信号生成端由一块FPGA芯片控制两块数模转换(D/A)芯片生成两路相位不同的中频信号,其中两路信号的相位差由相位控制端进行实时控制。信号接收端使用两块模数转换(A/D)芯片分别接收两路中频信号后传至FPGA芯片进行相位差的测量,测量得到的相位差由数据输出端实时输出。信号生成端与信号接收端之间用导线连接。

本平台使用的FPGA芯片是Xilinx公司的Virtex-5系列的XC5SX95T芯片;D/A芯片使用AD公司的AD9957芯片,A/D芯片采用AD公司的AD94 61芯片;数据输出端使用ChipScope在线调试软件。中频信号频率设定为70 MHz。A/D芯片采样频率为32 MHz,则根据带通采样定律,输入接收端FPGA芯片的数字信号的频率分量主要有38 MHz和6 MHz。本实验就是利用6 MHz的频率分量进行相位差测量的。

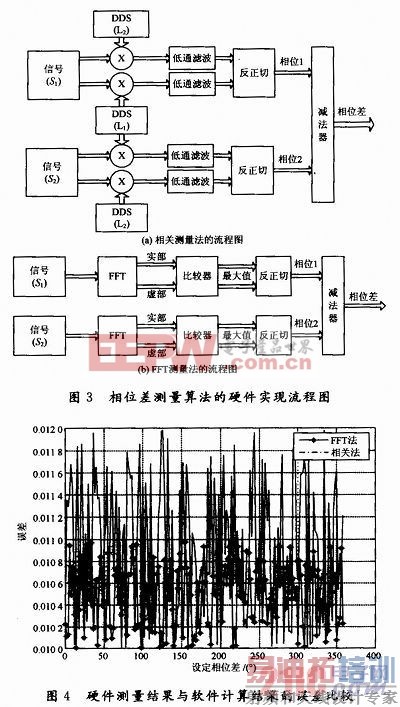

相关测量法和FFT测量法在FPGA内部的硬件实现流程图如图3所示,其中图3(a)是相关测量法的硬件实现流程图,图3(b)是FFT测量法的硬件实现流程图。

Xilinx公司为硬件工程师提供了大量预先设计好、经过严格测试和优化过的电路功能模块(IP Core),这大大降低了硬件设计的繁琐程度。本实验中相位差算法的硬件实现就充分运用了这一优势。图3硬件实现流程图中的DDS模块、低通滤波器模块和FFT模块都可以通过调用IP Core来实现,而反正切模块可以通过调用坐标旋转数字计算(CORDIC)模块来实现。

2.2 测量结果

在硬件实现过程中,为了防止频率泄漏,固定数据长度和FFT变换长度N为2 048。为了比较硬件测量结果与软件计算结果的性能,将经过A/D芯片接收的数字信号导出至Matlab软件进行理论相位差值计算,所得到的结果与ChipSeope显示的硬件测量相位差值结果进行比较。图4显示了在发射端相位差一定的条件下,两种算法各自的硬件测量结果与理论计算结果的误差曲线。

实验结果表明,FFT测量法的精度比相关测量法的精度要稍微高,无论是FFT测量法还是相关测量法,硬件测试的结果与理论计算的结果非常接近,误差很小。该硬件实验平台可实现中频信号的高精度相位差测量。

3 结论

首先对比了相关法和FFT法这两种相位差测量算法的性能,得出FFT测量法对白噪声的抑制能力要强于相关测量法,在高信噪比时两种算法均可达到较高测量精度。通过对不同数据长度的信号进行仿真分析,得出为了防止硬件实现上频谱泄漏造成的FFT测量法性能的下降,需要在硬件实现的时候控制信号数据长度N为2的整数次幂。然后,在基于高性能的FPGA芯片XC5SX95T的基础上,搭建了硬件实验平台,通过硬件实测,得出对于中频信号两种算法硬件实测结果与理论仿真结果之间的误差很小,都具有很高的精度。该实验平台可实现高精度的相位差测量,在工程应用中,可以根据信号的特点以及工程的实际需求选择运用这两种方法。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:机房地线引起的干扰及其抑制方法

下一篇:智能咖啡壶系统