- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PowerPCB信号完整性分析设计

信号完整性问题是高速PCB设计者必需面对的问题。阻抗匹配、合理端接、正确拓扑结构解决信号完整性问题的关键。传输线上信号的传输速度是有限的,信号线的布线长度产生的信号传输延时会对信号的时序关系产生影响,所以PCB上的高速信号的长度以及延时要仔细计算和分析。

运用信号完整性分析工具进行布线前后的仿真对于保证信号完整性和缩短设计周期是非常必要的。在PCB板子已焊接加工完毕后才发现信号质量问题和时序问题,是经费和产品研制时间的浪费。

1.1板上高速信号分析

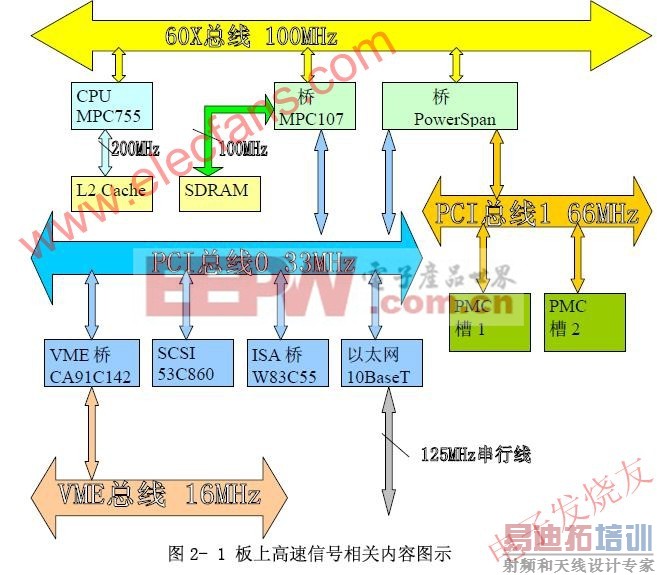

我们设计的是基于PowerPCB的主板,主要由处理器MPC755、北桥MPC107、北桥PowerSpanII、VME桥CA91C142B等一些电路组成,上面的高速信号如图2-1所示。

板上高速信号主要包括:时钟信号、60X总线信号、L2Cache接口信号、Memory接口信号、PCI总线0信号、PCI总线1信号、VME总线信号。这些信号的布线需要特别注意。

由于高速信号较多,布线前后对信号进行了仿真分析,仿真工具采用Mentor公司的HyperLynx7.1仿真软件,它可以进行布线前仿真和布线后仿真。

1.2印制板信号完整性整体设计

1.2.1层叠结构

在传输线(PCB走线)中的磁力线是沿逆时针方向的,如果把RF返回路径与对应的源路径平行并且与其靠近,在返回路径中的磁力线(延逆时针方向的场),相对于源路径中的磁力线(顺时针方向的场),将是相反的方向。这样顺时针场和逆时针场可以抵消。如果源和返回路径之间的磁力线被消除或减小,那么除了在走线附近极小的面积,辐射或传导的RF电流就不存在了。多层印制板可以实现通量最小化,这是采用多层电路板的原因之一。信号层靠近参考层,信号返回路径直接位于信号线的下方,回路面积最小,通量抵消最明显。

为了实现通量最小化,必须实现PCB板上信号层和参考层交错排列,这样,每个信号层都有相邻的参考层。考虑到本板上的芯片数多,特别密集,而且电气网络也特别多,所以采用多少层的PCB要仔细安排,多了或少了都不好:如果层数太少,布线将变得很困难,甚至可能完不成布线。当然在布线过程中如果感觉布线空间不够,可以再增加层数,但加层后要对已完成的布线做许多调整,重新安排一些走线规则,这将增加许多工作量。

如果层数太多,加工成本增加,板子厚度可能失控。目前4层板的板费为0.5元/平方厘米左右,而六层板的板费为1.5元/平方厘米左右。印制板层数每增加两层,板费要增加好几倍。按VME64总线标准,印制板厚度应为1.6±0.2mm,即63±8mil,目前国内的印制板设备,采用的板芯一般最薄的为5mil厚,铜层厚度有0.5盎司、1.0盎司、1.5盎司等规格,如果层数太多,印制板厚度无法满足要求。

1.2.2阻抗考虑

PCI2.2规范要求PCB上的信号线在未焊接器件之前的特征阻抗为60Ω-

100Ω,VME64规范要求PCB上的信号线在未焊接器件之前的特征阻抗为50Ω-60Ω。按目前的集成电路生产工艺,50Ω-100Ω的阻抗是比较合适的,不同的信号有一些差别。现在比较好的PCB加工设备,能加工线宽4mil、间距4mil的印制线。根据阻抗要求和目前PCB加工设备现状,信号线基本采用5mil线宽和5mil间距,对有些信号线的阻抗,如果层间距和印制板基材介电常数调整无法满足要求,可以采用4mil的信号线布线。

1.2.3传输速度

PCI2.2规范要求PCB上的信号线在无负载时的传输速度为150ps/inch-190ps/inch。PCB上的信号线在无负载情况下的传输速度只与介质材料的介电常数相关,所以选取介质材料的介电常数时除了考虑它对印制线特征阻抗的影响外,还应考虑它对印制线传输速度的影响。

1.2.4整板层叠及阻抗设计

综合以上三点,最后采用12层印制板,其中8个信号层(包括元件层),两个地层,一个3.3V电源层,一个混合电源层(包括5V、2V、两个2.5V)。用HyperLynx软件优化出来的PCB层叠结构如图2-2所示,总厚度为65.7mil,即1.67mm,满足VME64规范要求。

[p]

[p]1.3时钟信号阻抗匹配

时钟信号是各设备工作的基础,所以时钟信号的质量尤为重要,在PCB设计时要慎重对待。

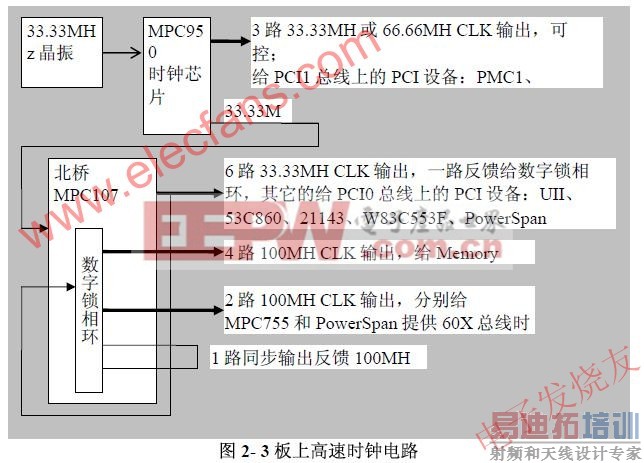

板上时钟信号很多,主要高速时钟信号如图2-3所示。

时钟芯片的输出信号阻抗一般都比较小。芯片MPC950的输出阻抗为7ohm,芯片AV9155的输出阻抗为10ohm。本板上的时钟信号都是点对点连接,所以采用串行端接进行阻抗匹配电路设计。

具体串连电阻的大小由HyperLynx仿真后决定。

1.4L2Cache总线和60x总线信号完整性分析

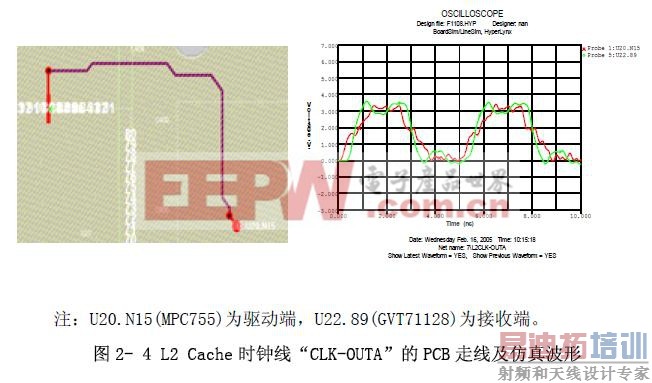

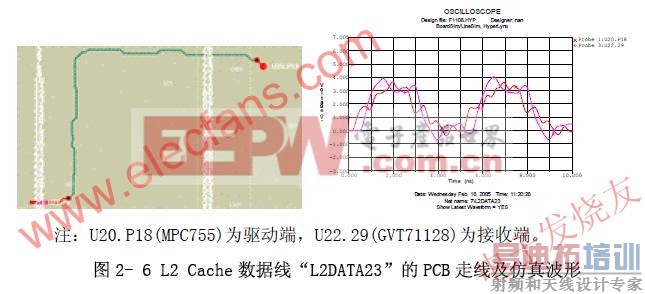

本板的L2Cache总线工作频率200Mhz,60x总线工作频率100MHz,是板上工作频率最高的部分。依据MPC755、MPC107、PowerSpan的芯片手册,阻抗在50ohm~70ohm之内比较合适,按前面层叠结构的设计,5mil的信号线宽是可以保证阻抗要求的。

因为板上这两个总线的负载最多为2个负载,且这几个芯片之间的距离很近,相关的PCB走线很短,所以信号时序关系一般能够满足要求(尽管其工作频率很高)。下面给出L2Cache总线上典型时钟线、地址线以及数据线的PCB走线图以及在HyperLynx仿真软件的BoardSim工具下的仿真波形。MPC755、MPC107、PowerSpan和GVT71128芯片的IBIS模型均来自于芯片厂商(Motorola、TUNDRA和GALVENTECH)。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:PCB模拟和数字布线设计的异同分析

下一篇:des算法原理