- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于DSP及FPGA的水下目标定位系统数字信号处理模块

随着水下武器和水下航行器等水下目标的快速发展,对其进行定位和跟踪从而检验其性能的试验具有非常重要的意义,这也是水下目标试验场的重要工作内容。水下试验场的定位系统根据被测目标是否加装合作声信标,可以分为主动和被动两种方式。主动定位方式需要在水下目标上加装声信标,定位系统整个试验系统的同步时序控制下,通过接收及处理水下目标声信标发射的已知脉冲信号来实现目标的定位及跟踪;被动方式则仅通过接收及处理水下目标运动产生的辐射噪声,实现水下目标的定位及跟踪。对于水下目标定位系统的信号处理模块而言,两种定位方式的差异在于因系统的接收信号频率及信号体制不同而导致的系统硬件规模和处理性能不同。

1 系统的硬件设计

对于主动定位系统.水下目标的合作声信标发射的信号频率可达100kHz,因此为了满足工程应用所需的测量精度,信号处理模块的采样频率应不小于500 kHz。但是由于主动定位系统是在统一的同步时序下工作的,因此每个处理模块只要获得接收信号相对同步信号的时延即可,也就是说,每个处理模块只需进行一路接收信号与不同发射信号的时延估计。

而对于被动定位系统,目标辐射噪声的频率范围主要位于100 Hz~2kHz,因此信号处理模块的采样频率不小于10 kHz就可以满足要求。但是由于被动定位系统没有统一的同步时序,因此只能通过估计不同接收信号的相对时延来进行目标的方位估计,也就是说,每个处理模块所需进行处理的接收信号不小于2个通道。

深入分析主/被动定位方法的信号体制及相应的处理方法可知,主动定位系统所需的信号处理模块的硬件规模和性能要求较高,因此信号处理模块的硬件设计以主动定位系统的性能指标为主、兼顾被动定位系统的指标要求。

1.1 模块的硬件功能及组成

本文设计的数字信号处理模块的主要技术指标包括:

1)输入模拟信号:通道数为3路,信号幅度为-10~10 V,频率为100Hz~30kHz;

2)通讯接口:RS422口及RS232接口各1个,自定义的通用IO口16位;

3)输出模拟信号:通道数为2路,信号幅度为-10~10 V;

4)LCD显示屏:彩色触摸屏;

5)运算能力:实时进行水下目标定位。

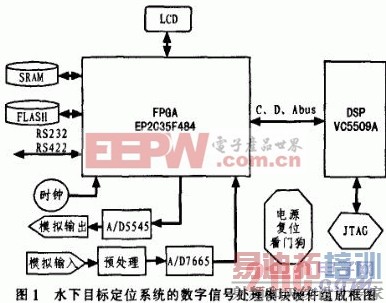

根据水下定位系统的功能需求和上述的指标要求,采用基于DSP+FPGA的硬件架构进行数字信号处理模块的设计,如图1所示。其中FPGA实现系统的时序控制、各种接口转换、数字信号预处理(如FIR滤波、FFT运算),而DSP实现系统的副本相关或互相关、包络检波等信号处理任务;这样既充分利用了FPGA的高度并行性和实时性,又充分使用了DSP的信号处理能力,使系统结构灵活、通用性强、运算能力强度,具有较好的工程应用参考价值。

1.2 硬件系统的主要器件选型

1.2.1 信号处理器

数字信号处理(Digital Signal Processing,DSP)的主要任务是完成水下目标的方位估计。因此选择DSP时首先考虑它的运算能力,在满足运算速度要求的前提下,要求DSP的功耗小、外围电路设计简单,软件开发容易。目前可供选择的DSP很多,包括TI公司的C2000系列、C5000系列、C6000系列,AD公司的BlackFin系列、SHARC系列、TigerSHARC系列等等,每款DSP都有其不同的特点。

针对本文设计的定位系统,综合考虑各因素,选用TI公司的TMS320VC5509A作为系统的DSP。

TMS320VC5509A是一款16位定点DSP,其片内的128 Kx16 bit SRAM空间可满足算法的存储空间需求;内核200MHz的时钟频率可满足系统的实时性要求;4个外部存储器片选信号便于通过FPGA,实现DSP与其他在板外设的数据交流和通信;5个外部中断输入可满足外部设备对DSP的突发请求。

1.2.2 FPGA

现场可编程门阵列(Field Programmable Gate Array,FPGA)的功能是实现系统的时序控制,并完成外部设备与DSP的接口转换,同时为了提高系统的实时性,实现定位系统的数字信号预处理,因此本文的FPGA选择主要考虑FPGA的片内存储器容量、乘法器数量、宏单元数量、性价比及开发的方便性等。目前可供选用的FPGA很多,根据定位系统的具体需求和研发人员的开发经验,选用Altera公司的EP2C35F484作为系统的FPGA,用于实现其相应的功能。EP2C35F484内部具有33216个逻辑单元(LEs),能够满足系统的各种时序控制;483 840 bits的RAM容量可以为DSP提供足够大的输入输出缓存,配合35个的乘法器,可以方便地实现数字信号预处理;4个PLL可以很方便地为系统产生不同的时钟信号或时序;322个用户I/O引脚数配合丰富的Les便于实现各种输入输出接口转换。

[p]

1.2.3 模数及数模转换器

模数及数模转换器的选择需同时考虑转换频率和分辨率。因此根据系统对输入模拟信号的精度要求,选择分辨率为16位的AD7665作为系统的模数(A/D)转换器。AD7665的最高采样频率可达570 kS/s,而且其允许的输范围为±10 V。满足系统的动态范围;其数字输出可采用串行或并行接口方式,便于与DSP或FPGA接口。

根据系统对输出模拟信号的精度要求,选用18位的AD5545作为系统的数模转换器(D/A)。AD5545是电流型输出型的双路D/A转换器。由于AD5545采用串行接口方式接收控制器的数据,因此AD5545的几何尺寸极小,便于高度集成。

1. 2. 4 存储器

作为一个可以独立运行的系统,总需要一定容量的非易失性存储器,用于存储系统的指令代码和缺省的系统参数,因此本模块采用闪存(FLASH存储器)AMD29LV256M进行系统的非易失存储器设计。AM29LV256M的容量为256 MBit,可以方便地构成16 Mx16-Bit或者32 Mx8-Bit的存储器,满足代码的固化需求。另外由于采用LCD液晶屏作为系统的显示器,而现有的LCD显示器没有显示缓存,同时为了增加系统的通用性和灵活性,便于进行大数据量的数据处理,系统需设计大容量的静态存储器(SRAM)。本模块选用CY7C1061AV33进行系统的外部存储器扩展。CY 7C1061AV33容量1 M×16-Bit,访问速度快。

1.3 系统的硬件电路设计

为了便于扩展,本模块的设计分3大部分进行:模块的供电、DSP最小系统以及以FPGA为核心的各种接口。

模块的供电采用LM2676-ADJ、TPS79501、LT1584CT3.3,将输入的12 V转换成DSP和FPGA所需要的5、3.3、1.6、1.2 V,并通过控制电源芯片的使能靖实现DSP的上电顺序。

DSP最小系统设计主要包括复位电路、时钟电路、调试接口等,其中复位电路采用Max706结合相应的外部器件实现上电复位、手动复位、看门狗复位、DSP内核电源电压过低复位、通过上位机复位等;时钟电路的设计结合DSP或者FPGA的片内PLL、采用高精度、高稳定度的外部有源晶振实现,并尽量降低外部晶振的频率,模块中的晶振频率为20MHz。而调试接口的设计由于需要经常插拔调试接口,因此主要考虑抗静电因素,通过在每根信号线上并联瞬态电压抑制器(TVS)实现;另外,为了进行较远距离的调试,进行了调试接口的再驱动及缓冲。

以FPGA为核心的各种接口设计包括存储器接口、外部中断接口、AD接口、DA接口、串行接口、LCD显示器接口等。为了便于扩展,DSP的EMIF信号线全部接到FPGA,并将FLASH存储器(AM29LV256M)和SRAM存储器(CY7C1061AV33)先通过FPGA再接到DSP的EMIF空间。也就是说,外部设备包括存储器可方便地映射到DSP不同的存储器空间。DSP的EMIF空间的缺省的配置为:CEO用于访问FPGA的片内SRAM(作用输入及输出缓冲的存储器):CE1用于访问DSP的上电程序加载空间,与FLASH存储器连接;CE2用于访问SRAM空间。外部中断接口用于将可选的多个外部中断源有选择的接到DSP的中断输入;缺省的配置为:INT0用于响应外部的同步,INT1用于RS422通信中断,INT2用于RS232通信中断;INT3、INT4为用户备用中断。AD接口首先将串行的采样数据转换成并行的数据并存放于FPGA的片内缓存或者直接将并行的采样数据存放于FPGA的片内缓存,用于FPGA的数据预处理(如FIR、FFT等),然后再将预处理的结果送到输出缓存。DA接口则在DSP的控制下、将DA输出缓存中的并行数据转换成AD5545所需要的串行接口数据,实现DA变换。串行接口则按照不同接口的收发协议,组织及收发数据,实现与不同设备的通信。LCD显示接口实际上是一个连续读写显存的接口,因此在FPGA内部设计了一个专门的读写显存控制器(简称LCD控制器),可以独立进行显示、控制LC D;但是为了便于DSP及时更新显示内容,在DSP和LCD控制器之间设计了一套仲裁电路,解决它们在读写显存时的冲突。

2 应用程序设计

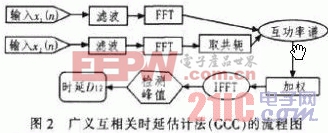

时延估计是声源定位算法的关键内容。为了进行时延估计,首先基阵接收目标信号模拟信号,再经过采集、依据不同方法进行处理,得到目标信号到达各个阵元的相对时延。一种广义互相关时延估计法(GCC)的流程图如图2所示。其中滤波在FPGA内部采用FIR实现,而FFT则可以由FPGA实现。也可由DSP实现。

[p]

3 实验

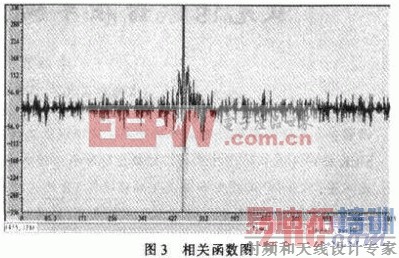

输入信号为两路CW信号,信号频率10kHz,脉宽1ms,两路时延0.2 ms,信噪比为-3 dB,A/D的采样频率为300 kHz,则信号脉宽有300个点,估计时延峰值应该在偏离中心60点处。按照图2的流程进行处理,采样宽度为512个点,广义互相关时延估计效果如图3所示。由图3可知,相关峰位于第455采样点处,即时延估计为0.19 ms,与给定的时延基本一致。

4 结论

本文研究的信号处理模块设计灵活性好、扩展性强,适合水下目标主被动定位系统的数据采集及处理,也可用于信号处理领域进行实时信号处理。本文所设计的以FPGA为核心的信号处理模块具有较好的工程应用参考价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...