- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一款基于FPGA的RFID阅读器设计

0 引 言

RFID 技术是从 20 世纪 80 年代走向成熟的一项自动识别技术,近年来发展十分迅速。 目前,在全世界,基于 RFID 技术的电子标签,使用已经 非常广泛了,这主要取决于它的特性,RFID 标签可以使用在几乎所有的物理对象上。RFID 技术在 工业自动化,物体跟踪,交通运输控制管理,防伪校园卡,电子钱包,行李标签,收费系统,医用装 置,电子物品的监控和军事用途等方面已经得到了广泛的应用。例如第二代居民身份证,使用基于 ISO/IEC4443-B 标准的 13.56 MHz 电子标签,该项 目可以说国内乃至国际上最大的RFID 应用的项目之一。

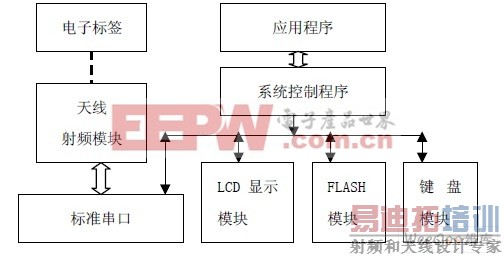

RFID 系统由阅读器(Reader),电子标签( Tag) 和后台数据库组成 ,见图1。阅读器从附着在物品上的Tag中读取数据,这些数据在阅读器或送给 后台的数据库应用程序进行处理。阅读器作为RFID 系统中的关键部件通过天线与电子标签进行无线 通信,可以实现对标签识别码和内存数据的读出或 写入操作。

图 1 RFID 系统构成。

FPGA 具有开发简单,静态可重复编程和动态在系统编程的特点,已经成为当今应用最广泛的 可编程专用集成电路。目前在 FPGA 的集成开发环 境中提供各种 I/O 接口的 IP 核,方便实现各种 I/O 接口。

现有的RFID 阅读器一般是由ARM( AdvancedRISC Machines)结构体系实现的,一般体积较大,不容易升级。本文研究和实现了基于FPGA 的阅读器,这种阅读器具有结构灵活、体积小、升级容易、方便实现不同的外设接口等优点。

论文结构如下第一部分描述阅读器的总体结构,第二部分是硬件部分结构,第三部分是软件部分结构,第四部分是阅读器的实现。

1 基于FPGA 的RFID 阅读器总体结构

阅读器是由FPGA、射频模块、LCD 和FLASH构成的,阅读器的系统结构见图2。 标准串口向射频模块发送对标签操作的命令,用于接收从射频模块返回的标签中的内容,LCD 显示标签信息,系统控制程序是系统的核心程序,它协调各部分的运行, FLASH 存储器存放数据。

图2 阅读器的系统结构

FPGA 实现的外部接口有:串口、LCD 接口、FLASH 接口和键盘接口等,射频模块内部含有符合RFID 标准的标签操作程序,能够执行来自串口的操作标签的命令,返回标签的信息。

2 阅读器的硬件部分结构

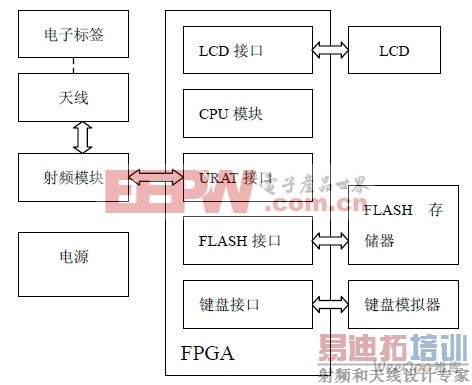

阅读器是以FPGA 为核心,控制数据处理交换的模块结构。FPGA 实现的模块有:各个外设接口和CPU 模块,这些模块由该FPGA 内部的可编程逻辑电路实现的,它完成与射频模块的通信,射频模块前端与标签的空中接口通信读取标签信息,FPGA 从串口模块取回标签信息送LCD 显示,硬件结构如图3。

图 3 阅读器的硬件结构。

3 阅读器软件部分结构

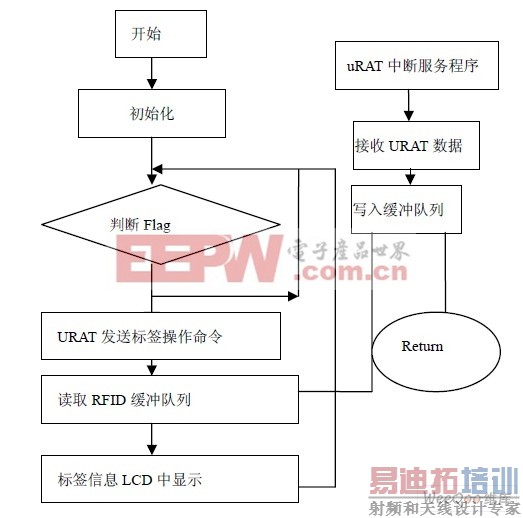

程序的执行从键盘的触发开始,此时通过串口向射频模块发送读标签命令,射频模块返回标签的信息,触发串口中断服务程序执行,将读出的信息放入FIFO 对列,将结果送LCD 显示。软件部分程序执行流程图见图4。[p]

图4 软件部分程序执行流程。

4 阅读器的实现

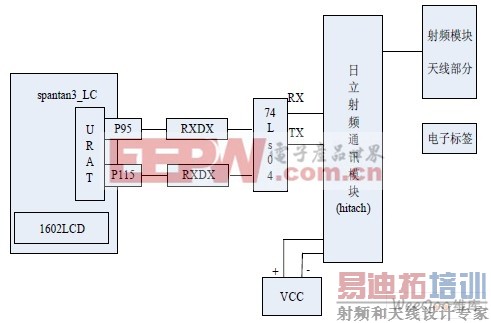

本文使用日立产射频模块、2.4GHz 电子标签、Xilinx Spartan-3 LC1500 开发板、Xilinx PlatformStudio 7.1i 集成开发环境和Xilinx ISE 7.1i 集成开发环境硬件连接见图5。FPGA 开发板设计一个串口连接射频模块,用于向射频模块发送标签操作命令和接收标签的信息。图中URAT 为设计的串口,G16和H16 为FPGA 的I/O 引脚,74LS04 为电平转换模块。1602 为液晶显示模块。

图5 硬件连接。

4.1 FPGA 中的CPU 模块

嵌入式CPU 的设计是SOC 设计的核心。FPGA可以方便地实现嵌入式CPU 核[6],在FPGA 器件中嵌入式CPU 有硬核和软核两种,如Xilinx 的VirtexII器件中含有CPU 硬核POWERPC401 核,Altera 的Excalibur 器件中含有PowerTrace 核;软核如Xilinx的PicoBlaze 和MicroBlaze, Altera 的Nios, Tensilica的Xtensa 和OpenCores 的OpenRISC 软核。硬核提供了丰富的指令和功能,但不能改变其电路结构。硬核具有高速和高效的优点,但熟悉和充分掌握硬核的使用比较困难,硬核并不是所有的FPGA 器件都有的。而软核是用VHDL 语言设计实现,设计者可以根据具体需要进行设计或对软核进行适当的修改,适当增加或减少硬件电路,如寄存器数量,RAM容量和总线宽度等,,提高芯片利用率,,还可以提高CPU 运行速度,并且软核还具有使用灵活和低成本的特点。本文使用的是Microblaze 软核。

4.2 实现过程

在集成开发环境中添加LCD、 URAT 和DIP的软件IP 核,其中DIP 用于模拟键盘输入。然后配置各个接口IP 核的总线类型、地址范围和外部端口,在项目的UCF 文件中配置接口IP 核的引脚和FGPA 的I/O 的连接关系。

从串口接收数据有两种方法:一种是采用定时器读;另一种采用串口的中断服务程序来读。采用定时器消耗资源比较大,本文采用串口中断的方法,当串口有数据到达时,激活串口中断服务程序,在中断服务程序中读出串口缓冲区的数据,然后写道FIFO 对列。

URAT 中断服务程序的主要代码如下:

Void XUartLite_InterruptHandler ( XUartLite *

InstancePtr)

/*判断Uart 缓冲区是否为空*/

if(!XUartLite_mIsReceiveEmpty(RS232_BASEADD

R))

{

/*接收URAT 数据*/

Data=XUartLite_RecvByte(RS232_BASEADDR);//

/*写入FIFO 缓冲队列*/

Add_Queue(Data);

}

其中FIFO 缓冲队列是由一个自定义的数据结构和对它的操作实现的。

下面是主程序的主要代码。[p]

初始化部分

/*URAT 初始化*/

XUartLite_Initialize( Uart,

XPAR_RS232_DEVICE_ID)

/*LCD 初始化*/

void lcd_init(unsigned int base_addr)

/*URAT 开中断*/

void XUartLite_EnableInterrupt ( XUartLite *

InstancePtr)

/*设置URAT 初始化*/

void XUartLite_SetSendHandler(XUartLite

* InstancePtr, XUartLite_Handler FuncPtr, void

*CallBackRef)

/*设置URAT 的中断服务程序*/

void XUartLite_SetRecvHandler(XUartLite *

InstancePtr, , XUartLite_Handler

XUartLite_InterruptHandle, void * CallBackRef)

初始化完成以后,然后进入一个无限循环。

/*判断是否有键按下*/

XGpio_InterruptGetStatus(XGpio *InstancePtr)

/*发送读标签命令*/

for (j=0;jcount ;j++)

{ XUartLite_SendByte(UARTLITE_0_BASEA

DDR, *(commanda+j) );

wait(50000);

}

/*如果对列不为空*/

If(!IsEmptyQuque())

/* 读取队列数据 */

Read_Quque(data )

/* 写入FLASH*/

void flash_write(Xuint32 addr, long data)

对FLASH 的操作首先要块檫除,然后才能写,对FLASH 写的代码如下:

void flash_write(Xuint32 addr, long data)

{XIo_Out32(flash_base_addr + (0x555 2),

0x00aa00aa);

XIo_Out32(flash_base_addr + (0xaaa 2),

0x00550055);

XIo_Out32(flash_base_addr + (0x555 2),

0x00a000a0);

XIo_Out32(addr, data);

return;

}

程序编写完成后,经过编译和消除错误后,下载到目标板,在FPGA 开发板运行程序,在LCD得到标签信息,见图6。

图6 标签信息在LCD 的显示

6 结 论

RFID 技术是近年来发展起来的一种新型的自动识别技术。FPGA 技术是未来硬件广泛使用的一种技术,本文结合将RFID 技术与FPGA 技术相结合,研究和实现了一种新结构的阅读器,基于FPGA的阅读器具有结构灵活、体积小、升级容易和易扩展等优点。本文给出了阅读器的总体结构、硬件部分结构和软件部分结构,研究了RFID 射频模块与FPGA 之间的接口实现及标签信息在LCD 显示。具有广泛的使用价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:μC/GUI在Nios

II嵌入式平台上的移植研究

下一篇:基于FPGA和TMS320DM642的CCD

像采集和处理系统硬