- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA控制的数字化语音存储与回放系统

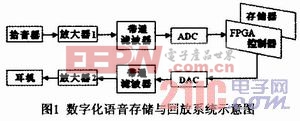

摘要:数字化语音存储与回放系统的作用是对语音进行录音和放音,并实现数字化控制。能够做到语音回放的方法有很多,本课题研究的是基于FPGA控制下的语音存储与回放系统。

关键词:语音录放;数模转换;模数转换;FPGA

1 设计要求

设计并制作一个数字化语音存储与回放系统,其示意图如图1所示。

(1)放大器1的增益为46dB,放大器2的增益为40dB,增益均可调;

(2)带通滤波器:通带为300Hz~3.4kHz;

(3)ADC:采样频率fs=8kHz,字长=8位;

(4)语音存储时间≥10s;

(5)DAC:变换频率fc=8kHz,字长=8位;

(6)回放语音质量良好。

不能使用单片语音专用芯片实现本系统。

2 数字化语音存储与回放系统硬件电路

2.1 放大器1即音频信号放大电路

音频信号放大电路如图2所示。第一级放大(-4.7)倍。IRD120实现自动增益控制,当开关打到1的位置是增益自动控制,当开关打到2的位置是手动控制。增益自动、手动控制是利用场效应管工作在可变电阻区,漏源电阻受栅源电压控制的特性。第二级放大(+101)倍。第三级放大倍数可调,最大(-20)倍,保证ADC0809满量程转换。

2.2 带通滤波器

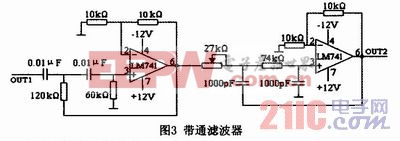

带通滤波器如图3所示。实测带通300~3300Hz。保证语音信号不失真地通过滤波器,滤除带外的低频信号和高次谐波。

[p]

2.3 模数转换(ADC)电路

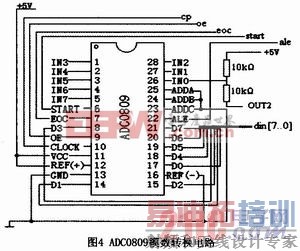

ADC电路如图4所示。题目要求采样频率fs=8kHz,字长=8位,可选择转换时间不超过125 μs的8位A/D转换芯片,ADC0809的转换时间为100μs,可选用ADC0809。音频信号经过放大、滤波送给ADC0809 ADC电路,将模拟量转换为数字量,再经可编程器件送给存储芯片。cp、oe、eoc、start、ale、din[7..0]接图9。

2.4 语音存储电路

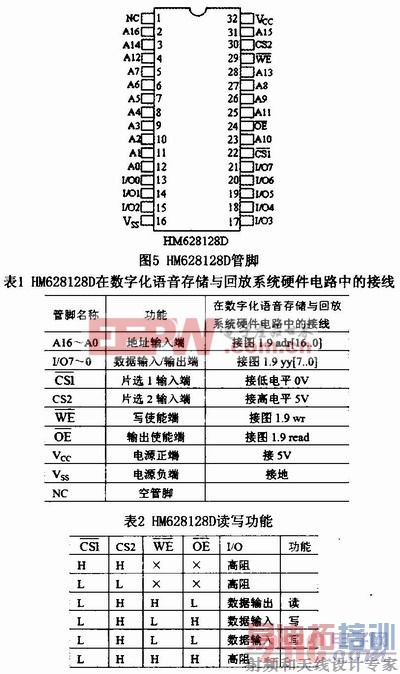

存储芯片HM628128D管脚如图5所示。HM628128D可存储8位131072字,5V供电,静态RAM。语音存储时间≥10s。HM628128D在数字化语音存储与回放系统硬件电路中的接线如表1所示。HM628128D读写功能如表2所示。

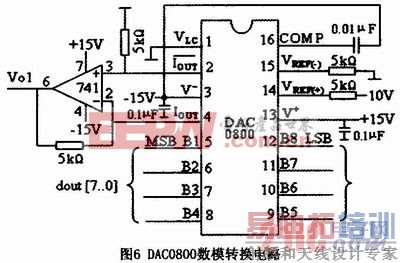

2.5 数模转换(DAC)电路

DAC如图6所示。题目要求变换频率fc=8kHz,字长=8位,可选择转换时间不超过125μs的8位D/A转换芯片,DAC0800的转换时间为100ns,可选用DAC0800。存储芯片输出的数字量经可编程器件图9送给DAC0800 DAC电路,将数字量转换为模拟量。

[p]

[p]

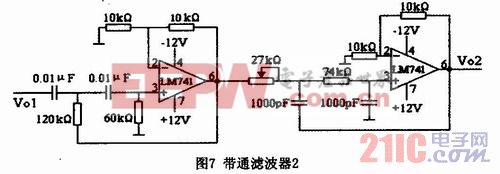

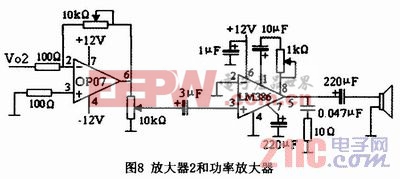

2.6 带通滤波器和功率放大器

带通滤波器2如图7所示。放大器2和功率放大器如图8所示。图6、图7、图8连接起来就可以获得音频信号。

3 数字化语音存储与回放系统软件电路

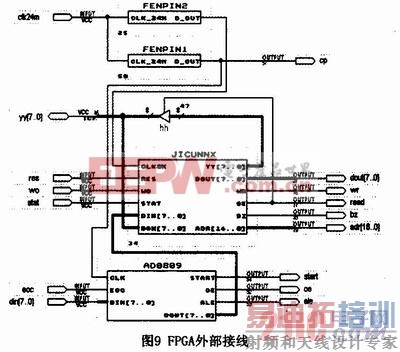

3.1 FPGA外部接线

FPGA外部接线如图9所示。clk24m接24MHz晶振,cp接图4 ADC0809 ADC电路,yy[7..0]接图1.5 HM628128D,res接按键开关res为0时地址复位为0,wo接高低电平开关wo为0录音wo为1放音,stat接高低电平开关,开始录音或放音。dout[7..O]接图6,wr、read、adr[16..O]接图5HM628128D,bz接发光指示灯显示录音或放音工作状态,其余端接图4 ADC0809 ADC电路。

4 结论

此课题的创新点在于用FPGA控制数字化语音存储与回放,取代了以往用单片机去控制;同时此课题综合了数电、模电、DAC、CAD、FPGA等多方面电子知识,对学生做课程设计、电子实验有着很大的实用性。同时此课题可作为产品开发,成本低、可靠性高,将会有一定的市场。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的32位ALU软核设计

下一篇:机电产品的电磁干扰抑制措施