- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的扩频测距快速捕获仿真研究

距离测量是测试技术中的一项基本测试技术,其几乎贯穿于工程实践的每个领域。在军事航天领域,由于其特殊的需求,对测距系统的量程、实时性和精度要求越来越高,而扩频测距由于其抗干扰能力强、精度高、作用范围广、隐蔽性好、适应性强、全天候等优势,在测距系统中得到了重视。

扩频测距也称伪码测距,它是采用一个较长周期的PN码序列作为发射信号,将它与目标反射或转发回来的PN码序列的相位进行比较,即比较两个码序列相差的码片数,从而看出其时间差,换算出发射机与目的地之间的距离。如果码片选得很窄,即码速率做得很高,那么就可以完成高精度的测距。但随着码速率的提高和码周期的加长,传统的捕获时间将达到不可容忍的地步,所以需要考虑快速捕获算法。

由扩频码的自相关函数可知,只有在t’=(t-τ)时,扩频解调输出V(t)的信号最大。根据τ就能算出两地的距离![]() ,c为电磁波传播速度。

,c为电磁波传播速度。

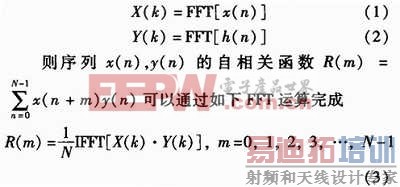

由于计算两序列的自相关函数![]() 需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

可知R(m)为现有发射PN码与反射回来的PN码之间的相关值序列,长度为N,可知当R(m)中最大值的序列号减1即为码片差。

1 仿真方案设计

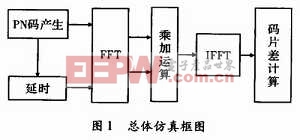

首先由m序列发生器产生出两路序列长度为N的PN码,其中一路经过延时模块以后与另一路分别进入FFT模块进行FFT运算,将进行FFT后的两组数据运算后进入IFFT模块得出序列组,由序列组得出两路序列之间的码片偏移数,从而算出其时延。系统总体框图如图1所示。

[p]

2 主要模块仿真结果

2.1 PH码产生模块

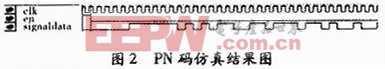

本设计选取的PN码为63位,本征多项式为x6+x+1。该PN码产生器由VHDL语言编写,其仿真结果如图2所示。

2.2 FFT转换模块

该模块是本设计的核心模块,由输入缓冲器、FFT运算器、控制器构成,完成对数据的FFT变换。将PN码发生器产生的数据存入输入缓冲器中,在控制器的控制下,FFT运算模块从输入缓冲器中读取出数据值进行FFT变换,然后得出输出数据。图3所示为FFT模块的输入输出关系。fft_imag_out,fft_real_out分别为输出数据的实部、虚部和修正因子,m_soutoe_sop为输出数据的起始位。

2.3 计算模块

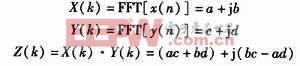

设两路信号进行FFT后的数据为

可见对进行FFT变换后需要进行的运算处理其实质是一个乘加,一个乘减和一个加法运算,其中乘加运算仿真结果如图4、图5所示。

[p]

2.4 判断模块

判断模块的主要功能是对IFFT后的序列的最大值进行判断,得出其最大值所在的序列号减1就为其码片差τ。clk为时钟信号,rest为开始信号,data_in为输入数据,data_out为输入数据data_in中最大值所在的序列号减1。图6为判断模块仿真结果。

2.5 系统总设计图及仿真结果

本设计采用自顶向下的设计方法,利用VHDL语言描述出扩频测距快速捕获的各个功能模块。图7所示为总体仿真结果,图中fft_imag_ outf,fft_real_outf为ifft后的数据,data_out为输出数据,由此可见,仿真结果与设定的τ=3一样,验证了本设计的可行性。

3 结束语

采用FFT代替自相关函数计算扩频系统中的码片偏移可节省硬件计算时间。经过硬件的优化设计与仿真,在Altera Straix II系列FPGA上,时钟频率达到109.1 MHz,捕获时间和计算时间大约在2μs,捕获时间提高。此外,由于扩频技术可以极大地抑制突发干扰和脉冲干扰,所以扩频测距比起传统的测距方法,如激光测距,超声测距等方法能适用于更恶劣的环境,如卫星测控,而由于使用快速捕获技术,可进一步提高实时性,在对测距实时性要求更高的引信技术中也可以采用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:YAG激光电源的电磁兼容性探讨

下一篇:常用的抗扰度试验标准