- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于PCD656的高速PCI总线接口的设计与实现

现代雷达信号处理具有数据量大、实时性高等特点,而总线传输的效率决定了系统的性能,目前普遍使用标准化的PCI总线技术,以便升级更新。为加快产品开发和降低设计难度,一般有两种解决方法:采用通用的PCI芯片或IP核。目前常用的PCI芯片如PCD054、PCD052等虽然性能稳定、使用方便,但它们只适用33 MHz、32位总线接口,受时序设计和应用程序效率等影响,总线传输速度约稳定在70 MB·s-1;使用IP核虽可以兼容66 Hz、64位总线且节省板卡面积,但其价格昂贵不利于高校及中小企业推广使用。而PCI9656适用于66 MHz、64位的PCI总线,因此逐渐成为总线开发的主流元器件,使得总线传输速度达到了150 MB·s-1甚至更高。

本文利用高效PCI芯片和FPGA设计了一款64位总线传输接口电路,传输速度达到212 MB·s-1,较以往总线传输速度有了较大地提高,满足了目前高速数据传输系统的要求。

1 PCI总线接口架构

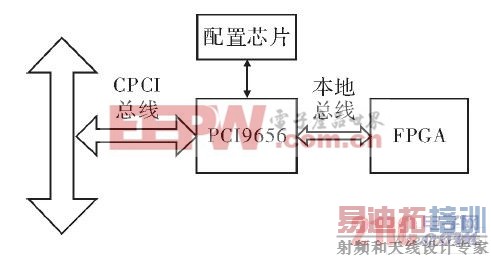

本系统主要由PCI9656和FPGA构成,系统框图如图1所示。当主机发起读写操作时PCI9656需要响应其操作,并将相应命令发送到FPGA进行处理,FPGA进行处理后将数据和命令通过PCI9656回传给主机。PCI9656与主机之间的通信需要相应的设备驱动程序支持,而FPGA响应主机命令则需要配置相应的局部时序。因此,本设计主要的工作为设备驱动程序的开发和FPGA局部时序的设计。

图1 总体传输系统框图

2 PCI9656性能概述

PCI9656是PLX公司推出的一款兼容32位和64位PCI总线标准的桥接芯片,采用PLX数据流水线结构(Data Pipe Architecture),内部配有DMA控制器、可编程主模式传输及从模式传输;内部有PCI优先判决器,可以支持外部7个外部主控器;可由本地中断信号LINTi和LINTo生成一个PCI中断信号INTA;本地时钟独立于PCI时钟工作;支持位宽为8位、16位和32位的66,MHz本地总线。PCI9656寄存器与PCI9054寄存器兼容,可容易地进行基于32位PCI总线与基于64位PCI总线的软件移植。

PCI 9656具有6条独立的数据通道,分别支持Direct Master、Direct Slave以及DMA功能模式下的数据传输。

(1)Direct Master模式。用于局部总线到PCI(CompactPCI)的数据传输,主控设备在局部总线端。16 QWord(128 Byte)和32 QWords(256Byte)的FIFO各应用于数据的读、写通道。

(2)Direct Slave模式。用于PCI(CompactPCI)到局部总线的数据传输,主控设备在PCI端。16QWords(128 Byte)和32 QWords(256 Byte)的FIFO各应用于数据的读、写通道。

(3)DMA模式。DMA传输时PCI9656同时是PCI和局部总线的主控设备,PCI 9656有两条DMA通道(Channel 0、Channel 1),每条通道都由一DMA控制器和32 QWords(256 Byte)双向FIFO组成。其DMA方式有常规的块模式(Block Mode)、集散模式(Scatter/Gather Mode)和命令模式(Demand Mode)。

在局部总线端,根据不同的处理器PCI9656有3种工作模式。

(1)M模式。支持Motorola 32 bit的处理器,提供了可与MPC850/860 PowerQUICC直接相连的接口。

(2)C模式。适合大多数处理器的通用模式,比如常用的FPGA,在本设计中采用此模式。

(3)J模式。与C模式类似,但其地址线与数据线复用。

[p]

3 总线设备驱动开发

在Windows环境下开发PCI设备驱动程序主要有两种模型,即WinDriver和WDM。本设计使用了WDM驱动模型。开发PCI设备驱动程序WDM需要处理:硬件访问、中断处理和DMA传输3方面问题。

3.1 硬件访问

X86处理器有两种独立的映射空间:I/O空间和内存空间,I/O空间只能通过I/O指令来访问,KIoRange类封装了对I/O空间的操作命令。对于设计的PCI设备,可以通过实例化KIoRange类来对I/O空间进行相应的操作。

对于PCI设备可以使用KMemoryRange类对内存进行相应操作,具体操作与KIoRange类对I/O空间的操作相似。

3.2 中断处理

驱动程序使用KInterrupt类来实现对中断操作的处理,其中包括中断的初始化、将一个中断服务例程连接到一个中断和解除其连接等。

中断服务例程不是KInterrupt类的成员函数,这是为了减少中断延迟时间。中断处理需要中断服务例程和延迟过程调用例程,在中断服务例程中,首先判断该中断是否是自己设备产生的,若不是,则返回False;若是,则请求一个延迟过程调用例程(DPC)。

3.3 DMA传输

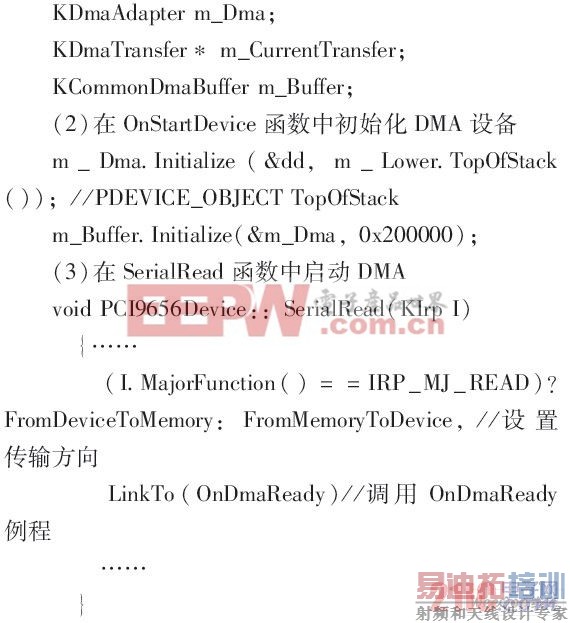

PCI9656使用DMA方式进行数据传输。实现DMA传输需要3个类:KDmaAdapter,KDmaTransfer和KCommonDmaBuffer。其中,KDmaAdapter类用于建立一个DMA适配器,它说明了DMA通道的特性,如总线宽度,单次传输最大个数等,需要注意的是本设备使用的是64位总线宽度,因此需要特别指出;KDmaTransfer类用于DMA传输控制,如传输开始、传输字节数等;KCommonDmaBuffer类用于申请系统提供的公共缓冲区。具体DMA传输设置如下

(1)实例化三个类

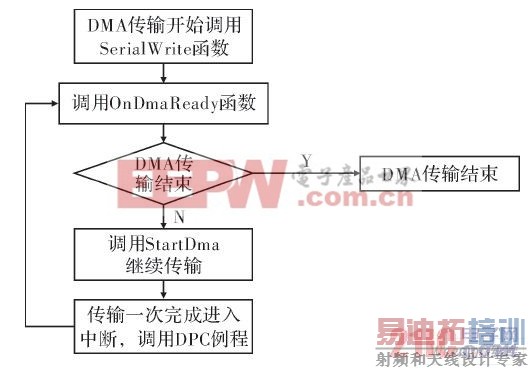

OnDmaReady例程中获取传输的物理内存的地址和字节数,然后设置相应的DMA寄存器值开始DMA传输。DMA传输结束后,应使m_CmxentTm-nsfer无效并删除。具体流程如图2所示。

图2 DMA传输流程[p]

4 局部总线端设计

本设计中,局部总线端采用了C模式。C模式下可配置3种数据传输方式:单周期方式(Single Cycle Mode)、4字方式(Brust-4 Mode)和连续突发传输方式(Continuous Mode),在本设计中采用了连续突发方式,可以有效地提高输出效率。

PCI9656在局部总线为为主设备,始终占用局部总线,局部总线端的FPGA始终响应PCI9656的操作。方案中使用PCI9656的DMA传输模式,在本地端不需要进行地址译码,因此可以对PCI9656的控制信号进行简化处理,PCI9656的局部端主要控制信号如下

ADS#:一次总线访问开始;

Blast#:总线访问结束;

LW/R#:读写控制信号;

Ready#:从设备准备好信号,有效时表示总线访问进行中;

LHOLD:PCI9656占用本地总线申请信号;

LHOLDA:占用本地总线应答信号;

Wait#:主设备传输暂停信号;

EOT#:数据传输异常中止信号,用于FIFO溢出或空时中断数据传输;

Lint#:用于引起CompaetPCI总线端的中断信号;

LRST#:本地总线复位信号;

CCS#:配置寄存器选择信号。

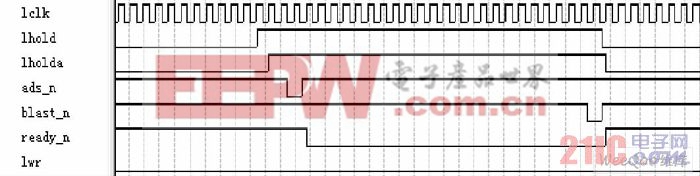

在DMA传输过程中主要关心的信号可简化为:ADS#、Blast#、LW/R#、Ready#、LHOLD、LHOLDA,如图3所示。

图3 PCI局部总线控制时序

图3中,lclk为本地总线时钟,当PCI9656要发起一次DMA操作时,先发送lhold信号申请本地总线,若本地总线空闲则FPGA发出lholda信号响应PCI9656,然后PCI有效ads_n信号以示总线传输开始,FPGA使ready_n有效以示总线传输正在进行中,此时本地数据通过局部数据线传送到PCI总线,或着数据由PCI总线传送到局部逻辑。一次传输结束时PCI使blast_n信号有效并使lhold信号无效,然后FPGA使lholda信号和ready_n信号无效,一次DMA传输完成。传输中若是DMA读操作则lwr信号拉低,若为写操作则拉高。

本地总线位宽为32位,因此本地总线理论速度为264MB·s-1,由于应用程序的效率问题和传输中一些无效状态的存在,目前PCI总线平均速率达到212 MB·s-1,可以满足目前高速数据采集、传输对总线传输速度的要求。

PCI9656本地总线时序设计中需要注意blast_n信号有效说明为突发传输最后一个时钟周期,此时ready_n信号仍然为有效,否则会造成总线等待;在正常读写访问中CCS#信号应置高,否则总线访问将指向配置空间而非内存或I/O空间。

5 结束语

利用PCI9656和FPGA实现了一种高速PCI总线接口,较全面地论述了总线驱动开发和局部时序设计的过程。这种设计提高了总线传输速度,为高速数据采集系统的实现创造了条件。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:某探测系统的电磁兼容性探讨

下一篇:基于TVP5150的视频LCD显示设计