- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的VGA控制器实现

摘要:依据标准的VGA显示接口的显示原理,介绍了一种利用可编程逻辑器件FPGA,并以VerilogHDL语言为逻辑描述工具来完成VGA接口的控制,从而实现简单的彩色条纹显示的具体方法。

关键宇:VGA;FPGA;VerilogHDL;彩色条纹显示

0 引言

VGA作为一种标准的显示接口,现已得到了广泛的应用。传统的VGA显示控制主要以专门的芯片电路和通用处理器来实现,体积大且不灵活。随着EDA技术的发展,可编程逻辑器件有了长足的发展。FPGA是现场可编程逻辑阵列器件,简化的FPGA基本由可编程输入输出单元、基本可编程逻辑单元、嵌入式RAM模块、丰富的布线资源、底层嵌入式功能单元和内嵌专用硬核等6部分组成。基于FPGA的产品设计具有开发过程简单,投资小,可反复修改,周期短,易于产品升级等优点,故其应用越来越广泛。本文介绍了一种用FPGA实现VGA显示的控制器,从而实现简易彩色条纹显示,并在此基础上通过外加存储器模块来完成图像的实时处理与显示的实现方法,该方法也可方便地应用于各种嵌入式便携系统中。

1 VGA的显示原理

VGA是IBM在1987年随PS/2机一起推出的一种视频传输标准。这个标准具有分辨率高、显示速度快、颜色丰富等优点。根据分辨率不同,VGA又可分为VGA(640x480)、SVGA(800x600)、XGA(1024x768)等。VGA显示采用逐行扫描方式。扫描是从屏幕的左上方开始,从左到右,从上到下。每扫完一行,电子束回到左边下一行的开始位置,期间对电子束进行行消隐。并在每行结束时,用行同步信号对行进行同步,扫描完所有行后,再用场同步信号对场进行同步,并使电子束回到屏幕的左上方,同时对场进行消隐,并预备下一次扫描。该方法的关键是对时序的控制。

1.1 VGA时序

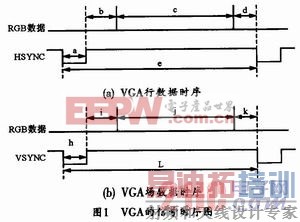

确定VGA显示接口时序主要应考虑行同步信号(HSYNC)、场同步信号(VSYNC)、蓝基色(B)、红基色(R)、绿基色(G)这5个信号,如果能从FPGA中按其时的需要求准确发送这些信号到VGA接口,就可以实现对VGA的控制。VGA的信号时序如图1所示,它分为行数据时序和场数据时序两部分。

所谓行时序,就是显示一行数据的时序。从图1(a)可以看出,显示一行数据需要的时序分四部分。产生行同步脉冲信号HSYNC的周期e=a+ b+c+d。其中a为同步信号时间。b为行消隐后肩时间,c为数据有效时间,d为行消隐前肩。从图(b)可以看出,场同步时序与行同步时序类似,也是显示一屏数据的时序,这里以行为单位。场同步脉冲信号VSYNC的周期L=h+i+j+k,其中h为同步信号时间,i为场消隐后肩时间,j为数据有效时间,k为场消隐前肩时间。

不同的分辨率下,行同步和场同步信号的周期是不同的,时序上的时间也不一样。表1列出了VGA的常用分辨率参数。

[p]

本设计以640x480且刷新频率为60Hz为例,其显示器每秒扫描60场,VGA在实际工作时并不是每行扫描640个点,每场扫480行,由图及表1可知,由于行消隐和场消隐的存在,实际是每行800个像素,每场525行。每行800个像素中包括行消隐前肩d(16个点)、行同步信号a(96个点)、行消隐后肩b(48个点)和有效点数c(640个)。每场525行中包括场消隐前肩k(10行)、场同步信号h(2行)、场消隐后肩i(33行)和有效行数j(480行)。所以,点像素的时钟频率为800x525x60=25.175MHz。

1.2 VGA时序控制信号的产生

VGA时序控制信号的产生包括行点计数器h_cnter、场行计数器v_enter、行同步状态机和场同步状态机。h_enter是800进制计数器,v_ cnter是525进制计数器。行同步状态机有a(行同步)状态、b(行消隐后肩)状态、c(数据有效)状态和d(行消隐前肩)状态,4种状态可根据h_ enter的值进行状态翻转。场同步状态包括h(场同步)状态、i(场消隐后肩)状态、j(数据有效)状态和k(场消隐前肩)状态,4种状态也可根据v_enter的值进行状态转换。其状态转移图如图2所示。

当状态机上电复位后,行状态机进入a状态,此时HSYNC输出为低,行计数器h_enter开始对25MHz的点时钟计数,当计数到95时,转移到b状态,而当计数到143时,从b状态转移到c状态,当计数到783时,从c状态转移到d状态。在b、c、d三状态时,HYNC输出为高。当状态机上电复位后,场同步状态机进入h状态,每当行计数器h_cater=7991时场行计数器v_enter加1,当v_enter=1时,状态机从h状态转移到i状态,当v_enter=34时,状态机转移到j状态,当v_enter=514时,状态机转移到h状态,此时场同步信号VSYNCS输出为低,其他状态输出为高。只有当行同步状态机在c状态且场同步状态机在j状态时,才能向RGB输入数据。

[p]

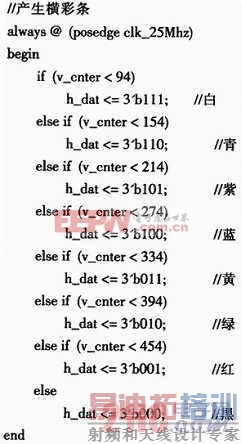

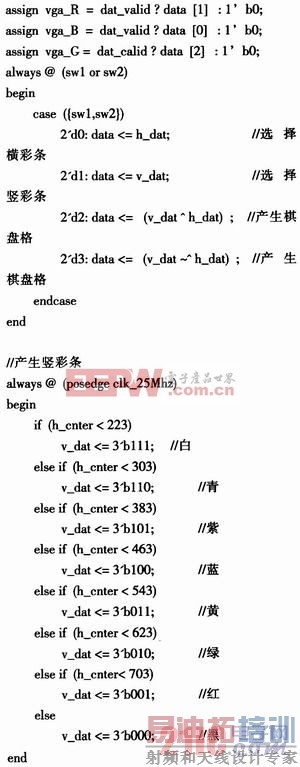

2 彩色条纹的实现

本部分包括彩色条纹模式显示控制、横彩条的实现、竖彩条的实现和棋盘格实现等。竖彩条可根据行计数器产生,在640个有效数据区内,每80个产生一个彩条,即对其进行8等分。横彩条则可根据场计数器产生,在480个有效区内,每六十个产生一个彩条,也是8等分。棋盘格可由横彩条数据和竖彩条数据异或而得到。可通过拨码开关sw1、sw2来控制彩色条纹类型的输出。其部分Verilog HDL代码如下:

3 结束语

本设计主要通过FPGA来完成对VGA的控制。此方案简单灵活且修改方便,可以充分发挥FPGA的灵活性。另外,此设计采用参数化设计,可方便的通过修改参数来满足不同分辨率的实现,同时在此基础上,通过外加存储器模块可以完成图像的实时处理和显示,因而可在嵌入式方面得到广泛的应用。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的高精度信号源的设计

下一篇:基于PSoC3的多通讯接口时的DMA设计