- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

π/4-DQPSK差分解调器的数字化FPGA设计与实现

摘要:给出了采用FPGA设计芯片技术对QPSK解调器进行设计的实现方法。该方法可将解调器中原有的多种专用芯片的功能集成在一片大规模可编程逻辑器件FPGA上,从而实现了高度集成化和小型化。仿真结果表明,该方案具有突出的灵活性和高效性,可为设计者提供多种可自由选择的设计方法和工具。

关键字:差分解调;FPGA;π/4-DQPSK

0 引言

在现代移动通信中,使用较多的数字载波调制解调技术是多进制相移键控。π/4-DQPSK相位调制技术就是在常规DQPSK调制基础上发展起来的,它的相位跳变值是π/4、3π/4,5π/4或7π/4,在DQPSK中,180°相位翻转对应有丰富的功率谱旁瓣能量,限带引起的包络起伏将通过非线性功放的转换效应导致可观量值的频谱扩散,从而使旁瓣干扰增大和限带滤波作用抵消。与QDPSK相比,π/4-DQPSK限带滤波后有较小的包络起伏,其最大相位翻转为135°,并在非线性信道中有更优的频谱效率。而软件无线电作为解决通信体制兼容性问题的重要方法,现已受到各方面的注意。该方法的中心思想是以硬件作为无线通信的基本平台,而把尽可能多的无线通信功能(如工作频段、调制解调类型、数据格式、通信协议等)用软件来实现。而FPGA器件可反复编程,重复使用,因此用其实现调制解调是实现软件无线电的一个重要环节。

1 π/4-DQPSK的基本原理

π/4-DQPSK数字基带调制信号的数学表达式为(假设载波初相为0):

![]()

这里,g(t)是持续时间为Ts的矩形脉冲,θn为受调相位。表1所列是π/4-DQPSK信号的相位编码逻辑关系。

[p]

2 π/4-DQPSK的解调

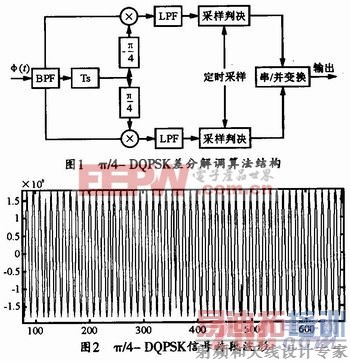

对于差分相干解调,通过比较前后码元载波相位,便可分别检测出A和B。然后用图1所示的方法还原成串行二进制数字调制信号。

设某一码元及前一码元载波为:

![]()

那么,将AD采样输入FPGA中的π/4-DQPSK波形所图2所示。[p]

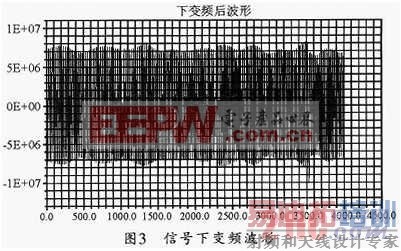

经过混频后进入解调器的信号φ(t)的波形如图3所示,设上支路为A,下支路为B。那么,经延迟移相后,其上、下两支路分别为:

而乘法器的输出为:

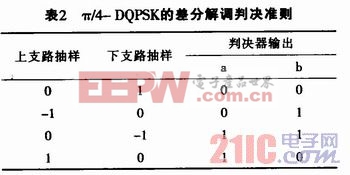

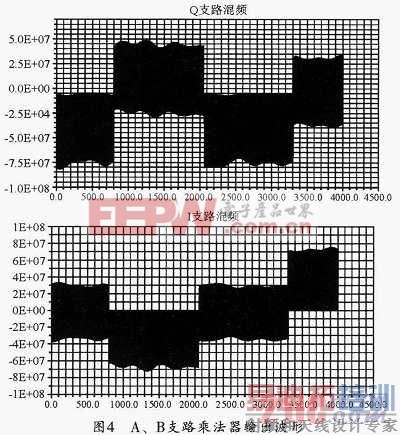

其A、B支路的乘法器输出波形如图4所示。表2所列为π/4-DQPSK的差分解调判决准则。

[p]

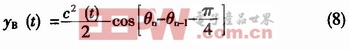

下面是A、B两路乘法器的LPF输出:

![]()

3 结束语

π/4-DQPSK差分解调算法的所有部分均可由VHDL编程实现。目前,整个过程已经经过功能仿真和时序仿真,并用OUARTUS II进行了综

合、映射、布局布线,现已成功下载到Cyclone II中运行。可满足预期的设计目标。该方案实现简单,速度快,占用硬件资源少,非常适合工程应用。其软件和硬件相结合的方法还具有体积小、功耗低、集成度高、可软件升级、抗干扰能力强等特点,符合未来通信技术发展的方向。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:LZW改进压缩算法的FPGA实现

下一篇:LVDT数字解调方法研究