- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TDI-CCD的成像FPGA系统软件设计应用

摘要:为建立高速、高效、合理的CCD成像软件系统,设计TDI-CCD成像系统自顶向下的软件设计结构和模块化设计方法,实现成像系统FPGA软件解耦合,给出整体软件设计结构及其性能分析;在系统调试阶段运行良好。实际运行结果表明,该软件得各项性能指标达到设计要求。

关键词:FPGA;CCD成像;模块设计;解耦分析

CCD是一种广泛应用于成像系统中的光学传感器,TDI-CCD利用延时积分的方法,通过对同一物体多次曝光,实现增强型光能采集的目的。同时,根据像移补偿的速度,设计TDI-CCD的电荷转移速率,能够实现电子学像移补偿。本文阐述的成像系统以TDI-CCD为核心,利用FPGA实现CCD图像数据整合功能的硬件系统。由于FPGA在资源、速度、效率、稳定性等方面有很多优势,因此,采用FPGA实现高速、大规模、继承性好的成像软件,通过在软件结构、模块和设计方法上的优化,寻求更加合理设计方案,达到功能和性能的提升。本文将FPGA设计的一些指导性原则应用于实际的系统设计中,给出了FPGA自顶向下的软件结构划分,以及程序设计中的注意事项。通过对模块接口信号的解耦处理,增强了系统的适应性和稳定性,该软件系统在实际工程中已进行验证。

1 成像系统结构

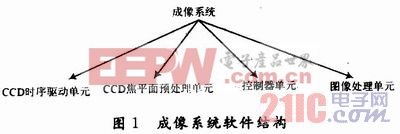

成像系统以TDI-CCD为核心,采用FPGA作为核心数据处理单元,实现数据处理传输,其基本组成部分如图1所示。

时序驱动单元采用FPGA产生驱动时序,通过硬件电路实现对CCD控制信号驱动;焦平面单元将CCD视频信号经过预放、滤波、相关双采样(CDS)、A/D转换后输入到图像处理单元;图像处理单元接收控制器指令,完成总体对成像系统的控制,以及图像数据的整合传输等功能;

2 成像软件设计

成像系统软件采用FPGA实现。软件核心是图像处理单元。该单元接收CCD行同步信号以及指令,完成数据处理功能;

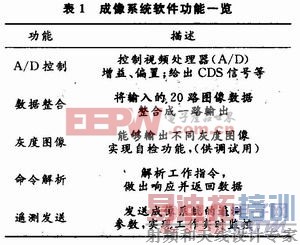

成像系统FPGA的主要功能如表1所示。成像系统在物理上分为3个电箱。图像处理电箱独立存在,并接收焦平面电箱的视频信号和控制电箱工作指令,实现数据处理。根据系统逻辑功能划分FPGA软件结构,并将软件设计规范应用其中,优化系统性能。图像处理单元工作频率高,数据处理复杂,不同的结构划分和设计方式对性能影响较大,因此,本文对图像处理软件设计进行详细阐述。

[p]

2.1 FPGA软件设计分析

可编程逻辑设计原则的合理应用,为理解FPGA程序设计,实现高效、稳定的数字系统提供了条件。

(1)资源与速率的平衡。资源和速率是FPGA设计的重要指标。通过合理的软件结构划分,在高速数据处理区域采用速度优先方法,即通过模块复用、串/并转换、数据流水化等方法实现高速数据传输;在低速处理区域,采用串行方式和组合逻辑,通过增加扇出实现资源的最优化。

(2)系统与硬件匹配。FPGA内部硬件资源决定设计的结构和方法。采用BLOCK RAM或Distributed RAM,根据数据处理内容、资源利用率要求决定使用方式;另外,利用全局信号线,实现全局变量处理;利用FPGA内部IP和原语实现程序设计,改善程序架构。

(3)同步设计。同步设计是资源与速度的体现,在异步时钟域数据处理时,采用FIFO转存,解决同频异相或异频问题,实现数据读取和传输。

(4)可靠性设计。软件设计采用冗余和容错性设计、简化设计规模和减少软件配置项;

2.2 图像数据处理与分析

2.2.1 数据率和时钟选择

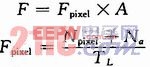

CCD图像输出数据率计算如下:

式中:F为输出数据率;Fpixel为CCD像元转移速率;A为量化等级;Npixel为像元数;Na为哑像元数;TL为行周期。根据指标计算,成像系统的数据率达到1 Gb/s以上,因此,数据传输采用10 b数据并行方式,满足软硬件设计预定的指标要求。

2.2.2 时钟域分析

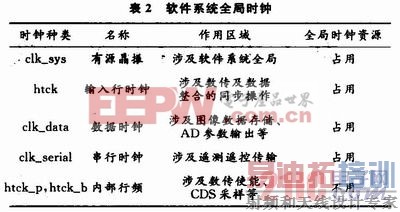

CCD图像处理单元,主时钟采用120 MHz有源晶振(elk_sys),通过FPGA内部全局时钟网络(BUFG)实现全局走线;设计时不建议使用DCM。系统的主要时钟如表2所示。

系统接收外部行同步时钟,通过高频主时钟同步,并在FPGA内产生内部行频,用于产生CDS信号及控制逻辑。通过分频产生串行时钟,完成遥控遥测信号的收发;产生数据时钟,完成数据采样和传输;

2.2.3 成像系统软件结构及功能实现

根据软件系统功能,自顶向下划分模块,如图2所示。为了保证模块间信号的独立性,增强了模块解耦处理,具体的处理原则是:减少模块IO数量,减少逻辑关联程度,避免信号控制环路产生;存储器与后续数据处理操作整合;模块间避免数据传输,减少异步时钟域的数据同步问题;采用脉冲电平逻辑实现模块控制等。由于合理划分了软件模块,方便了模块化设计和仿真验证,为后续的工作奠定了坚实的基础。图2中三级模块没有具体给出。

[p]

(1)数据解析模块。通过RS 422解析串行指令,同时完成部分硬指令翻译,并根据指令要求发送系统遥测参数。串行接收数据采用累加校验,并对接收数据进行预存储。校验正确后,将数据以乒乓方式存入RAM,以保证读/写逻辑不冲突;校验错误时,不转存数据。根据不同的指令类型,对相应的地址进行读/写操作,更新完毕后给出标志位。

(2)视频控制模块。输出A/D参数、CDS信号和A/D输出时钟。A/D参数采用广播方式,通过使能信号完成20路AD的配置;由外行信号htck同步A/D的控制逻辑以及CDS信号;由于数据处理速度较低,实现时,通过增加扇出、减少模块复用,来降低资源利用率。CDS采样脉冲的位置对信号质量影响很大,需要精细调节。在设计时,采用FPGA内部移位寄存器生成不同位置的采样脉冲,在调试中实现精确对准。

(3)数据整合模块。将输入的20路图像数据整合一路输出。根据工作指令选择灰度图像或实时图像,并行存储到相应的fifo中;输出时,通过控制读使能信号,实现数据的循环读取。设计FIFO时,仍然采用乒乓方式,通过标志信号使读写逻辑分离。相比RAM设计而言,避免了大规模地址线造成的亚稳态问题,设计时序相对简单。

(4)数据输出模块。根据卫星指令将图像数据按照规定格式输出。设计时,需要注意数传协议中各数据段数据的输出时序。因此,良好的模块规划,更有利于程序的实现和验证。

2.3 性能与设计要点

(1)FPGA内部时钟域分析有利于同步设计的实现,在良好的时钟分配下,能够提高系统运行频率,增加软件可靠性。根据FPGA资源说明,每个slice有固定数量的触发器和查找表(LUT)资源,合理利用可以降低器件资源的利用率。

(2)组合逻辑容易产生亚稳态,为系统带来不确定因素,同时,组合逻辑延时也限制了系统的运行频率。在频率要求较高的模块内部,可以采用流水线技术降低组合逻辑规模。

(3)软件结构对系统性能和资源使用有很大的影响;不合理的结构划分不仅浪费资源,也不利于软件的升级和维护。该软件通过合理的结构和接口信号划分,力求达到模块解耦的目的。通过详细的接口时序说明,可以更好的进行软件维护和更新,为后续开发奠定基础。

2.4 关于软件系统工作频率和硬件速度的匹配

电路设计时,通过分析硬件电路的芯片参数和电路延时指导软件设计。对于关键信号走线,除了可以在硬件上设置延时线外,FPGA内部可以通过DLL倍频时钟,通过时钟计数方式实现延时,或者通过FPGA内部LUT和门逻辑实现组合逻辑延时设计。由于FPGA的端口速率有限,不同等级的FPGA芯片的处理速度也不同,因此,需要参考FPGA的参数特性设计系统结构,并确定端口数传规则和内部结构,同时,注意与外围

硬件的匹配,以保证软硬件可靠运行。

3 实时图像效果评估

图3给出了实验室条件下的原始数据图像。通过调整信号处理器的增益,调整相应抽头的灰度值,从而达到灰度均衡效果;通过观察相应的图像数据可以得出,数据处理和成像效果达到预定指标要求。

4 结语

FPGA成像软件是系统可靠运行的重要保障,其性能对整体分辨率的提高有着举足轻重的作用。在给定的硬件条件下,通过高效设计FPGA软件,能够显著提高系统性能。在成像软件的数据处理方法上,仍然有很多方向,如实时图像压缩传感,提高系统的传输能力;在FPGA内部进行海量数据处理等。通过实验证明,该软件的实际运行速度达到要求。因为硬件处理速度的限制,若想提高软件运行频率,寻求更加合理的软件系统结构以及电子学分系统结构将成为重要的研究内容。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于OPNET的SCPS-NP协议仿真设计

下一篇:开关电源设计中如何减小EMI