- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的步进电机控制器研究和实现

摘要:步进电机是一种将电脉冲转化为角位移的执行机构,已广泛应用于各种自动化控制系统中。为了提高对步进电机的细分要求,提出了基于FPGA控制的步进电机控制器方案。给出了用VHDL语言层次化设计各功能模块的过程,利用QuartusⅡ进行仿真,给出了仿真结果,并成功地在FPGA器件上验证了设计的可能性。采用FPGA器件和VHDL语言,只需修改模块程序参数,而无须修改硬件电路就能实现各种控制。该设计硬件结构简单可靠,可根据实践需要灵活方便进行配置。

关键词:步进电机;FGPA;控制器;QuartusⅡ

步进电机是数字控制电机,它将脉冲信号转变成角位移,即给一个脉冲信号,步进电机就转动一个角度,因此非常适合对数字系统的控制。由于工业技术的不断进步,诸如自动化控制、精密机械加工、航空航天技术,以及所有要求高精度定位、自动记录、自动瞄准等的高新技术领域对步进电机的细分要求越来越高。实践证明。步进电机的细分驱动技术可以减小步进电机的步距角,提高电机运行的平稳性,增加控制的灵活性等。采用FPGA控制步进电机,利用其中的EAB可以构成存放电机各相电流所需的控制波形数据表,利用FPGA设计的数字比较器可以同步产生多路PWM电流波形,并对多相步进电机进行灵活控制。当改变控制波形表的数据,增加计数器的位数,提高计数精度后,就可以对

步进电机的步进转角进行任意细分,从而实现步进转角的精确控制。

1 步进电机细分驱动控制器工作原理

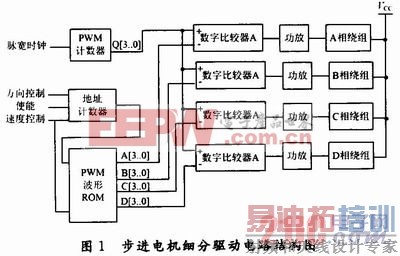

图1是步进电机细分驱动控制器系统框图。该系统由PWM计数器,波形ROM地址计数器,PWM波形ROM存储器、比较器、功放电路等缉成。其中,PWM计数器在脉宽时钟的作用下递增计数,产生阶梯形上升的周期性锯齿波,同时加载到各数字比较器的一端;PWM波形ROM输出的数据A[3..0],B[3..0],C[3..0],D[3..0]分别加载到各数字比较器的另一端。当PWM计数器的计数值小于波形ROM输出的数值时,比较器输出低电平,当PWM计数器的计数值大于波形ROM输出数值时,比较器输出高电平。由此可输出周期性的PWM波形。根据步进电机8细分电流波形的要求,将各个时刻的细分电流波形所对应的数值存放于波形ROM中,波形ROM的地址由地址计数器产生。通过对地址计数器进行控制,可以改变步进电机的旋转方向、转动速度、工作/停止状态。FPGA产生的PWM信号控制各功率管驱动电路的导通和关断,其中PWM信号随ROM数据而变化,改变输出信号的占空比,即可实现限流及细分控制,最终使电机绕组呈现阶梯形变化,从而实现步距细分的目的。输出细分电流信号采用FPGA中LPM_ROM查表法,它是通过在不同地址单元内写入不同的PWM数据,用地址选择来实现不同通电方式下的可变步距细分。

2 步进电机细分驱动控制器的FPGA实现

2.1 系统功能设计

运用自上而下(top-down)的设计思路,将系统按功能逐层分割实现层次化设计。根据步进电机细分控制框图,将该系统分为PWM计数器(CNT8)、地址计数器(CNT24)、DEC2、PWM波形ROM、数字比较器(CMP3)、数据选择器(BUSMUX)6个功能模块,前3个模块用VHDL语言编程描述各模块的接口及电路功能;后3个模块可选择LPM库中的适当模块,并为其设定适当的参数,以满足自己的需要。因而可在自己的项目中十分方便地调用优秀电子工程技术人员的硬件设计成果。

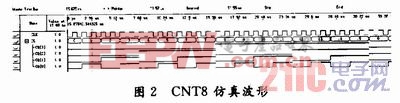

CNT8是PWM计数器,在时钟脉冲作用下递增计数,以产生阶梯形上升的周期性锯齿波,同时加载到四相步进电机各相数字比较器的一端。图2为它的仿真波形。

CNT24是可逆计数器,其U-D端即加减控制端作为控制电机正反转的方向控制端。高电平时计数器加计数,电动机正转;低电平时计数器减计数,电动机反转。计数器的模应该等于电动机运行1个周期的拍数或拍数的整数倍(该处模等于32)。仿真波形如图3所示。

[p]

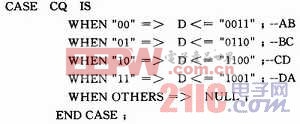

DEC2为无细分时的电机控制模块,控制双四拍时的正反转。

步进电机的正、反转控制可通过改变步进电机各绕组的通电顺序来改变转向,当四相双四拍步进电机的通电顺为AB→BC→CD→DA→AB…时,电机正转;当其绕组按AD→DC→CB→BA→AD…的顺序通电时,电机反转。因此,利用case语句编程来改变输出脉冲的顺序,以此改变步进电机绕组的通电顺序。用‘1’表示该绕组加电;用‘0’表示该绕组断电。

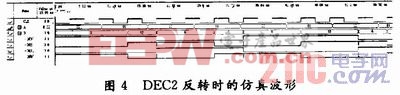

图4为DEC2反转时的仿真波形。

2.2 利用VHDL文件生成元器件

工程创建好以后,就可以用设计好的VHDL语言文件生成工程模块。首先打开CNT8.vhd文件,点击菜单中File→Create/Update→Crea-te Symbol Files forCurrent File命令,以生成图5所示CNT8模块。

按照同样的方法生成CNT24和DEC2模块。将这些模块包装为一个symbol,以备总模块调用,如图5所示。

2.3 原理图输入设计

2.3.1 PWM_1.mif文件的设计

在设计控制器前,必须首先完成存放PWM波形的ROM存储器设计,而在此之前还必须定制LPM_ROM初始化数据文件,如图6所示。

2.3.2 ROM存储器的设计

mif文件建好以后就可以进入ROM存储器的设计。

设计好的rom3模块如图7所示。

2.3.3 定制模块

调用LPM库中的模块,定制BUSMUX(参数化多路数据选择器)元件和lpm_compare0元件。

如图8所示,数据选择器通过模式选择信号,再根据不同的模式功能选择该功能模块的信号输出。该模块的输入信号有模式选择信号sel[0],即非细分控制和模式选择信号sel[1],即细分控制。当sel为“0”时,对应的为非细分控制输出,即由DEC2输出,此时步进电机按照双四拍模式运行;当sel为“1”时,对应的为细分控制输出,即由比较器CMP3输出,此时步进电机按照细分8拍模式运行。[p]

调用LPM库中的模块,定制一个lpm_compare0元件,然后在lpm_compare0的输入/输出端接入输入/输出信号,并将这些模块包装为一个symbol,以备总模块调用,如图9所示。

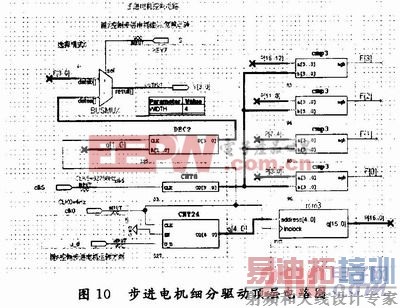

2.3.4 各模块集成

各功能模块设计完成后,用原理图的输入法生成总的功能模块,实现设计功能,最后生成的顶层电路图如图10所示。

3 系统调试

3.1 步进电机总模块时序仿真调试及分析

总模块在QuartusⅡ6.1软件环境下编译通过,再进行总体仿真。

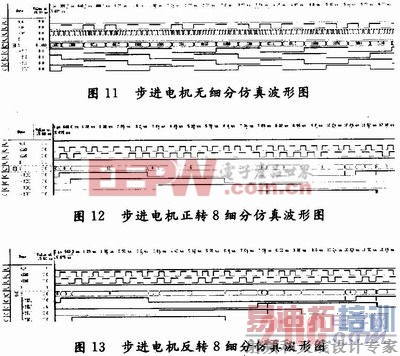

图11中各信号的定义为u_d为步进电机正、反转控制;clock0为步进电机转动速度控制;clock5为PWM计数时钟;s=1为细分;s=0为非细分。Y[3..0]分别对应步进电机的4个相,即DP,CP,BP,AP;s为选择细分控制。

图11给出了步进电机无细分仿真波形图。图12给出了步进电机从A相(1000即8)→AB相(1100即12)→B相(0100即4)→BC相(0110即6)→相C(0010即2)→CD相(0010即3)→D相(0001即1)→DA相(1001即9)→…的工作过程仿真波形。通过图12可以清楚地看到,首先步进电机A相导通,B,C,D相截止;然后B项的数据逐渐增大,从1增大到4,电机中的磁场经过4拍从A相转到了AB相,再经过4拍,A相的数据逐渐减小,电机中的磁场从AB相转到B相。从A到AB再到B共经过了8拍,实现了步距角的8细分。图13给出了步进电机反转8细分仿真波形图。

步进电机的转速取决于输入的脉冲频率。如果给步进电机发一个控制脉冲,它就转一步,再发一个脉冲,它会再转一步。2个脉冲的间隔越短,步进电机转得越快。调整控制器发出的脉冲频率,就可以对步进电机进行调速。从图14可以看出,当改变输入脉冲clock0的周期时,A,B,C,D四相绕组的高低电平宽度将发生变化,它将导致通电和断电的变化速率发生变化,随之使电机转速发生变化。所以调节输入脉冲的周期就可以控制步进电机的运动速度。

由图14与图15的对比可知,通过减少clock0周期,步进电机控制器的运行速度明显加快。通过以上对步进电机的仿真分析可知,该设计实现了对步进电机的各种基本控制。

3.2 下栽到实际FPGA器件上进行工程调试

各模块经过编译优化后,就要选择合适的目标芯片进行综合、管脚配置。该系统选用Altera公司的高性价比Cyclone系列FPGA芯片,型号为EP1C6Q240C8,芯片在32 678 Hz下工作,将实验板GW48-PK3的JTAG PORT接口和下载接口USBBlaster用数据线连接,最后打开板子的电源。

在该硬件环境中,通过键7可以控制步进电机的正、反转,键8可以选择步进电机的细分/非细分功能,这证明该设计完成了步进电机细分驱动控制器的设计要求,最终取得了令人满意的结果。

4 结语

该系统以FPGA为核心部件,根据步进电机的工作原理,利用EDA技术实现了步进电机的细分驱动控制。采用VHDL语言并根据步进电机的不同,改变模块程序的参数,实现不同型号的步进电机控制。在系统设计过程中,力求硬件简单,并充分发挥VHDL语言软件编程灵活方便和FPGA快速的特点来满足系统设计要求,同时大大缩短系统的开发时间和成本。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...