- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的IRTG-B码编解码器的设计与实现

摘要:为提高整个系统时间的同步精度,以便为测量设备提供可靠的时间信息和标准频率信号,给出了一种基于FPGA的IRIG-B编解码器的设计与实现方法。新系统基于模块化设计,其中编码部分完成标准时间信息及相应的BCD码的产生,并在标准时间BCD码中加入帧开始标志位、位置识别标志和索引标志识别,从而将BCD格式的时间信息变成IRIG-B格式码,同时数据并串处理可通过FPGA的一个I/O端口发送串行数据。解码部分则完成串行IRIG-B格式码的接收并判断帧开始标志位和位置识别标志,再解出相应原始时间信息并存储到双端口的RAM中,最后以并行方式输出。

关键词:IRIG-B;可编程逻辑器件;FPGA;编码器;解码器

0 引言

时间统一(以下简称时统)系统是武器系统试验测试、通信、气象、航天、工业控制、电力系统测量与保护等领域的关键技术,主要为其他参试测试设备提供标准时间信号和标准频率信号。随着现代信息技术的不断发展,对标准化时间系统设备的要求越来越高,IRIG-B码以其优越性成为时间系统设备的首选。而对信号的帧结构的可编程度、集成度的需求越来越高,用于时间系统的IRIG-B码源的设计也趋于高度集成化。FPGA可编程逻辑器件的规模比较大,适合于时序、组合等逻辑电路应用场合,同时具有实时性好、可靠性高、成本低、可编程等优势。本文介绍了采用Ahera公司的EP20K200E器件所设计的IRIG-B时统信号发生及解码电路。

IRIG-B编码模块主要利用外部时钟脉冲信号来触发,它将用于产生IRIG-B码的各种门电路集成在一个芯片,以产生标准的IRIG-B串行时间码并向设备终端发送,从而完成DC码编码。通过设备终端对接收到的IRIG-B码进行解调,便能产生出系统所需的标准时间和各种控制信号,然后再存储到相应的双端口RAM中。

1 系统整体硬件设计

IRIG(Inter-Range Instrumentation Group)是美国靶场司令部委员会的下属机构,称为“靶场时间组”。IRIG-B码(DC)以其实际的优越性能而成为时统设备最佳选择的标准码型。IRIG时间标准有两大类:一类是并行时间码格式,这类码由于是并行格式,传输距离较近,且是二进制,因此远不如串行格式广泛;另一类是串行时间码,共有六种格式,即A、B、D、E、G、H。它们的主要差别是时间码的帧速率不同,B码的主要特点是时帧速率为1帧/s;而且携带信息量大,经译码后可获得1、10、100、1000 c/s的脉冲信号和BCD编码的时间信息及控制功能信息;此外,B码的分辨率高,调制后的B码带宽能适用于远距离传输,它分为直流、交流两种,而且接口标准化,国际通用。

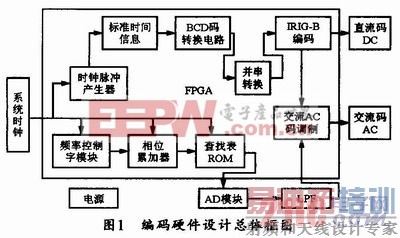

IRIG-B码编码器由时钟脉冲发生器模块、标准时间形成模块、BCD码转换模块、并串转换、直流码形成模块和交流码模块组成,其编码器硬件设计总体框图如图1所示。

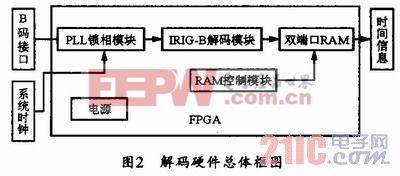

IRIG-B解码器则由锁相环PLL模块、IRIG-B解码模块、双端口RAM、RAM控制模块等组成。其解码硬件的设计框图如图2所示。

[p]

2 IRIG-B编码模块的设计

2.1 时钟脉冲产生模块设计

为了达到系统所要求的精度,使频率较为稳定,设计时可用更高的频率作为时钟分频链的第一主时钟。这里采用锁相环实现倍频方法来提供所需的频率,可选用Quartus II软件中宏功能库中自带的PLL来提高整体的运算速度,同时也能合理的进行资源综合。实事上,使用基本的宏定义模块可以明显地提高用户的设计开发时间。时钟脉冲产生电路是IRIG-B码产生器不可缺少的单元,该电路主要由几个分频器级联和一些逻辑门组成。

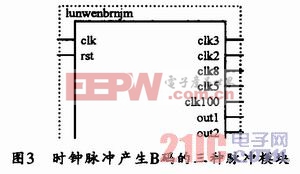

电路中的数字分频器可对外部提供的频率进行分频,以产生系统所需时序脉冲和B码的三种基本编码形式脉冲,其宽度(高电平)分别为2ms、5 ms、8 ms,频率为100Hz的脉冲信号:其中第一种是高电平为2 ms、低电平为8 ms的脉冲(代表逻辑“0”);第二种是高、低电平均为5 ms的脉冲(代表逻辑“1”);第三种是高电平为8ms、低电平为2 ms的脉冲(作为位置识别标志和参考码元)。Quartus II软件下的仿真模块结果如图3所示。

2.2 标准时间信息和BCD码转换模块设计

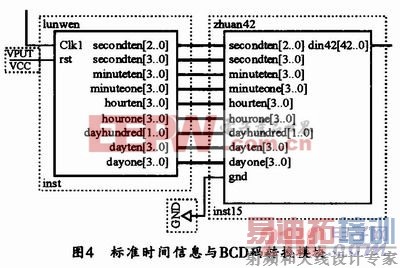

该模块由百分秒计数器、秒计数器、分计数器、时计数器和天计数器级连而成。它可对预置的时间进行秒加一,每隔一秒对时间信息刷新一次,从而形成动态BCD码,并使时间信息符合IRIG-B码的格式。标准时间信息和BCD码转换模块如图4所示。

2.3 IRIG-B码DC格式的生成

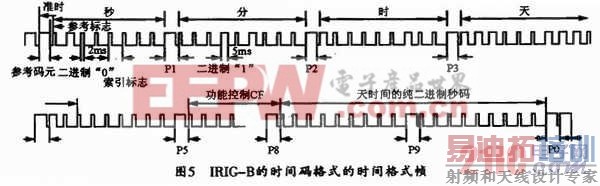

IRIG-B(DC)时间码格式的时间格式帧从帧参考标志开始,因此,连续两个8ms宽脉冲中的第二个8ms脉冲的前沿为秒的准时点,该点标志着一个时间格式帧的开始,称为参考码元。从第二个8ms开始,分别为第1、2、…、99、0个码元。B码时间格式中含有秒、分、时、天等信息,其位置在P0~P5间。时间信息中,高电平用5ms脉冲表示,低电平用2 ms脉冲表示,其中秒信息占用第2、3、4、5、7、8、9码元;分信息占用第11、12、13、14、16、17码元;时信息占用第20、21、22、24、26、27码元;天信息占用第31、32、33、34、36、37、38、38、41、42码元;P6~P10包含其他控制信息(这里没有应用)。另外,第6、15、25、35、…、95码元为索引标志,用2ms脉冲宽度表示,固定为“0”。时、分、秒均用相应BCD码表示,低位在前,高位在后,个位在前,十位、百位在后。图5所示是IRIG-B时间码的格式帧示意图。

[p]

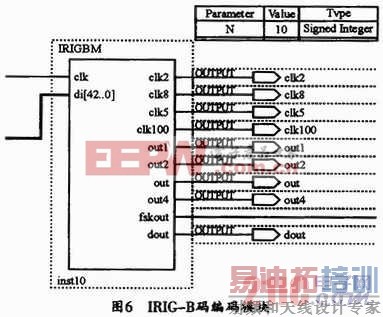

一般每个IRIG-B码都包含有丰富的码信息。它必须包含帧开始标志位、位置识别标志和索引标志,以使接受方能进行数据卸载,或通过位置识别标志和索引标志识别出相应的天、时、分、秒等信息。图6所示是IRIG-B码编码模块的设计图。

3 IRRIG-B解码模块设计

3.1 锁相环PLL模块

PLL锁相环模块用于实现系统同步功能,以使外部信号脉冲和提供的标准时钟脉冲相位同步,从而实现输入信号频率对标准信号频率的自动跟踪。PLL主要由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)等三个基本部件组成。本文选用Ouartus II软件中宏功能库中自带的PIX模块来实现其相位同步功能。

3.2 IRIG-B解码模块

对IRIG-B码进行解码就是将B中包含的标准时间信号和天、时、分、秒信息提取出来。解码的关键在于判别IRIG-B码的帧开始标志位和相应的秒、时、分、天的位置和信息。通过检测B码中各个码元的宽度(高电平),可以判断相应的时间信息。该模块可完成对IRIG-B码的宽度检测。如果宽度为8,则确定是位置识别标志,如果检测到两个连续的宽度都是8,第二个宽度为8的脉冲则作为帧开始标志位。如果宽度为5,则对应的数值为“1”,如果宽度为2,则对应的数值为“0”。

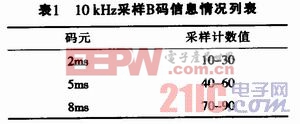

本设计采用10 kHz基准信号来采样IRIG-B码信号以提取码元相关信息。由于10kHz与外部频率脉冲不能完全同步,有一定时间误差。所以,利用10 kHz脉冲信号来采样B码信号,可使三种码元不会出现重叠,从而可以提高采样精度。在捕获方式下,当满足捕获条件时,硬件可自动将计数器中的数据写入存储器中,当B码信号的上升沿到来时,计数器开始计数,下降沿到来时则停止计数,并通过采样计数数值范围来判断对应的码元,从而将直流码解出。表1所列是用10kHz采样B码的信息表,图7所示是IRIG-B解码模块示意图。

3.3 双端口RAM和控制模块

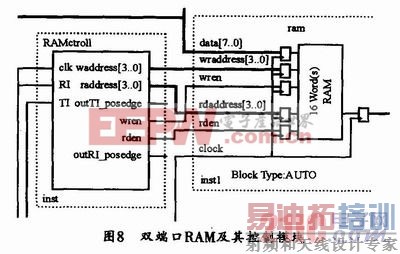

本系统中的RAM模块主要完成时间信息的存储,RAM通过读写控制信号来进行读写控制。当读写信号为高电平时进行写操作,此时可以通过写地址线控制把数据存储到相应的存储单元中;为低电平时则进行读操作,此时可通过读地址线控制把相应存储单元的数据读出。从而完成整个数据存储的读取,图8所示是该双端口RAM和控制模块的示意图。

4 结束语

基于FPGA的IRIG-B码编解码器有利于硬件电路的简化并缩短开发周期,同时其工作稳定,可靠性高,可提供精确时间信息,在工程实践中得到日益广泛的应用。本系统采用模块化设计,其系统的各个模块之间有较好的关联性,又有一定的独立性,便于后期对系统功能的扩展。当以串行方式进行数据传输,用一个I/O端口即可完成数据的接收和发送,因而既节省系统资源,又可解决并行传输通道之间的相互干扰问题。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...