- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的IEEE 1394b高速数据传输系统

摘要:介绍了IEEE 1394h串行总线的特点,并以FPGA嵌入式处理器Nios II为控制核心,设计实现了一种1394b高速数据传输系统。阐述了该系统的硬件设计和软件工作流程。实验表明,该系统可靠性高、实时性好、具有广泛的应用价值。

关键词:IEEE 1394b;串行总线;FPGA;Nios II

随着信息技术的迅速发展,计算机的速度不断提高,外部设备的速度也随之提高。常用串行总线,如USB2.0总线最高速率为480 Mb·s-1,IEEE 1394a总线最高速率为400 Mb·s-1,但在有些情况下难以满足高带宽和实时性的要求,成为系统性能进一步提升的瓶颈。IEEE 1394 b-2002正是在这种情况下应运而生,它最高支持800 Mb·s-1的总线传输速率,最多可支持63个节点,最大传输距离100 m,支持即插即用、等时和异步传输,并且向下完全兼容IEEE 1394a的设备。1394b串行总线可以应用在众多的领域中,无论是在视频传输还是计算机外设、网络互连等方面都有着巨大的市场潜力。具有相同功能的1394b产品,比普通计算机配套设备便宜,具有更好的可扩展性和竞争力。

1 系统的硬件设计及仿真

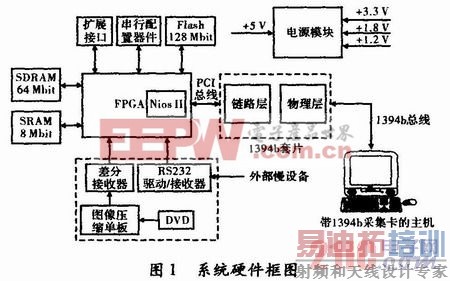

系统硬件设计框图如图1所示。根据用户需求,该系统以FPGA为单板控制核心,外部慢设备的控制或状态信号通过RS-232总线发送到FP-GA内部的相应接收模块。这些慢设备发送的数据信息量不大,但要求准确无误的传送到主机端显示,所以这些数据在1394b总线上采用了异步传输的方式。除慢设备外,系统单板还通过RS-422差分接收器接收两路压缩后的DVD视频图像数据。这些图像数据通过等时传输的方式不间断的发送到主机上,经过解压缩进行实时播放。系统单板上还留有一些扩展接口,用于功能扩展。

综合考虑系统的功能需求及实现的复杂度,FPGA采用了Altera公司Cyclone II系列的EP2C70F67216。这款FPGA具有68 416个逻辑单元,422个用户I/O管脚,I/O标准支持3.3 V PCI,可以通过IP核实现主从模式的PCI接口。在系统中FPGA主要完成:(1)异步与等时数据的接收。(2)数据拼接与数据缓存。(3)外部SRAM的控制,实现大量数据的片外缓存。(4)与链路层控制器间的PCI接口时序控制。(5)与Nios II软核之间的接口模块。

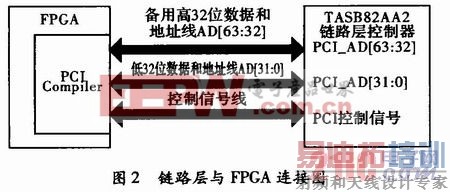

链路层控制器TSB82AA2通过PCI总线与FPGA相连,PCI接口的时序较复杂,本设计采用了FPGA内部的IP核PCI_Compiler来实现PCI主从传输模式。链路层控制器与FPGA的连接关系如图2所示。在SOPC Builder开发环境中,只需要设置相应的参数,就可以实现PCI总线与FPGA内部Av-alon总线之间的数据交换。需要注意的是,在生成硬件网表前需要加入IP核有关文件中提供的PCI约束信息,并按照约束文件的要求锁定管脚。

[p]

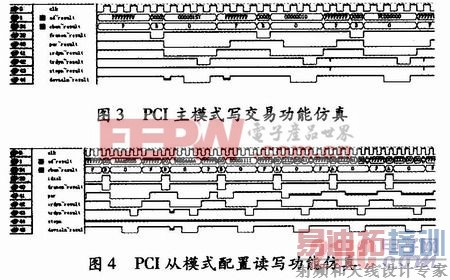

当FPGA为PCI主设备时,它通过PCI-Avalon桥发起PCI主传输,如图3所示是PCI主模式写交易的仿真时序。当FPGA为PCI从设备时,链路层控制器是PCI命令的发起者,并由PCI-Avalon桥自动进行分析,将PCI总线上的命令转化为相应的Avalon总线信息,图4所示是PCI从模式配置读写仿真图。

2 嵌入式软核Nios ll的设计

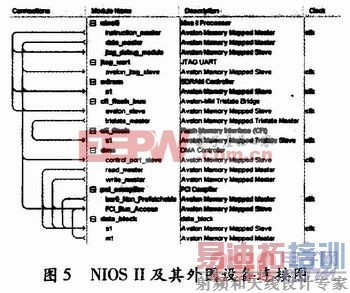

Nios II是Ahera推出的32位RSIC嵌入式处理器,根据用户的需求有Nios II/f(快速)、Nios II/s(标准)以及Nios II/e(经济)3种可配置的方案。Nios II还支持片内调试和指令定制,具有较大的灵活性和可扩展性,而且许多常用的标准外设接口已经以IP核的形式集成在了SOPC Builder开发环境中,用户如需要则可直接调用,缩短了开发周期和成本。根据应用需要,本系统将Nios II配置成快速型,时钟频率为100 MHz。Nios II与各种外设通过Avalon总线连接,具体的连接关系如图5所示。

[p]

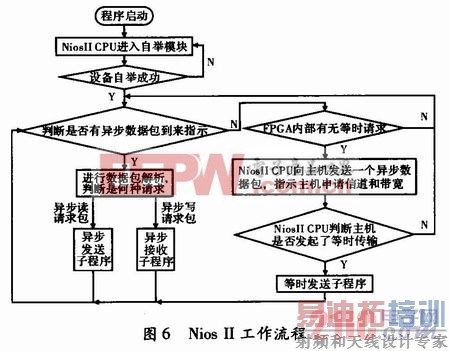

本系统中Nios II主要完成3个功能:(1)实现1394b设备的自举,协助主机完成设备识别以及设备的身份确认。(2)实现异步数据收发功能,异步读、异步写,根据请求包的类型进行分别处理。(3)满足传输条件时,为等时传输申请等时信道和带宽,成功后开始组织等时传输,传输结束后释放信道和带宽。图6为Nios II工作流程图。

下面介绍等时传输过程,根据系统设计,将外部DVD压缩图像数据作为等时数据来处理。具体过程如下:

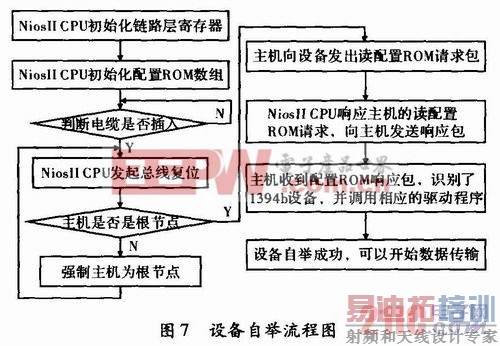

(1)NioslI CPU对1394b的OHCI和链路层寄存器进行初始化,判断线缆是否插入,强制根节点,直到设备完成自举,节点的身份确认,如图7所示。

(2)自举过程结束后,Nios II CPU检测等时传输的条件是否满足,如果满足则向主机发出申请,申请等时信道和带宽。

(3)申请成功后,Nios II CPU开始组织数据进行传输。首先它向DMA控制器发送寄存器配置信息,从而将数据传送任务交由DMA控制器完成。

(4)DMA控制器从FPGA的缓存单元中取出数据,并添加包头将数据拼接成合法的等时数据包格式,并发起PCI主模式传输。

(5)数据经由PCI总线传送到链路层芯片中,又通过物理层芯片传送到1394b总线上,并由主机上连接的数据采集卡接收,最终由主机端的应用程序解压缩和播放数据。

3 结束语

文中介绍了一种基于FPGA的IEEE 1394b高速数据传输系统,它能实现外部多路数据的实时传送。由于支持1394b的设备与支持1394a的设备可以相互兼容,所以在此基础上可以建立1394组网平台,实现多个系统的互联与传输。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...