- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA高速并行采样技术的研究

摘要:介绍一种基于四通道ADC的高速交错采样设计方法以及在FPGA平台上的实现。着重阐述四通道高速采样时钟的设计与实现、高速数据的同步接收以及采样数据的校正算法。实验及仿真结果表明,同步数据采集的结构设计和预处理算法,能良好抑制并行ADC输出信号因相位偏移、时钟抖动等造成的失配误差。

关键词:交错采样;高速采样时钟;同步接收;信号处理

0 引言

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高采样率需要高速的模/数转换器(ADC)。目前市场上单片高速ADC的价格昂贵,分辨率较低,且采用单片超高速ADC实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

利用时间交叉采样原理,对同一信号用多个相对较低速的ADC并行采样是可行的。本文针对某项目要求构建了四路采样率为400 MHz的ADC和高性能FPGA接口处理平台,实现1.6 GHz数据采集。着重讨论了ADC采样时钟的设计、数据同步接收和校正预处理等关键技术,并提出软硬件优化方案。

1 采样系统设计

1.1 多ADC并行采样原理

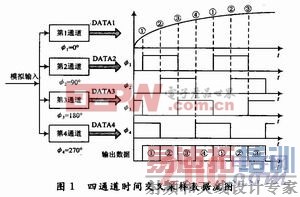

时间交叉采样原理基于使用多片相对低速的并行ADC实现高速数据采集。m路ADC中每一片ADC的采样频率是整个系统采样频率的1/m,通过算法调整可使每一路通道时钟具有固定相位差,采样数据经多路排序合并后,可达到一路ADC采样速率m倍的效果。图1是四路采样时序结构,理想条件下各路时钟相位依次相差90°。

1.2 时钟设计

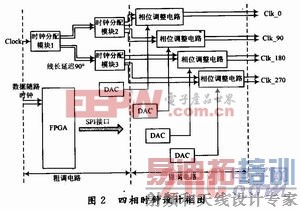

外部时钟信号经“时钟分配模块1”转换成两路同相差分时钟信号,一路送“时钟分配模块2”,另一路经PCB走线移相90°后送“时钟分配模块3”。模块2,3各输出两路180°相差时钟信号,最终得到依次相差近似90°的四路ADC采样时钟。

四路时钟信号并非严格均匀相差90°,各路独立进入“相位调整电路”微调。相位微调电路由可编程移相LC网络组成,FPGA独立控制四路调整电路,使相位时延控制在200~300 ps范围。时钟分配及调整电路结构如图2所示。

[p]

1.3 数据接收和存储

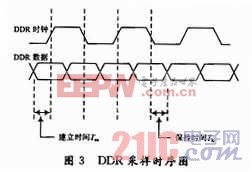

ADC输出数据速率为400 MHz,与之相对应的随路时钟为200 MHz,利用DDR方式接收数据。FPGA内部PLL产生的四路时钟信号的上升沿和下降沿都对输入数据进行实时采样,数据与采样时钟之间保持一定的相位差,以满足同步时序的数据建立时间(Tsu)和保持时间(Th),如图3所示。

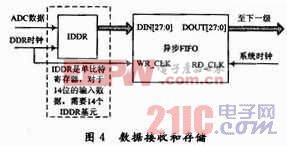

通过FPGA输入模块IDDR映射生成内部寄存器接收数据,并由异步FIFO实现内部时序同步和存储。ADC采样数据的有效位是14 b,利用FPGA软核生成的FIFO宽度和深度可分别设置为28 b和128,其中高14位[27:14]存储奇数时刻的采样数据,低14位[13:0]存储偶数时刻的采样数据,数据存储如图4所示。

2 数据预处理

2.1 时间交叉采样引起的误差

在图1所示的多通道并行时间交叉采样的数据采集系统结构中,各个子通道间数据不可能完全匹配,主要会产生三种误差:

(1)由于各个子通道ADC的增益不一致而引起的增益误差(Gain Error);

(2)多相时钟设计不完全理想以及PCB板线路走线延迟不一致引起的采样时刻偏离带来的时间相位误差(Time Skew Error);

(3)各通道ADC基准电压不一致而引起的偏置误差(Offset Error)。

以正弦信号为例,令输入信号S=Acos(2πfint)+θ。其中:A,fin,θ分别为输入信号的幅度、频率和初始相位。若系统总采样率为fs,经m片ADC时间交叉采样后第k个子通道的输出为:

![]()

式中:0≤nN-1,N为每个子通道数据采样点数;gk为第k个子通道的增益;δ为时间误差;σ为偏置误差。[p]

2.2 增益误差的计算和校正

在本文的设计中,经过模拟前端多相时钟电路设计,时间相位误差可以忽略,且ADC的基准电压由同一电源供电,偏置误差也可忽略,在此,利用DFT变换校正增益误差。对于只有增益误差的第k个子通道的输出信号yk(n)=gkAcos[2πfin(mn+k)/fs+θ],做N点DFT得:

,因此,经过增益误差校正输出信号为:

3 实验仿真结果

图5是经过FPGA内部映射之后的时序仿真图,可以看到经过精心设计的多相时钟技术以及合理的同步接收使信号的采集效果良好。

图6是采集得到的数据经过增益误差校正前后的频谱对比图,可以看到在40 MHz处,杂散得到了明显的抑制。其中,模拟输入信号的频率为20 MHz。

4 结语

针对高速并行ADC时间交叉采样技术对多相时钟信号的高要求以及采集数据的误差,介绍了多相时钟设计的一种方法和利用FFT技术实现对增益误差的校正。通过实验仿真证明,该设计能够有效提升数据采集系统的性能。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...