- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于Avalon总线的SD卡读写控制器的设计

0 引言

当前,人们对大数据量的高速存取需求越来越高。SD卡作为新一代数据存储设备,具有大容量,高速度的特点,很好地满足了市场的具体需求,被广泛用于便携式消费类电子设备,例如手机,数码相机、PDA和各种多媒体播放器等。在工业控制领域,同样有大量数据需要采集,存储,分析。而传统用MCU的GPIO模拟SD卡的时序实现读/写调试复杂、读/写速度慢,已经不能符合大多数应用的需求。利用FPGA自身高速并行的特点,开发一种SD卡读写控制器的IP核,不但可以提高性能,而且可以简单实现IP复用,大大提高开发效率,降低成本,具有极大的应用前景。

可编程的片上系统(System on Programmable Chip,SoPC)最先由Altera公司提出,它将尽可能大而完整的电子系统,主要包括NiosⅡ嵌入式处理器、各种硬件接口、数字信号处理系统、普通数字电路逻辑在单一FPGA芯片中实现。SoPC系统中的各个外设通过Avalon总线相连,可简单实现IP复用,因此,系统在开发周期、体积、功耗、功能、产品升级维护等多方面实现最优化,逐渐成为电子产品设计的趋势。

1 Avalon总线简介

Avalon总线是Altera公司专门为SoPC系统指定的一套总线标准,它定义了主从端口对之间通信的信号类型和时序关系。在结构上不同于传统的共享式总线:它在需要连接的每一个主从端口对之间都有点到点的连接,不同的主从端口对之间可以同时进行通信,所以大大提高了系统的性能。Altera一直在致力于为Avalon总线添加一些极其有用高级特性,简化系统设计的同时提高系统的性能。Avalon总线标准也在不断的升级完善,现在已经包含Avalon-MM接口规范和Aval-on-ST接口规范。

在Avalon总线接口的设计中,SoPC Builder提供了直观的图形用户界面,设计人员可以很方便地添加自定义外设,SoPC Builder将自定义外设和其他组件组合起来,生成对这些组件进行例化的单个系统模块,并且自动生成内部总线逻辑,按照设计人员的要求将这些外设与NiosⅡ处理器连接起来,并自动完成外设和存储器的地址映射、中断控制和总线控制等工作。本文主要阐述了SD卡读/写控制器的AvaIon-MM总线接口和SD卡读/写控制逻辑的设计,以圾NiosⅡIDE中读/写控制程序的编写。

2 SD卡的一般读/写过程

SD卡有两种读/写访问模式:SD模式和SPI模式,其中SD模式又分为1 b和4 b两种。由于DE2开发平台硬件上的原因,该设计采用的是1 b的SD模式实现SD卡的读/写。SD卡在上电初期,卡主控通过检测引脚1(DAT3)的电平来决定使用SD模式还是SPI模式。

SD总线上命令和数据的传输从一个起始位开始,以停止位终止。每个时钟周期传输一个命令或数据位。控制器通过CMD信号线发送命令到SD卡,用于对SD卡进行相应的操作,SD卡接收到命令后,会发送相对应的响应给控制器,这些响应中包含了SD卡的一些基本信息和状态信息等。SD卡初始化完成后,进入数据传输阶段,则可以进行读/写操作。为了避免命令,数据和响应传输的错误,SD规范中采用了CRC技术,在传输命令和响应时,需要进行CRC7效验,而在传输数据时,则需要进行CRC16效验。该控制器主要采用SD的CLK,CMD,DAT0三根信号线完成SD卡的读/写。

3 SD卡读写控制器总体工作过程

该控制器采用Verilog HDL语言编写,在SD卡就绪后,NiosⅡ处理器先向Avalon-MM Slave端口设置相关寄存器。状态控制逻辑根据寄存器中的相关位发送命令到读/写控制逻辑,再由读/写控制逻辑发送相应的命令到SD卡。命令在时钟信号CLK的上升沿经过CRC7校验后通过CMD信号线串行写入SD卡。SD规范中定义了很多命令,但这里仅用到了常用的10个命令就实现了读/写控制的功能,命令都要按一定格式顺序发送到SD卡,命令编号占6 b,每个命令必须填充开始标志,命令的参数以及CRC7校验数据以及结束标志,发送1个完整的命令需要写入48b。

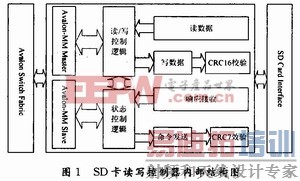

SD卡在接收到命令后,会根据写入的命令执行相应的操作,并发送相应的Response给控制器,其中Re-sponse也分为几种,包含长响应和短响应,Response中的数据包含了卡的一些基本信息以及命令的执行情况等。控制器根据返回的状态的信息决定下一步操作,即发送下一个命令。控制器内部总体结构如图1所示。

控制器上电后自动进行初始化,将SD卡的状态保存到状态寄存器中,在进行读/写前,应先读取SD卡的状态信息,在SD卡进入了读/写就绪状态后,即可向Avalon-MM Slave端口写入读/写控制命令,具体包括要读/写的扇区号,读出数据或写入数据的存放地址。控制器在收到开始读/写命令后,开始读/写指定的扇区,控制器一次性读/写512 B,产生一个读/写完成的中断,即可以开始读/写下一个扇区。进行读操作时,控制器将从SD卡读出的数据通过AvaIon-MM Master端口写入所指定的地址处。进行写操作时,控制器通过Avalon-MM Master端口将指定内存地址处的数据写入SD卡。控制器整个读/写过程无需CPU干预,由Master端口主动完成,CPU仅需写入相关控制命令,大大提高了CPU的利用率。[p]

4 Avalon-MM接口设计

为了实现数据在Avalon总线上的传输,必须实现Avalon总线相关信号和时序逻辑,主要包括数据、地址、读/写控制、中断、时钟复位等信号。

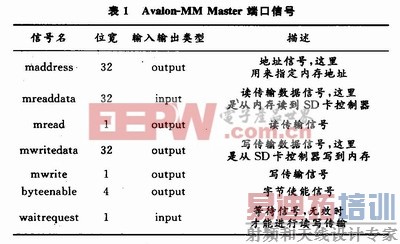

Avalon-MM Master端口主要用来将读/写控制逻辑部分读到的数据写入内存,或者将内存中的数据写入读/写控制逻辑,其接口信号如表1所示。

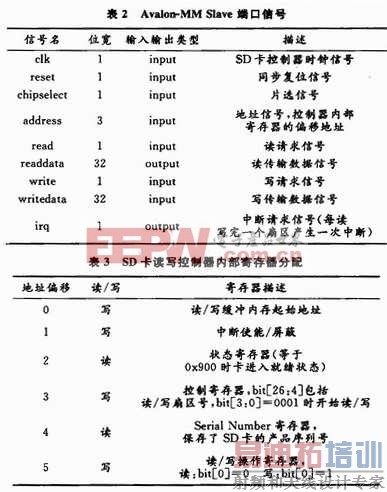

Avalon-MM SIave端口主要用来接收相关控制命令,即通过这个端口实现控制器内部寄存器的访问,其接口信号如表2所示。

该控制器内部有6个寄存器,也可以根据需要实现更多,通过软件设置相关寄存器即可进行读/写SD卡的操作,寄存器功能描述如表3所示。

[p]

5 系统硬件设计

为了验证SD卡读写控制器,在DE2开发平台上搭建了最基本的硬件系统,主要包括:NiosⅡ处理器,PLL锁相环,片上RAM,JTAG UART和自定义的SD卡读写控制器。NiosⅡ作为系统主控制器,PLL用来产生SD卡读/写所需的时钟信号,片上RAM用来存储代码和数据,JTAG UART主要用来调试,打印数据到控制台验证写入的数据和读出的数据是否相同。

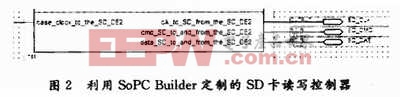

硬件系统的建立主要利用Altera公司QuartusⅡ开发工具以及其集成的SoPC Builder完成的,关键在于如何用SoPC Builder将SD卡读写控制器添加到元件列表中。在SoPC Builder提供的图形化的界面下,添加控制器Verilog源程序后,设置控制器中各信号在Avalon-MM总线中的信号类型等,图2即为添加好的SD卡读写控制器。

图2中,各引脚的描述如下:

base_clock:控制器输入时钟,该设计采用PLL产生的25MHz时钟信号;

clk_to_SD:SD卡时钟信号输入;

cmd_SD:SD卡命令,响应输入/输出信号;

data_SD:SD卡数据信号。

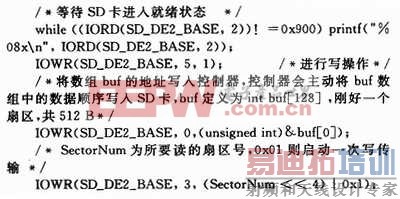

根据SD控制器的寄存器映射,在Nios IDE中编写C程序控制SD卡控制器进行读/写操作,下面代码为写SD卡的一段程序,读SD卡的的过程与其类似。

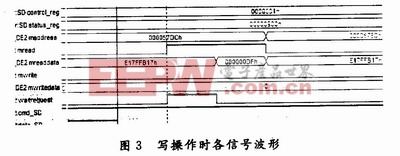

读/写完一个扇区后,控制器会产生一个中断,此时即可进行下一次读/写操作。由于SD卡读/写有比较复杂的时序要求,命令、响应众多,在设计的初期,采用Modelsim做了各方面的功能仿真,功能仿真完成后采用QuartusⅡ自带的SignalTapⅡ逻辑分析仪来测试

分析内部逻辑的工作状态,SignalTapⅡ使用简单方便,更重要的是可以实时观测内部信号变化,而且可以设置触发条件,大大提高了开发的效率。图3是用SignalTapⅡ逻辑分析仪捕捉到的波形。

图3中,status_reg为状态寄存器,00000900表明卡已处于就绪状态,control_reg为控制寄存器,00000001H表明已经开始了一次对扇区0的写传输,mread的上升沿即开始了Master端口的读传输,这里的读指的是将内存中buf数组中的数据读入控制器,再由控制器写入SD卡中,waitrequest为等待信号,高电平时无法进行数据传输,waitrequest无效后可以很明显地看到000000DFH由Master端口读入控制器,再由读写控制逻辑写入SD卡。

6 结语

该设计采用SoPC技术实现了SD卡读写控制器,通过NiosⅡ处理器控制实现了SD卡读/写。由于该控制器根据Avalon接口规范进行开发,可以很方便以IP核的形式集成到其他SoPC系统中,简单实现SD卡的读/写,大大降低了开发成本和难度。本文所设计的SD卡读写控制器还有一大优点就是具有Master端口,可以自主完成数据的读/写,无需CPU的干预,另外采用了中断,降低了响应延时,提高了读/写速率。该设计满足了大部分数据存储需求,适用于工业监测控制,一般消费类电子产品等。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于ADS仿真的X波段二倍频器设计

下一篇:基于FPGA高速并行采样技术的研究