- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADS仿真的X波段二倍频器设计

摘要:利用GaAsFET的非线性特性设计了一个X波段二倍频器,输入频率为6.1~6.3 GHz,输出频率为12.2~12.6 GHz,带宽400 MHz。在理论计算的基础上,结合微波仿真软件ADS对输入匹配电路、输出匹配电路和平行耦合带通滤波器进行了优化设计,最后通过S参数及谐波平衡仿真得到倍频器的各项性能参数。仿真结果表明,该设计完全满足性能指标要求。

关键词:倍频器;ADS;匹配电路;带通滤波器

0 引言

倍频器作为基本的电子部件,被广泛应用于通信、雷达、导弹制导、频率合成器等各种电子设备中。倍频的实现均是以器件的非线性为基础的,倍频电路有效地提取所需的谐波,而将基波和不需要的谐波加以抑制。场效应管(GaAsFET)有源倍频器具有单向性及隔离度好,变频损耗低的优点,同时可以得到较高效率和较宽工作频率,对输入功率要求较低,噪声小,温度稳定性高。

本文介绍了一种基于GaAsFET的X波段二倍频器设计方法。设计时首先根据性能指标要求选择合适的有源器件,确定相应的工作状态、偏置条件及器件的稳定状态,然后合理设计匹配、偏置及滤波电路,最后对整体电路进行优化。设计中采用微波仿真软件ADS对电路进行CAD辅助设计,并给出仿真结果。

1 GaAsFET倍频原理

二倍频器主要考虑的指标为工作频率、带宽及变频损耗,理论上可用各种非线性器件实现倍频,实际常用二极管或三极管倍频,因为此时相对带宽较窄,倍频次数小。相对于二极管和双极晶体管来讲,采用场效应管设计倍频器的突出优点是能在一个宽频带范围内获得倍频增益,并可在输入和输出端之间提供有效的隔离。在考虑成本及各项指标要求后,决定采用变电阻类型的GaAsFET实现,它具有变频损耗低,隔离性好,电路稳定,温度特性好的优点。为了在所要求的频率上实现最小变频损耗,偏置电路和匹配电路的设计非常重要。偏置电路的设计决定了输出频率中含所需频率的谐波成分;匹配滤波电路的设计必须保证在获得所需谐波分量最大的同时,力求无用谐波分量及寄生参量功率达到最小,保证最大输入/输出功率和良好隔离。

FET实现倍频的原因是由于其非线性,主要来自以下几个方面:

(1)栅源和栅漏极非线性电容Cgs和Cgd是外加结电压Vgs和Vgd的函数。

(2)漏极电流Id限幅引起的非线性,即栅极偏置电压接近栅极势垒电压φ,或接近夹断电压Vt时,输入激励电压Vgs瞬时低于Vt或瞬时正向电压高于栅极二极管导通电压时,因截止限幅和饱和限幅作用引起Id的非线性。

(3)Vgs-Id的非线性变换特性,如平方律特性等。

根据FET特性可知,当漏极输出电阻较大时,![]() ,是典型的平方律特性。

,是典型的平方律特性。

(4)输出电导非线性。FET截止型倍频器原理如图1所示,提供合理的偏置电压是非常重要的,它与输出功率、效率和稳定性都有着密不可分的关系。

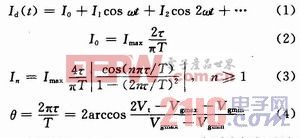

理论上虽然有诸多方法实现倍频,但工程实践表明对于GaAsFET,利用漏极电流Id限幅作用产生的丰富谐波可以实现高的倍频增益,因此主要研究这种倍频机理。与FET放大器理论相同,根据栅极偏压的不同,倍频器工作状态可以分为A类、B类、AB类三种工作状态。其中,A类工作时谐波幅度很小,且直流分量很大,几乎占漏极饱和电流的一半多,故倍频效率很低,不予采用;在B类、AB类工作时漏极输出波形均含有比A类更多的谐波频率分量,因而可采用此类电路实现高效率倍频,其中AB类效率最高,但遗憾的是不能得到偶次谐波,且工作电流大,容易自激。为获得高倍频效率,此处采用B类倍频。使栅极直流偏置电压Ugg始终偏置于夹断电压Vt附近,利用管子的夹断效应使漏极电流Id为尖峰脉冲电流且含有丰富的谐波,此时可以将漏电流波形当作半个余弦脉冲序列处理,如式(1)所示。

式中:Imax为漏极电流峰值;Vgmax,Vgmin分别为栅极饱和电压和反向电压峰值。

从式(3)可知,当n值增大时,Imax减小,所以这种倍频器不能用于高次倍频,但完全满足二倍频。

倍频器的设计与放大器基本相同,不同的只是输出以2ωo代替ωo实现。由于倍频器输出频带要求较窄,相对带宽不到3.5%,输入/输出端采用短截谐振线来实现匹配和谐波抑制。设计的主要工作在于直流工作点的确定,输入/输出匹配电路的设计和输入激励电平的选择。[p]

输入匹配电路的设计主要是使激励源与FET输入阻抗实现共轭匹配,保证激励功率中的基波有效的加到FET输入端,同时抑制其他谐波输入和返回激励源,这也是高功率和高效率输出的基础。在距离FET输入端的输入微带线上并联一条对应2ωo的λ/4开路短截线,用来反射二次谐波信号,使输入电路在二次谐波频率上等效阻抗为0,防止二次谐波泄漏至激励源。输入微带线的长度取为2ωo的λ/2,使对于二次谐波频率而言,输入端始终为短路点,可以减小输入电路变化对输出电路的影响。

输出匹配电路是使输出FET阻抗与谐振回路匹配,以获得最大的倍频功率和转换效率。对于FET,基波输出功率与需要的谐波输出功率相差不大,故二倍频设计对基波功率的抑制尤为重要。在距离FET输出端的输出微带线上并联一条对应ωo的λ/4开路短截线用来反射基波信号,即使输出电路在基波频率上等效阻抗为0,输出微带线的长度取为ωo的λ/2,使对于基波频率而言,输出端始终为短路点,可以减小输出电路变化对输入电路的影响。

偏置电路和隔直电容的设计。偏置电路用以提供倍频器合适的偏置电压,直流工作点不仅直接影响输出功率和效率的高低,而且还密切地关系到倍频电路的稳定性,如果设计不当,甚至可能使倍频器完全不能工作。另外,为防止输入/输出偏置电路形成低频空闲回路,在

输入/输出阻抗部分分别加ωo,2ωo的λ/4高阻抗线,以减小偏置电路引起射频信号的泄漏。设计时还需考虑避免直流偏置电路的电源噪声及电阻噪声混入射频通道影响倍频噪声性能,而且电源纹波及噪声可能恶化相位噪声和杂波抑制指标,电源过冲可能损坏内部电路,应使用低纹波的无过冲电源,且直流供电必须足够大且去耦。同时考虑栅极和漏极偏置电压加电时序,以防器件损坏,此外,还要考虑小的附加损耗、寄生振荡的抑制、独立电源供电、反射等,所有这些都应该在实际的调试过程中得到充分的考虑。

2 二倍频器设计与仿真

2.1 晶体管选择

在倍频器设计过程中首先要选择合适的非线性器件作为倍频器件,器件选择主要考虑以下三点:

(1)要充分利用晶体管工作频率的上限,有利于保持电路稳定性,预防自激。

(2)选择非线性强的管子,根据工作状态和激励功率、输出功率的要求挑选直流参数和极限参数符合要求器件。

(3)对于频率很高时,还需晶体管具有较大的Rds和较小的Cgs。

在电路设计中,设计指标是ADS优化设计的关键,即输出功率、效率、倍频增益、带宽等。在Ku频段倍频增益中,考虑的主要技术指标是稳定性、倍频增益和输出功率,从理论上讲,可以选择双极型晶体管和场效应管,但场效应管相对于双极型晶体管有更高的截止频率,工作状态的稳定性也比双极型晶体管好。综合考虑系统指标要求,此次设计采用NEC公司的GaAs MESFET NE900100实现倍频。

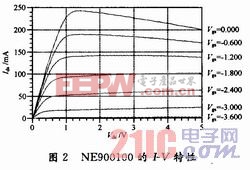

由ADS软件中,由NE900100的等效模型容易得到其I-V特性,如图2所示。从图中可以看出,其固有性能参数如下:夹断电压Vt=-4 V,漏极电流峰值Imax=227 mA,DATASHEET还提供了管子的典型应用状态,Vds=8 V,Idds=90 mA及其小信号S参数。

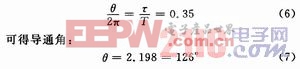

由式(3)可知,对于二次谐波,电流脉冲持续时间的最大值通常选在τ/T=0.35处。由于电流脉冲持续时间与导通角存在如下关系:

![]()

调节漏极电流脉冲持续时间主要反映为栅极偏压的选取,也反映为导通角的选取,即取:

为获得二倍频最大输出功率,选择导通角为126°,对应得到最大二次谐波分量,但同时要注意对基波和三次谐波的抑制。此时主要通过调节栅极偏置来实现短的导通间隔,选择VggVt,使得τ/T=0.35,同时Vgg的选取还必须考虑栅极偏压对峰值反向电压的影响,避免超过击穿电压而损坏管子。[p]

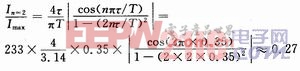

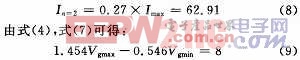

由式(3)得:

计算得漏极电流(单位:mA)输出二次谐波分量的最佳极值为:

结合式(9)及FET特性、约束条件来选择合适的栅极和漏极偏置电压,使得电路能够达到较好的变频性能。

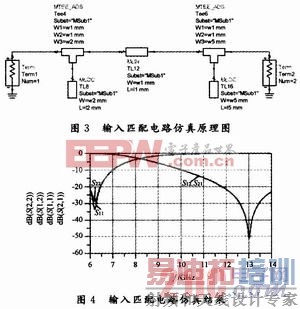

2.2 输入匹配电路设计与优化

通过ADS对输入匹配电路进行优化,如图3所示。将匹配输入端与输出端阻抗分别设为50 Ω及FET输入阻抗的共轭值,通过优化各微带线的长度使匹配电路反射二次谐波信号,而对输入基波信号没有影响,如图4所示,优化后的匹配电路对二次谐波有良好的抑制作用,对于二次谐波S21-27 dB,而在基波处S21-0.1 dB,S11-33 dB,对基波影响很小。

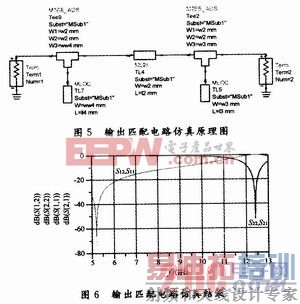

2.3 输出匹配电路设计与优化

输出匹配仿真原理图如图5,将输入阻抗值设置为NE900100的输出阻抗共轭,而终端阻抗值设置为50 Ω,通过优化使匹配电路反射基波信号,而对需要输出的二次谐波信号基本没有影响,优化后的输出匹配电路仿真结果如图6所示,对于基波S21-20 dB,而在二次谐波处S21 -0.01 dB,S11-33 dB,对二次谐波影响很小。

2.4 半波长平行耦合滤波器设计

由于二倍频器输出包含有较丰富的频率分量,为了改善频谱质量,在倍频后须加带通滤波器使输出信号有较好的功率起伏和谐波抑制能力,良好的滤波器是倍频的关键。

根据方案需要,给定二倍频器输出滤波指标如下:中心频率为12.4 GHz;带宽为300 MHz;带内纹波小于0.1 dB;带外衰减大于20 dB(f>12.7 GHz或f12.1 GHz);端接条件是两端均为50 Ω带线。

这里选用半波长平行耦合带通滤波器,它具有半波长开路谐振器平行耦合滤波器和半波长短路谐振器平行耦合滤波器两种对偶形式,其寄生通带中心频率是主通带频率的3倍,不存在表面波,不需要对地连接,在Ku频段具有体积小、重量轻、结构简单等特点。它既适用于窄带设计也适用于宽带设计,但用于宽带时其结构较复杂且需要支撑,对于本文所设计的窄带滤波器,不仅结构简单,而且可采用近似设计方法进行计算。[p]

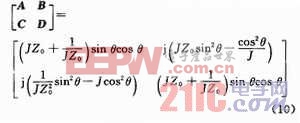

平行耦合滤波器的每一节耦合线电路均可等效为一个导纳倒相器和在两端连接有电长度特性导纳为Yo的传输线组合,这里采用第一种形式耦合电路,其等效电路如图7所示。

分析时采用传输线的A,B,C,D矩阵来计算,导纳倒相器可视为特征阻抗为1/J的1/4波长传输线,故可得出每个耦合电路的等效电路A,B,C,D矩阵如下:

其奇偶模阻抗为:

![]()

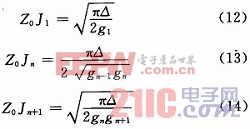

上面是对于单个耦合电路而言,考虑n+1节耦合电路级联组成的带通滤波器,通过单个耦合电路奇偶模阻抗可推得n+1节耦合电路级联带通滤波器的奇偶模特征阻抗如式(12),式(13),式(14)所示。

根据上述公式即可求出n+1节耦合线级联带通滤波器奇偶模特征阻抗,要注意的是其阻带特性不是十分理想,特别是在2ωo的衰减极点处,稍有失谐便可能产生寄生通带,因此设计时必须进行精心仿真和调试。

设计之初要考虑滤波器级数n的选择,因为其选择会直接影响滤波器插损和带外特性,此外还要在分析滤波器通带及带外特性的基础上对滤波器进行理论估算。对于相对带宽较窄时可利用滤波器的近似设计方法来计算其结果,这样处理虽然简化了设计和计算过程,但得到的结果往往存在精度不高的问题。利用先进的ADS仿真软件对其进行正确的建模,可以对理论计算结果反复的仿真和优化,直到结果满足指标为止。

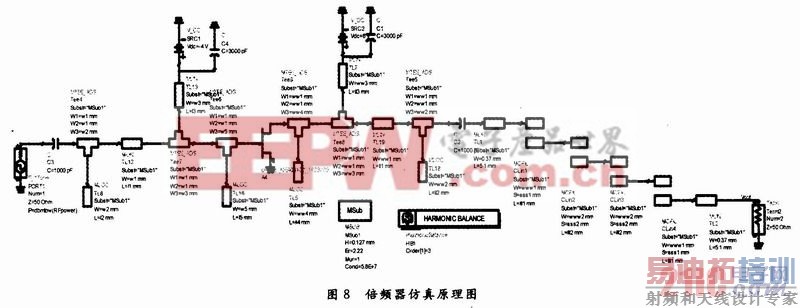

2.5 倍频电路设计与优化

将优化后的参数代入如图8所示的倍频仿真电路,为了便于观察激励电平影响,选用ADS中的单音频率源作为输入端,其阻抗可以人为设定,根据倍频器的外围环境阻抗决定此时阻抗为50 Ω。为保证仿真优化结果接近实际值,必须考虑建模的精确性。比如器件封装的影响,对电路中传输线和匹配网络建模要尽量接近实际,比如重点考虑微带突变节、十字节、开短路短截线的设计。

介质基板材料应选用表面光滑度高、韧性好、硬度高的低损耗微波介质材料,尽量选用小尺寸电路以减小传输线损耗,另外还要考虑所选基板介电常数随环境温度及湿度变化要小,除了考虑基板厚度、相对介电常数以外,还包括介质损耗角正切等参数。综合考虑成本及上述因素后,整个电路制作在介电常数εr=2.22,厚度H=0.127 mm的Rogers RT/duroid 5880基板上。

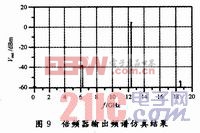

在保证稳定性的前提下仔细设计输入/输出匹配及偏置电路,得到匹配网络初值,再利用ADS的谐波平衡分析方法对电路进行仿真和优化,仿真电路如图8所示。运用软件进行多次的仿真优化来选择合适的激励功率,由于所选GaAsFET工作在1.5~26.5 GHz频段,基波分量仍占主导地位,同时还需进一步滤除无用谐波以得到理想倍频效果。这里主要关心二次谐波输出,由于倍频器产生的谐波幅度并不完全与激励功率成正比,综合考虑倍频损耗及基波、三次谐波的影响,选择最佳变频损耗对应激励功率为10 dBm,中心频点12.4 GHz的仿真优化输出频谱特性如图9所示。从总体仿真结果来看,倍频器可获得理想的变频损耗,同时对于基波和无用谐波的抑制效果良好,符合设计要求。

3 结语

本文讨论了一种GaAsFET倍频器的设计,介绍了设计的具体流程和方法,并充分利用ADS仿真软件对倍频器进行优化设计,省去了复杂的理论分析计算,大大简化了设计过程,对倍频器的CAD设计具有很大的现实意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...