- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于1553B总线协议的解码器设计和FPGA实现

摘要:文章通过对1553B总线协议的研究,结合现代EDA技术,介绍了一种使用现场可编程逻辑器件(FPGA)设计1553B,总线协议用的manches-ter II型码解码器的方法。通过采用Verilog HDL硬件描述语言和原理图混合输入法,使设计简洁有效。通过OuartusII开发软件对设计进行了时序约束和分析,最后给出了时序仿真图,从而证明了这种设计是可行和可靠的。

关键词:1553B总线协议;ManehesterII型码;现场可编程门阵列

0 引言

MIL-STD-1553B是关于数据总线电气特性和协议规范的美国军用标准,它的全称为“飞机内部时分制指令/响应性多路传输数据总线”(Aircraft Internal Time Division Command/Response Multiplex Data Bus),该标准规定了飞机内部数字式的命令/相应时分制多路数据总线的技术要求。

在军用机载数据总线方面,MIL-STD-1553B是应用时间最早,也最为持久的,它为适应工业和军事的需要而提出,具有很高的可靠性和灵活性,加之技术比较成熟,所以应用比较广泛。目前,MIL-STD-1553B已广泛应用于军事、工业和科技领域,从大型运输舰、空间补给站、轰炸机到各种战斗机,以及直升机,都有其应用,它甚至用于导弹系统,以及用作飞行器和导弹之间的基本通信协议。我国于1987年颁布了相应的军标,目前,1553B总线已成为国内军用飞机航电系统的主流数据总线。

本文论述了一种运用Verilog HDL语言,并结合现在EDA技术设计的可靠性强的1553B总线用ManchesterII型码解码器模块。

1 1553B数据格式

1553B数据总线以异步、命令/响应方式执行数据信息的传输,其通信方式采用半双工方式,总线控制器初始化所有个信息位、一个奇偶校验位和3个位长的传输,并控制数据总线上所有数据信息的传输,并控制数据总线上所有数据信息的传输,数据总线上的信息流有信息组成,而信息有三种类型的字组成:命令字、数据字和状态字。有10种信息格式,每个信息格式至少包含两个字,每个字有16的同步头,所有的信息字都采用ManchesterlI型码。

如图1所示,1553B的数据传输速率是1Mbit/s。按照ManchesterII型码规则,将逻辑“0”用编码“01”来表示,其中“0”和“1”各占0.5 μs,也即用一个由低到高的跳变来表示;将逻辑“1”用编码“10”来表示,其中“1”和“0”各占0.5 μs,也即用一个由高到低的跳变来表示。

MIL-STD-1553B总线标准定义了三种字类型:命令字、数据字和状态字。每一种字类型都有唯一的格式,但三种字类型有相同的数据结构,如图2所示。每个字有20比特,最前面三个比特是同步字头,标志新字的开始,同步字头波形是无效的Manchester码,因为其跳变仅仅发生在第二比特时间的正中。使用这种不同的模式,是为了让解码器在每个字的开头重新建立同步,以及保持发送的整体稳定性;接下去的十六比特是信息字段,三种类型的字有不同的含义;最后一个比特是该字的奇偶校验位,标准规定为奇校验。

[p]

2 EDA设计

本文设计的ManchesterII型码解码器选择ALTERA公司的Cyclone系列的EPlC6Q240C6芯片作为目标器件,在QuartusII9.0集成环境中,使用Verilog HDL硬件描述语言和原理图混合输入方法实现,使设计简洁有效。

解码器的功能是将1553B总线中串行输入的数据转变成并行数据,并检查数据和奇偶校验位是否正确,为下游的1553B处理器提供正确的数据。如图3所示,解码器包括同步模块、同步头检出模块、数据处理模块、状态机模块。设计采用16M时钟的工作频率。

数据信号和使能信号可以在时钟信号的一个周期之内的任意时间来领,也就是说无法定位数据信号和使能信号对于时钟信号上升沿的时间间隔,这将使各模块内部的时钟计数器无法准确地计时,使状态机无法准确地进行状态跳变。

同步模块的作用相当于一个D触发器,它可以使数据信号和使能信号相对于时钟信号的上升沿有固定的时间间隔,这个时间间隔就是同步模块的tco,即时钟输出延时。这样就为下游模块的时钟计算和时序约束提供了一个固定的参数,为各模块的时钟计数器准确计时和状态机正确跳变奠定了基础。

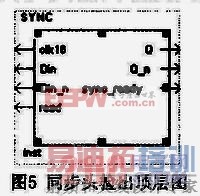

如图4所示,同步模块中Din和Din_n管脚(Din_n为Din的方向输入信号)接收来自1553B模拟收发器的数据信号,read管脚接收模拟收发器发出的使能信号。产生与16MHz时钟的上升沿同步的数据信号和使能信号。

[p]

同步头检出模块是检测1553B三种类型字的同步头。如图2所示,命令字和状态字的同步头是先高电平后低电平,数据字的同步头是先低电平后高电平,三种字的同步头的高低电平各占1.5 μs。在用Verilog HDL硬件描述语言设计中,本文通过设置两个计数器,分别在时钟信号上升沿的时候给高低电平计数,理论上说两个计数器都等于24的时候,同步头才算检出。但是要考虑到tco的影响,设计中当两个计数器到等于22的时候,就说同步头检出,这时产生message ready信号,告诉状态机要开启数据处理模块。如图5所示,是同步头检出顶层图。

数据处理模块是正确解码后面的有效信息位,包括串并转换、数据错误检测、校验位检测。如图6所示,利用把16MHz时钟8分频产生的2MHz的采样信号对总线数据进行采样,可以在每一码位的1/4周期处和3/4周期处采样,这样采样的信号最可靠。当一码位两次采样的值不一样时,就认为数据正确,并将第一次采样的值发送给数据寄存器。如果一码位两次采样的值相等,就认为数据错误,产生数据错误信号dataerror。当数据寄存器的前十六位的和除以2的余数等于第十七的数据时,就认为奇校验正确。否则就认为错误,并产生奇校验错误信号verify_error信号。图7所示为数据处理顶层图。

[p]

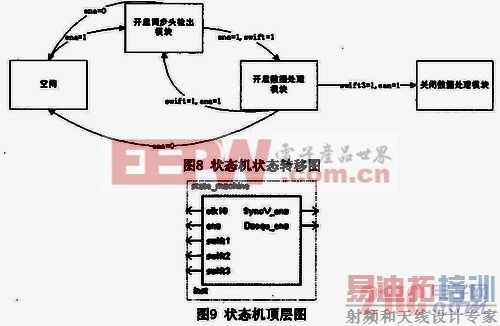

状态机模块是要正确地协调工作同步头检出模块和数据处理模块,如图8所示状态机模块的状态转移图。当状态机被使能时,说明1553B总线数据来临,此时状态机产生SyncV end信号告诉同步头检出模块开始工作。当同步头检出模块工作结束时,产生Sync ready信号,告诉状态机要开启数据处理模快。当数据处理模块工作到一定时间时会产生一个sync head信号,这个信号的意义是要让状态机告诉同步头检出模块开始检测下一个字的同步头。而此时数据处理模块还没有工作完,只有当数据处理模块产生finish信号时,才表示数据处理模块工作完成,告诉状态机关闭数据处理模块。图9所示是状态机顶层图。

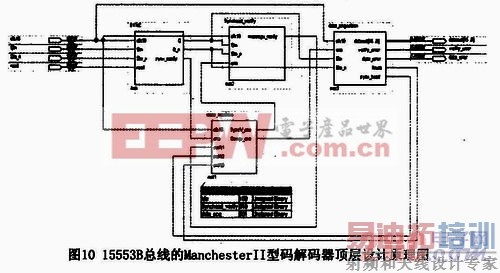

在QuartuslI中的原理图输入界面中,将以上各模块正确地连接在一起,如图10所示为1553B总线的manchesterII型码解码器的顶层设计原理图。

3 时序约束与验证

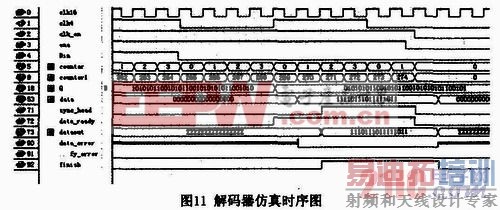

时序约束是FPGA设计中非常重要的环节,只有建立了合理的时序约束,设计才能正常地工作。如今的FPGA中一般都有全铜层的全局时钟驱动网络,本设计中16MHz的时钟设置成全局时钟,可以有效地避免这些时钟信号到达各寄存器时钟短的时钟偏斜。将时钟的最高频率设置成16.8MHz。图11所示为解码器的仿真时序图,解码器在一个字周期之后,解码出数据为1110111011111011。

文章详细介绍了一种利用FPGA实现的1553B总线用的ManchesterlI型码解码器,文章给出了解码器各模块的功能和实现方法,最后给出了顶层设计原理图。给出的仿真时序图证明这是一种可靠的实现方法。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于Cyclone

III

FPGA的DDR2接口设计分析

下一篇:一种基于FPGA核系统的智能429-422信号转换模块的设