- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高性能FPGA中的高速SERDES接口

引言

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代 。起初, SERDES是独立的ASSP或ASIC器件。在过去几年中已经看到有内置SERDES 的FPGA器件系列。这些器件对替代独立的SERDES器件很有吸引力。然而,这些基于SERDES的FPGA往往价格昂贵,因为它们是高端(因而更昂贵) FPGA器件系列的一部分。莱迪思半导体公司在这一领域一直是先驱者,已经推出了两款低成本带有SERDES的 FPGA器件系列,在2007年推出了LatticeECP2M,最近又推出了 LatticeECP3 。ECP2M和ECP3 FPGA为设计者提供了两全其美的产品:一种高性能、低成本具有内置高性能SERDES 的FPGA。这些器件为设计人员提供一个低成本综合平台,以满足他们设计下一代产品的需求。莱迪思还为客户提供了高性能具有SERDES的FPGA器件系列LatticeSC /M,芯片上拥有额外的ASIC IP。

莱迪思的SERDES设计超过了各种常用协议规定的严格的抖动和驱动需求。 LatticeECP2M和LatticeECP3的低成本、高性能带有SERDES功能的FPGA系列为用户设计下一代系统提供了一个很好的平台。器件的一些亮点如下:

- 低功耗:工作于3.2Gbps的速率时,每个通道功耗额定为90mW 。

- 针对芯片至芯片和小型背板(不超过40英寸的FR - 4 ),能可靠传输和恢复串行信号。

- 嵌入式物理编码子层块,支持流行的串行协议,如1吉比特以太网,10吉比特以太网( XAUI )、PCI Express 、Serial RapidIO SMPTE 。

- 支持无线协议,如CPRI 、OBSAI等,包括用于实现多跳的一个低延迟变化选择。

- 灵活的SERDES模块 :多个标准/协议可以混合于单个模块中。

- 针对低成本器件系列,它提供业界领先的结构和IO性能的高性能、低成本、低功耗FPGA 。

- 辅以业界领先的软件,知识产权核和评估平台,能够实施完整的解决方案的设计。

SERDES结构

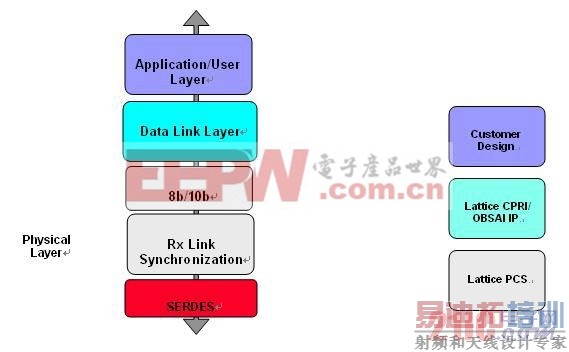

SERDES主要由物理介质相关( PMD)子层、物理媒介附加(PMA)子层和物理编码子层( PCS )所组成。PMD是负责串行信号传输的电气块。PMA负责串化/解串化,PCS负责数据流的编码/解码。在PCS的上面是上层功能。针对FPGA 的SERDES ,PCS提供了ASIC块和FPGA之间的接口边界。

图1 串行协议栈的功能划分[p]

流行的串行协议

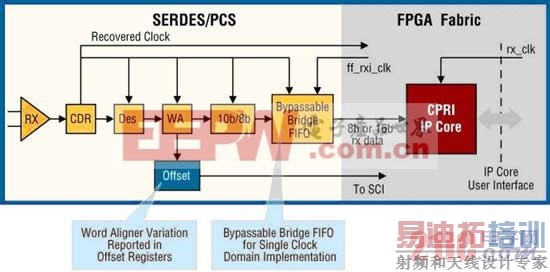

以太网( 1吉比特以太网和10吉比特以太网,或XAUI )和PCI Express是最流行的通信协议。这些协议的每一个都从并行总线接口发展成串行接口,以跟上日益增加的数据传输速率。这些流行的协议共享物理编码子层中的公共块。例如,它们都使用8b/10b编码。 8b/10b编码提供了非常好的直流平衡,最多5个全0或全1并有良好的跳变密度。这些都有助于提高传输的可靠性。如图2所示,在莱迪思的ECP2M和ECP3器件中的嵌入式ASIC模块包含了PMA和PMD以及PCS公共块,例如,链接同步块和8b/10b编码器/解码器。

图2 LatticeECP3支持流行的串行协议

Ethernet

以太网是使用最广泛的通信协议。以太网的数据传输速率已经从10 Mbps发展至100 Mbps,又发展至1吉比特( 1000 Mbps ),继而又发展多吉比特范围: 10 Gbps 、 40 Gbps和100 Gbps。随着数据传输率的发展,链路已经从并行接口(MII、 GMII )发展到串行链路(GE、SGMII 、 XAUI等) 。

LatticeECP3系列完全符合吉比特以太网和10吉比特以太网协议。该SERDES是符合针对1000 BASE-X吉比特以太网的IEEE 802.3z规范和针对10吉比特以太网XAUI 的IEEE 802.3-2005规范。如图2所示,LatticeECP3器件支持嵌入SERDES和其他块的以太网物理层,如链路同步、在器件中8b/10b编码/解码以及时钟容限补偿的ASIC模块。将莱迪思的GE/ SGMII PCS和MAC IP组合在一起时 ,LatticeECP3为用户提供了一个完全集成的、完全兼容吉比特以太网的解决方案。

LatticeECP3 SERDES超过了由IEEE 802.3-2005规范针对XAUI定义的抖动规格。莱迪思的XAUI IP和10吉比特以太网MAC IP内核提供一个完全集成的,完全符合10吉比特以太网的平台。LatticeECP3是完全符合支持1吉比特和10吉比特以太网的业界最低成本的FPGA.

PCI Express

PCI Express是下一代外围组件互连( PCI )标准。该PCI Express协议是为了解决日益增加的带宽需求,通过电缆或针对扩展卡的连接器插槽、提供一个可升级的、芯片之间点对点的串行连接,同时保持与传统的PCI在软件层相兼容。

单个PCI Express串行链路是双单工连接,规定每个链路为2.5Gbps的速率(5Gbps或更高的速率,针对2.0版和以后的规范),可以构成x1、x2、x4、x8 , x12 , x16和x32链路宽度,以实现更大的带宽。串行实现是便宜的,可以进一步推动延伸长度、减轻共模噪声、关注现有源同步并行接口(如常规的PCI )的相偏 ,并减少需要连接通道的总数。LatticeECP3 SERDES完全符合PCI Express 1.1版的抖动规范。与莱迪思的PCI Express端点控制器IP相结合 ,为设计人员提供了一种低成本的PCI Express平台。[p]

莱迪思还为设计人员提供了完整的PCI Express开发套件。如图3所示,莱迪思的PCI Express开发套件是一个完全集成的开发平台,提供了一个完整的硬件/软件开发环境,以加速评估PCI Express技术。该套件包括PCI Express系统设计所需的各种元件,其中包括莱迪思的PCI Express端点IP核、 RTL源代码、项目指南和几个演示文件,从控制到数据的应用、驱动程序、图形用户界面及一块评估电路板。

图3 Lattice PCI Express开发套件

无线协议:CPRI 与 OBSAI

通用公共无线接口( CPRI )和开放基站架构组织( OBSAI等)是针对无线基础设施的两种流行的基于分组的协议标准。LatticeECP3 SERDES也支持这些标准。如图4所示, LatticeECP3 的SERDES /PCS ASIC模块支持CPRI / OBSAI物理层。莱迪思还提供完全支持各自协议栈的CPRI ( 3.0规范)和OBSAI等( OBSAI-RP3 - 01 )的IP核。

图4 用LatticeECP3支持CPRI/OBSAI协议栈

此外, LatticeECP3 SERDES还支持针对实现多跳的低延迟变化要求。在新的远程无线前端(RRH )拓扑结构中,系统要求能够测量和补偿在多跳情况下发生的延迟变化。为了支持这项工作,非常仔细地设计了ECP3 PCS块,使链路延迟变化确定并一致。此外,字对齐延迟变化也是可测量的,一旦知道这个值,在补偿寄存器中就会得到报告,从而可以进行系统级的补偿。

图5 用ECP3的 SERDES/PCS实现短延迟选择

SMPTE

活动图像和电视工程师协会(SMPTE )按照SDI或串行数字接口制定了一套标准。这些标准包括: SMPTE 259M-标准清晰度串行数字接口(SD - SDI)、SMPTE 292M -高清晰度串行数字接口(HD - SDI ) ,以及SMPTE 424M - 3Gbps串行数字接口( 3G-SDI) 。[p]

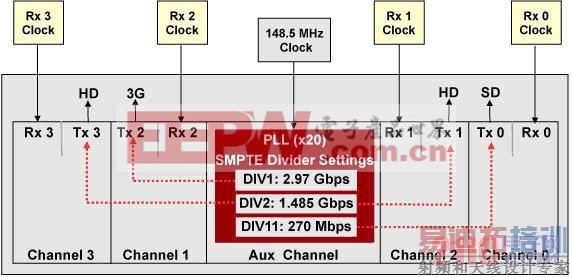

SMPTE 259通过串行链路以270 Mbps的速率传输数据,SMPTE 292的速率增加到1.485 Gbps, SMPTE 424的速率增加到2.97 Gbps。LatticeECP3器件同时动态地支持所有这些速率而无需过采样。LatticeECP3 SERDES是完全符合SMPTE抖动规范的。SERDES IO也可以是直流耦合(用外部电容器)支持SMPTE病态信号。此外, ECP3 SERDES具有通道的独立性。如图6所示,器件包括合适的时钟分频器( DIV1 、DIV2和DIV11 ) ,允许真正实现支持SD/HD/3G的独立多速率传输。每个通道的接收时钟是独立的,可以来自外部源或者来自FPGA,允许独立地支持SD/HD/3G的多速率接收。

图6 用LatticeECP3 SERDES支持增强的SMPTE多速率

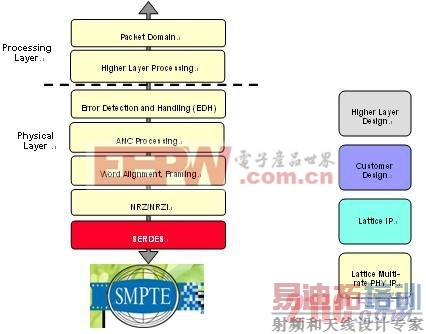

如图7所示,SMPTE协议栈可以完全在LatticeECP3 FPGA中实现。莱迪思提供了一个实现NRZ/ NRZI编码、字对齐和成帧的多速率串行数字接口( SDI )物理层IP核。LatticeECP3是业界成本最低,功耗最低和最灵活的针对SMPTE的可编程开发平台。

图7 用LatticeECP3支持SMPTE协议栈

莱迪思还开发了一个证明符合SMPTE标准的完整的系统。该系统由LatticeECP3视频协议电路板、该IP和演示设计所组成。

结论

SERDES正变成越来越流行的接口,在网络应用方面被广泛地采用。LatticeECP3 带有SERDES功能的FPGA为设计人员开发各种基于SERDES的应用提供了稳健的低成本平台。针对以太网、PCI Express、SMPTE和无线应用,用功能强大的低成本FPGA平台来支持各种通用串行协议

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...