- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

非晶硅反熔丝FPGA提升系统可靠性

现场可编程门阵列(FPGA)技术因其提供的设计灵活性,已为系统设计人员广泛采用。非晶硅反熔丝FPGA技术尤其有用,它可以提供一种高电路密度与低功耗,以及非易失性编程和高可靠性的组合。为了充分发挥其可靠性,FPGA厂商需要考虑反熔丝的崩溃(wear-out)机制,并通过一种设计、测试、软件工具和编程控制的组合来避免崩溃。

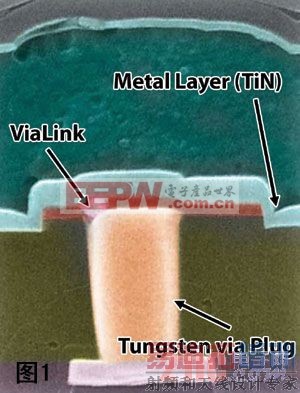

非晶硅反熔丝的最基本要素是利用非晶硅作为一种电介质将两个电极分开(图1)。在一般情况下,这种电介质可表现出GΩ级的阻抗,可有效地隔离电极。不过,在施加一个合适的编程电压和电流时,非晶硅的一个区域会形成一个连接电极的传导通道(<100Ω)。

已编程反熔丝在其工作范围内的表现像一个稳定、可靠的线性电阻器,而且在器件的寿命期间始终可以保持其低阻值。不过,如果已编程反熔丝单元遭损坏,它会呈现一种非线性行为,其电阻就会变得不稳定。一个损坏的已编程反熔丝的阻值可能出现从上百到上万欧姆的变化,当巨大的电流通过它时,还可能从根本上改变其使用寿命期限。

如果所使用的器件包含损坏的反熔丝单元,就可能造成这种不稳定的现场故障。如果反熔丝是用来连接一个高或低逻辑门,那么,损坏的反熔丝仍然会使其门保持在适当的逻辑电平。不过,线路电阻和负载电容具有CMOS逻辑电路的信号传播和切换速度的功能。那么,在一个高速电路中,损坏的反熔丝的不稳定阻值可能引起电路时序的变化。延迟的变化可能从几纳秒到几微秒,从而导致难以诊断的现场故障。

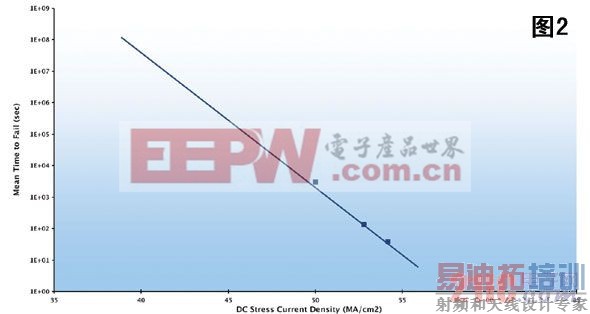

流经反熔丝的过大的工作电流是引起损坏的常见原因。图2所示已编程反熔丝单元的平均故障时间是直流电流密度的函数,即用实际电流除以反熔丝传导路径的截面积。该路径的截面积是编程电流与编程算法,以及编程脉冲的高度、宽度和极性的函数,通常为几百平方纳米。从直流数据显示,增加电流密度流经已编程反熔丝可显著加速故障的出现。这种巨大的依赖性也意味着减少工作电流可以显著延长已编程反熔丝的寿命。

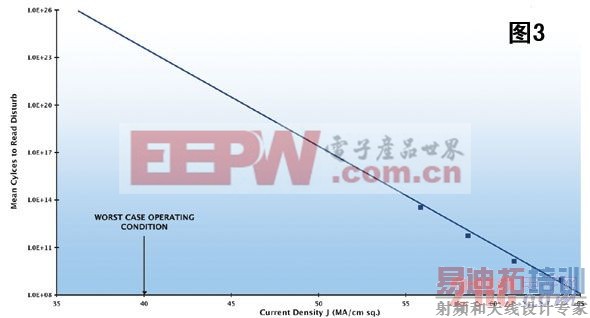

在FPGA的正常工作条件下,不会出现这样的直流电流。通常,一个设计中的已编程反熔丝需要将一个CMOS驱动电路连接到一个容性网络。在这种情况下,只有交流容性电流流过已编程反熔丝。作为开关频率、负载电容、反熔丝电阻和驱动器输出的函数的峰值交流电流,可能对已编程反熔丝造成影响,并导致在使用寿命期限内出现故障。图3所示为在作为电流密度函数的故障发生之前,反熔丝所能保持的时钟周期数,从而显示出对直流电流同样的巨大的依赖性。

控制工作条件,可以充分提高器件的可靠性。除此以外,逻辑设计、设计布线、反熔丝程序排序和测试期间的各种因素都可能影响可靠性。在以下步骤当中适当地小心就可以减少损坏已编程反熔丝的可能性:

● 设计——在逻辑设计期间,遵循一些简单的规则可能有助于通过避免风险处境保证可靠性。防止正常工作过程中反熔丝单元的编程疏忽,例如,避免把反熔丝直接连接到任何外部信号或电源总线上。电源和接地总线的外部信号或瞬变噪声可能在没有编程的和正在编程的反熔丝之间产生过高的电压。

● 制造测试——须在晶圆级对没有编程的反熔丝进行全面测试,以保证它们的编程电压不会过低,并使它们仍然保持其高阻值的非编程状态。在最后测试过程中透过类似的检查,可保证没有编程的反熔丝不会在封装期间受到损坏。晶圆级测试和最后测试应该验证编程电路可以通过适当的电压和电流。最后检查会在编程之前,在编程器里进行,以保证反熔丝不会在最终测试之后损坏。

● 设计布线——设计布线是在创建最后的电路网络,可以依次确定每个已编程反熔丝的有效的下游电容。若电容保持在设置阈值以下将会限制流经已编程反熔丝的峰值交流电流,因此,设计布线软件可以通过限制下游电容来减少在大电流条件下工作的反熔丝单元的数目。对于不同速度的应用,可以选择容性线路更短的布线,或对大的网络进行缓冲来创建更小的容性网络。减少工作在大电流条件下的反熔丝单元的数目可以增加已编程元件的可靠性。

● 反熔丝排序——对已编程反熔丝的状态的控制是一个经常被忽略的步骤。随着器件的编程,网络开始形成。施加到一个网络上的编程脉冲可以对连接到另一个网络的任何反熔丝进行容性编程。所以,反熔丝可能出现损坏,从而导致生产甚至是可靠性方面的问题。时序控制器软件应该可以防止这些情况的发生,并找出一种替代的时序。

● 编程——编程电流的控制对保证反熔丝的可靠性非常关键。可靠性比是由流经一个已编程反熔丝的最差情况下的峰值交流工作电流与用于编程算法的编程电流之间的比率决定的 :

设置这个比率需要充分理解编程算法和建立在反熔丝导电细丝(conductive filament)上的电流的影响。

为了使这个比率得以保持,在对每个反熔丝进行编程时,编程器应该控制其输出的电流。如果每个脉冲期间的编程电流低于设置最小值,元件的编程就会失败。同样,编程电流应该再一次以较低的电压进行测量,以保证已编程反熔丝的IV特性,并使编程路径符合规范。当测量的电流之一超出了该规范的限制时,尽管元件可能发挥适当的作用,但可能使反熔丝连接变得不可靠。通过编程期间对元件的抑制,编程器就可以防止可能出现的现场故障。

将非晶硅FPGA技术与ASIC集成在一起作为嵌入式应用的开发人员,应该保证他们的设计和工具最大限度地减少对已编程反熔丝单元的压力和因此而降低可靠性的可能性。反熔丝技术厂商正在继续努力使人们了解和减少其技术的故障机制。那些与其技术厂商进行密切合作的ASIC设计人员可以利用这种理解创建内部设计规则,以优化基于反熔丝的设计的运行寿命。

使用现有FPGA元件的开发人员可以期待,这些可靠性原则已经融入了反熔丝技术厂商提供的器件设计、布局及布线和编程工具当中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于ANSYS的漏感变压器仿真计算

下一篇:西蒙Z-MAX结构化布线解决方案