- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的实时中值滤波器硬件实现

高清视频监控逐渐成为市场的热点,视频监控不仅要求把现场图像捕获并保存,而且还要尽可能清晰。在高清图像的生成和采集过程中,往往会受到各种噪声的干扰,使高清图像的质量变差,因此必须对图像进行滤波、平滑等预处理来消除噪声。中值滤波作为一种非线性滤波方法,既可以消除随机噪声和脉冲干扰,又可以很大程度地保留图像的边缘信息,得到了广泛的运用。在许多实际应用场合,如高清视频监控、X光图像的降噪等,需要快速且实时地进行中值滤波,软件实现达不到实时处理的要求,因此选用硬件实现。

在硬件实现上,文献[1]、[2]等采用行延迟的方法形成邻域数据,以实现3×3的中值滤波。文献[7]为了提高红外成像跟踪器设计了大窗口的中值滤波器。文献[3]、[4]提出了邻域图像帧存的存储结构,该结构充分利用了图像帧存的数据结构转换特性,并行高速提供邻域图像数据,配以FPGA作为并行处理器,高速实时地实现了中值滤波。但是以上研究都是基于标清图像的中值滤波器,处理的图像大小一般为256×256、512×512的灰度图等,很少有实现高清图像的中值滤波器。本文在文献[3]、[4]的理论基础上,在苏光大主持研制成功的NIPC-3邻域图像并行处理机上实时实现了1 920×1 080×8 bit的高清图像的中值滤波器。该系统的硬件是基于一个标准的PCI板卡,Altera公司的CycloneII FPGA是图像处理系统的核心,此外,该板卡还包括了若干片SRAM、视频采集转换芯片、CPLD和PCI接口芯片。NIPC-3硬件处理的结果由PCI传到计算机做后续处理,是软硬件结合的系统。

1 快速二维中值滤波器算法

本文中值滤波器排序算法用文献[2]提出的快速排序算法。如图1,将3×3窗口内的各个像素分别定义为M11、M12、M13、M21、M22、M23、M31、M32、M33。首先分别对窗口中的每一行计算最大值、中值,最小值不难判断。9个数值中,3个最大值中的最大值和3个最小值中的最小值一定是9个像素中的最大值和最小值;3个中值中的最大值至少大于5个像素:即本行中的最小值和其他2行的中值及最小值;而3个中值中的最小值至少小于5个像素:即本行中的最大值和其他两行中的中值及最小值。最后,比较3个最大值中的最小值Min_of_Max,3个中值中的中值Med_of_Med,3个最小值中的最大值Max_of_Min,得到中间值即为滤波的最后结果Med_of_Nine。

利用这种排序法的中值滤波运算仅需17次比较,且该算法十分适用于在FPGA上做并行处理,大大提高了滤波的速度。

2 FPGA硬件实现

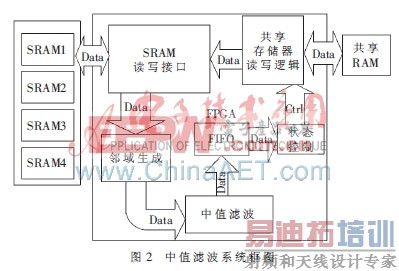

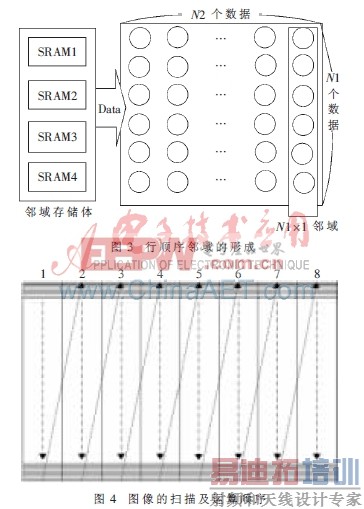

邻域图像并行处理机是一种以邻域图像帧存提供邻域图像数据、以邻域图像处理器并行邻域图像处理的图像并行处理机,其本质是邻域数据(即多数据)的并行处理[4]。中值滤波系统框图如图2所示,主机通过PCI接口将待处理数据写入共享RAM,数据再由共享RAM转入邻域存储体,利用行顺序邻域生成方法[3],将数据由串行转化为并行,实现处理并行,达到数据的高速处理。邻域存储体是由4片SRAM组成,型号是IS61SP6464,位宽为64 bit,一次可以存取8个字节,4片SRAM并行排列,一个时钟周期最多可以吞吐32个字节。见图3,考虑一个N1×1的随机邻域,N2个时钟周期就可以得到N1×N2大小的邻域。然后再将中值滤波模块结果通过FIFO缓存写入共享RAM,传到PC机显示。

[p]

[p]

2.1 分块存储方法和并行运算结构

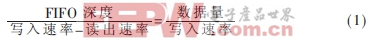

如图4,以256×256大小的图像为例,将其划分为8个256行32列的图像块,中值滤波运算就是按照块的顺序,对每块图像从上到下进行[5]。每一次存储体访问读出一行邻域后,通过流水线队列即可形成n×32的邻域,对于中值滤波算法n为3。为了最大化地提高图像处理速度,采取了32个3×3邻域的并行计算。但是构造32个3×3邻域,需要额外增加2列数据,组成3行34列的运算矩阵。这额外的2列数据正是前一图像块的最右端的2列,为了后续运算的需要,已经保存在RAMa或RAMb中了。RAMa、RAMb的作用是实现乒乓RAM操作,例如向RAMa中写当前图像块的最右端2列时,处理单元同时从RAMb中取出前一个图像块的最右端2列数据参与运算。运算单元架构如图5,这样每一次并行计算就得到了32个8 bit的结果,对应32个结果像素,即图5中的result为256 bit。

2.2 FIFO缓存

共享RAM芯片采用了Cypress公司的CY7C1380,这是一款32 bit位宽、2 MB容量的同步SRAM。因为系统采用流水线结构,一个clk即可产生256 bit的结果,需要写入到32 bit的SRAM,如果不加入缓冲器,必定会有结果数据的丢失,为此,加入一个FIFO,将256 bit结果分8次写入共享RAM,每次写32 bit,这样,FIFO完成了写快读慢的缓冲过程。FIFO的深度取决于需要缓冲的数据量,缓冲的数据量取决于写速率和读速率,见式(1)。

3 FPGA实验结果

图6(a)是从高清摄像机随机采得的带噪图像,从图6(b)可看出本文设计的针对大图像(1 920×1 080)的中值滤波器有较好的去噪效果。

整个电路结构采用Verilog编写,该中值滤波器能达到的最大工作频率为60 MHz,该中值滤波器对如图6所示的1 920×1 080灰度图执行中值滤波的时间约为10 ms,这个速度要比实时快4倍。为了突出本文设计的中值滤波器的性能,本文采用512×512的灰度图做实验。将本文设计的中值滤波器与文献[1]、[3]设计的中值滤波器的性能比较,可以看出,本文设计的中值滤波器的处理速度约为文献[1]方法的8倍,约为文献[3]方法的20倍,如表1所示。

本文针对NIPC-3的特点,用适合并行处理的存储方法,成功实现了1 920×1 080大小图像的实时中值滤波系统。该系统有较好的去噪效果,同时在速度上完全满足实时需要,是一个高速且完整的系统。该系统可以用于高清视频图像的预处理,有很大的实用价值。

参考文献

[1] 石婷,张红雨,黄自立.基于Stratix II EP2S60的改进中值滤波器的设计实现[J].国外电子元器件,2007(1):12-15.

[2] 徐大鹏,李从善.基于FPGA的数字图像中值滤波器设计[J].电子器件,2006,29(4):1114-1117.

[3] 苏光大.实时中值滤波器的实现[J].电视技术,1999(5):25-27.

[4] 苏光大.邻域图像处理机中的新型邻域功能流水线结构[J].电子学报,2000,27(2):1-4.

[5] 刘炯鑫.NIPC-3邻域图像并行处理机的软件设计[D].清华大学电子工程系,2007.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的改进DES算法的实现

下一篇:PCB柔性线路板的挠曲性和剥离强度