- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

LFMCW雷达中频接收机的设计与实现

摘要:针对一种线性调频连续波(LFMCW)雷达系统结构,提出一种中频接收机硬件平台的设计方案。该方案采用AD8347正交解调器做I/O下变频,AD9248模数转换器做采样,EF3C80 FPGA做数字信号处理,PCI9054做PCI接口,并给出了系统软件的设计方法。实现了对线性调频连续波雷达中频信号的接收、处理和存储。通过测试,该接收机能够准确测量出目标信号的频率信息,可为雷达成像提供原始数据。

关键词:线性调频连续波雷达;中频信号接收机;FPGA;PCI

线性调频连续波(LFMCW)雷达具有体积小、重量轻、结构简单、分辨力高和无距离盲区等优点,受相关技术进步和需求的促进,近十多年来线性调频连续波雷达逐渐应用于近距离高分辨率多目标探测与成像。本文通过对一种线性调频连续波雷达系统结构,设计了一套中频信号接收机,能够有效实现中频信号的接收和处理,能准确测量出目标信号的频率信息。

1 线性调频连续波雷达系统方案

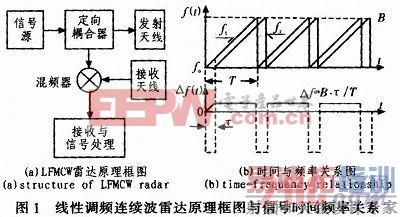

传统线性调频连续波雷达的原理结构和时间频率关系如图1所示,用发射信号与接收信号进行混频,得到零差拍信号,该信号的频率反映了目标的距离信息。对每一周期有效时间内的零差拍信号进行频谱分析,便可提取出目标的距离信息。

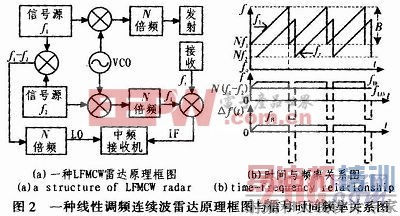

本文中中频信号接收机所针对的一种线性调频连续波雷达的结构与图1中结构有所不同,如图2所示。

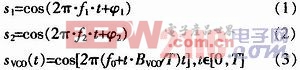

设信号源1,信号源2以及VCO的信号形式分别为:

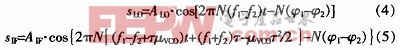

假设目标距离为R,回波延时为τ,压控振荡器VCO的调频斜率为μVCO,则易得到中频接收机的输入本振,中频信号以及混频得到基带信号的形式分别为:

![]()

显然NμVCOτ就是对应的基带信号频率fB,N和μVCO是定值,所以提取出基带信号频率就可求出回波延时τ,也就得到了目标的距离。设μ=NμVCO为雷达发射载波的调频斜率,则易得目标距离与基带信号频率之间的关系式:

![]()

在该线性调频连续波雷达系统中,中频接收机收到的本振信号是两个固定频率源的差频的N倍频,也是一个固定频率的信号,fLO=1.2 GHz,雷达发射载波的调频斜率是VCO调频斜率μVCO的N倍,μ=240GHz/s,线性调频周期T=10ms。由于该雷达用于近距离高分辨率成像及隐蔽物体的检查,作用距离较小,Rmax=100 m,将μ、Rmax以及光速c带入式(7)中可得fBmax=160kHz,所以基带信号的实际有用带宽为160kHz。

[p]

2 系统硬/软件设计

2.1 模拟中频信号到数字基带信号的处理方案

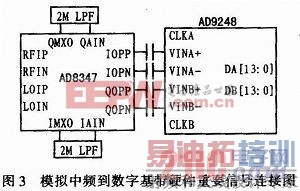

AD8347的射频信号输入范围800 MHz~2.7GHz,-3dB解调带宽为65MHz,由于输入的中频信号IF频率为1.2GHz,基带信号实际有用带宽160 kHz,输入输出信号的频带AD8347都完全适用。AD8347的正交误差1°,振幅平衡0.3 dB,具有较好的精度。内部集成69.5 dB自动增益放大器,能够适应-70~10 dBm输入功率变化。

AD9248-65是一款14位双通道,最高采样频率65 MSPS的模数转换器,具有高性能采样保持放大器、时钟占空比稳定器和内部参考电压。信噪比71.6dBc,无杂散动态范围80dBc,全功率输入带宽500 MHz,300 mW的低功率。在实际应用中,选择使用内部参考电压,输入电压范围选择2 V峰峰值。

实际有用基带信号带宽160kHz,在采样之前需做抗混叠滤波,LC滤波器不易做到1MHz以下的低通,故滤波器选择了通带截止频率2MHz,阻带起始频率5 MHz的LC低通滤波器,采样率50 MSPS,采样频率为带宽的10倍,过采样还能提高信噪比。模拟中频到数字基带硬件重要信号连接图所图3所示。

2.2 基于FPGA的数字信号处理方案

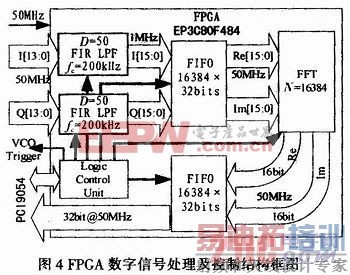

根据FPGA要实现的数字信号处理功能以及存储容量和时序控制逻辑的规模,评估了所需要FPGA的逻辑资源、管脚数量、片内存储资源等因素,最终选取了Ahera公司Cyclone III系列的EP3CSOF484C8。FPGA系统时钟50 MHz,采用主动串行(AS)配置方式,配置芯片选择EPCS16。

由于抗混叠滤波器的通带截止频率为2 MHz,相对于160 kHz的实际有用基带信号带宽,仍然存在很大的带外噪声,并且由于50 MSPS的采样率过高,导致数据率大大超过了实际需求,所以在FPGA内部首先要做1/O两路并行的抽取式FIR低通滤波。抽取系数50,系数精度16位,输入位宽14位,输出保留16位。通带截止频率160kHz,阶数为400阶,Blackman窗,在400kHz处衰减80dB。抽取之后得到的实际采样率为1MHz,是400 kHz带宽的2.5倍,满足奈奎斯特采样要求。既有效滤除了绝大部分带外噪声,又降低了数据率。

线性调频连续波雷达的发射与接收是需要同步进行的,系统采用由接收机发出Trigger信号触发发射机的VCO开始扫频的方式。上位机通过PCI9054把开始指令发给FPGA,FPGA各模块进入工作状态的同时发送Trigger信号触发VCO开始线性调频。

输入的采样数据经FIR低通抽取滤波以后,每50个时钟周期输出一次,所以整个VCO扫频周期内得到的数据仅10 000次。由于FFT变换采用的是Altera FFT IP核的Burst数据流模式,需要将一帧源数据连续输入,而抽取滤波器输出的数据流是非连续的,所以采用了16384x32bits的FIFO1进行缓存,VCO扫频结束后,再将FIFO1中的数据连续地传输给16384点的FFT运算模块,有效数据仅有10000点,需添6384点零补齐。

FFT变换输出的实部和虚部数据各16位,每帧16 384点,存入16 384x32 bits的异步FIFO2,FIFO2可以完整存放一帧数据。当FIFO2非空时,FPGA对PCI9054产生本地中断LINT#信号,PCI9054通过Local总线将FIFO2中的数据读出。FPGA数字信号处理及控制结构框图如图4所示。

2.3 PCI总线接口方案

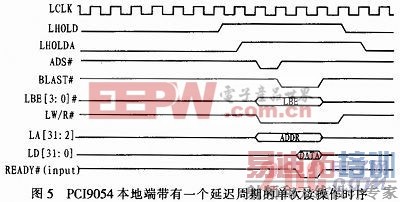

系统采用了PCI9054作为接口芯片,为PCI总线和局部总线建立起一条高速的数据通道,突发数据传输速度峰值可达132 MB/s。本系统中PCI9054采用本地数据和地址非多路复用的C模式,数据总线宽32位,本地时钟50 MHz。[p]

PCI9054负责将上位机的指令通过本地总线发送给FPGA,接收到FPGA发出的LINT#中断后对上位机产生INTA#中断,上位机收到中断后通过PCI9054读取FPGA中FFT变换得到的数据。读操作时序如图5所示。

2.4 系统软件设计

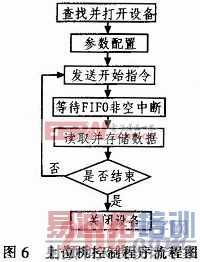

PLX公司为PCI9054提供了一套PLXSDK开发套件,其中包括驱动程序、PLXMon调试工具以及API函数,在VC++6.0中完成上位机控制台操作界面的设计并调用API函数完成对PCI9054的操作。上位机控制程序流程图如图6所示。

3 实验结果

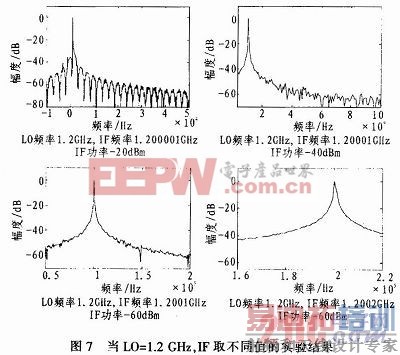

因为对于一个距离一定的目标,其理想回波的中频信号就是一个单频信号,所以在单独测试中频接收机时可以分别用两台信号源产生两个单频信号输入接收机的IF和LO接收端,LO输入信号频率1.2 GHz,功率-10 dBm。IF信号频率为1.2 GHz偏差在200 kHz范围内,功率-60~10dBm。

从图7中可以看出,当IF频率为1.200 001GHz,信号功率为-20dBm,得到基带信号频率为1kHz,信噪比约为60dB;当IF频率为1.200 01 GHz,信号功率为-40 dBm,得到基带信号频率为10 kHz,信噪比约为60dB;当IF频率为1.200 1 GHz,信号功率为-60 dBm,得到基带信号频率为100 kHz,信噪比约为50 dB,所以虽然中频输入信号IF的信号功率衰减到了-60 dBm,得到基带信号的信噪比仍能保持在一个较好的结果,这是由于前段混频器AD8347具有69.5 dB自动增益放大器。当IF频率为1.200 2 GHz,信号功率为-60 dBm,与IF频率为1.200 1 GHz时的功率相同,但得到2 kHz基带信号的信噪比约为40 dB,说明FIR低通滤波器起了作用,在200 kHz处已经衰减了10 dB以上。所以可以证明中频接收机对1.2 GHz偏差1~160 kHz范围都能良好地完成接收任务,可以准确地测量出IF信号与LO的差频。

4 结论

本文阐述了一种线性调频连续波雷达中频接收机的系统结构,针对系统参数完成了中频接收机的硬/软件设计,能够实现对中频信号的接收和处理,测量目标回波的差拍频率,可实现近距离高分辨率探测,采集处理后存储的数据可用于雷达成像。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...