- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速数字相关器设计

摘要:在数字通信的数据传输过程中,需要保持数据在传输过程中的同步,因此要在数据传输过程中插入帧同步字进行检测,从而有效避免发送数据和接收数据在传输过程中出现的异步问题。文中提出了一种采用流水线技术、基于 FPGA设计高速数字相关器的方法。仿真结果表明设计方案是可行的。

在数字通信系统中,常用一个特定的序列作为数据开始的标志,称为帧同步字。在数字传输的过程中,发送端要在发送数据之前插入帧同步字。接收机需要在已解调的数据流中搜寻帧同步字,以确定帧的位置和帧定时信息。帧同步字一般为一系列连续的码元,在接收端需要对这一系列连续的码元进行检测,如果与预先确定的帧同步字吻合,则说明接收端与发送端的数据是保持同步的,开始接收,否则不能进行接收。完成帧同步字检测工作的正是数字相关器。本文采用流水线技术,研究了基于 FPGA的高速数字相关器的设计方法,并给出了 MAX+PLUSII环境下的仿真结果。

1 数字相关器原理

数字相关器在通信信号处理中实质是起到数字匹配滤波器的作用,它可对特定码序列进行相关处理,从而完成信号的解码,恢复出传送的信息。其实现方法是进行两个数字信号之间的相关运算,即比较等长度的两个数字序列之间有多少位相同,多少位不同。昀基本的相关器是异或门,例如,y=ab,当 a=b时,y=0,表示两位数据相同;当 a≠b时,y=1,表示两位数据不同。多位数字相关器可以由一位相关器级连构成。 N位数字相关器的运算通常可以分解为以下两个步骤:对应位进行异或运算,得到 N个 1位相关运算结果;统计 N位相关运算结果中 0或 1的数目,得到 N位数字中相同位和不同位的数目。

当数字相关器接收到一组数据时,在时钟的上升沿对帧同步字进行检测。对于帧同步字是一个连续 16位的码元,数字相关器在进行检测的过程中,只有当连续检测到 16位的码元与预先设定的帧同步字完全相同时,才由输出端输出信号表示帧同步。否则,任何一位出现不相等,数字相关器又将重新开始进行检测,直到出现连续的 16位码元与预先设定的 16位码元完全相等时才进行输出。数字相关器的设计一般考虑采用串行输入或并行输入两种输入检测方式,由于串行输入是在 16个时钟周期内依次对两路串行输入信号 A、B进行异或运算,并统计数据位相同个数,检测速度较慢,要提高检测速度,就要考虑采用并行输入检测方式。

2 高速数字相关器的 FPGA实现

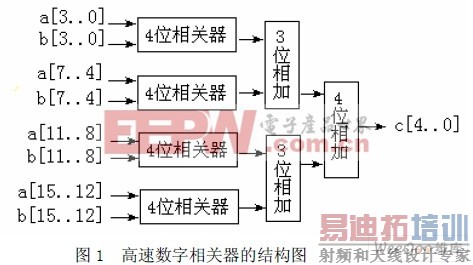

在 16位并行数字相关器中,由于实现 16位并行相关器需要的乘积项、或门过多,因此为降低耗用资源,可以分解为 4个 4位相关器,然后用两级加法器相加得到全部 16位的相关结果,其结构图如图 1所示,如果直接实现该电路,整个运算至少要经过三级门延时。随着相关数目的增加,速度还将进一步降低。为提高速度,采用“流水线技术”进行设计,模块中对每一步运算结果都进行锁存,按照时钟节拍逐级完成运算的全过程。虽然每组输入值需要经过三个节拍后才能得到运算结果,但是,每个节拍都有一组新值输入到第一级运算电路,每级运算电路上都有一组数据同时进行运算,所以总的来讲,每步运算花费的时间只有一个时钟周期,从而使系统工作速度基本等于时钟工作频率。

[p]

在使用 VHDL进行高速数字相关器设计时,主要实现 4位相关器和多位加法器模块的设计。其元件生成图分别是 4位相关器模块 XIANGGUAN4、3位加法器模块 ADD3和 4位加法器模块 ADD4,其电路原理图如图 2所示。其中 4位相关器模块 XIANGGUAN4的主要源代码为:

entity xiangguan4 is

port(a,b:in std_logic_vector(3 downto 0);

sum:out std_logic_vector(2 downto 0);

clk:in std_logic);

end ;

architecture one of xiangguan4 is

signal ab :std_logic_vector(3 downto 0);

begin

ab=a xor b; --判断 a,b是否相同

process(clk)

begin

if clk'event and clk='1' then

if ab=1111 then sum=000; --列出各种组合,输出相应相关值

elsif ab=0111 or ab=1011 or ab=1101 or ab=1110 then sum=001;

elsif ab=0001 or ab=0010 or ab=0100 or ab=1000 then sum=011;

elsif ab=0000 then sum=100;

else sum=010;

end if;

end if;

end process;

end one;

[p]

3 仿真实验及结论

在 MAX+PLUSII环境下,根据高速数字相关器的原理图进行设计,这里将时钟端 gck设计为周期 10ns的时钟。a[15..0]端为帧同步字设置端,将其设置为 1、0交替码; b[15..0]端为码元输入端,输入连续的信号,其输入码元的周期也为 10ns ;c[4..0]作为记录信号,记录连续的输入码元与帧同步字相同的个数。然后对原理图进行编译、仿真,得到仿真波形如图 3所示。可以看出,从连续的 16个码元输入到同步检测输出经过 3个时钟周期,输出端 c[4..0]表示了连续的输入码元 b与帧同步字 a相同的个数,当 c[4..0]为 16时,表示 a和 b实现了同步。在对高速数字相关器进行编译、仿真成功后,对引脚进行锁定并将编程文件下载到 ALTERA公司 ACE1K系列芯片 EP1K30QC208进行实验验证,实验结果正确,表明设计是可行的。

4 结束语

数字相关器实现了数字通信过程中帧同步字的检测,在数字通信系统中具有重要的作用,广泛应用于帧同步字检测、扩频接收机、误码校正以及模式匹配等领域。本文采用 FPGA对高速数字相关器进行设计,并进行了编译仿真和下载实现。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...