- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ASIC+FPGA的IPv6路由器PoS接口设计

IP over SDH(PoS)技术是通过SDH提供的高速传输通道直接传送IP分组,它位于数据传输骨干网,使用点到点协议PPP将IP数据包映射到SDH帧上,按各次群相应的线速率进行连续传输,其网络主要由大容量的高端路由器经由高速光纤传输通道连接而成。这种技术实际上是对传统IP网络概念的延续,完全兼容传统的IP协议体系,只是在物理通道上借助SDH提供的点到点物理连接,从而使速率提高到Gbit/s量级,因此PoS技术现在和今后都将是非常重要的IP网络传输手段。

155Mbit/s PoS接口是IPv6路由器所提供的一种重要的PoS接口,本文介绍基于PMC公司PM5380型8×155Mbit/s和Xilinx公司VIRTEX-II PRO型300万门的大规模可编程器件的网络接口硬件设计与实现方案,也给出其中关键的FPGA设计。该设计在国家数字交换系统工程技术研究中心研制的IPv6路由器(国家863重大项目)中已经获得实现,性能良好。

1 155Mbit/s PoS接口工作原理

1.1 IPv6路由器体系结构

IPv6路由器主要包含如下子系统:线路接口子系统、多功能转发子系统(“多功能”主要是指该转发系统支持多种协议类型:IPv4、IPv6、MPLS)、高速交换子系统和主控(完成各个子系统的管理,集中处理本路由器收到的路由信息,计算并更新路由表)以及OAM(操作维护台)。图1是IPv6路由器的体系结构。

不同类型的网络分别通过相应类型的线路接口接入路由器,数据从线路接口进入路由器后再进行转发和交换,在此过程获取指明下一路网络的路的信息,最终从相应的接口以输出网络要求的格式输出。PoS线路接口就是是线路接口子系统的一种。

1.2 155Mbit/s PoS接口的工作原理

155Mbit/s PoS线路接口板的设计目标是为IPv6路由器提供8个155Mbit/s PoS接口,并支持IPv4、IPv6和MPLS包。在接收方向上将封装在SDH帧中的IP包提取出来送到协议处理单元或转发模块处理;在发送方向上将IP包封装在SDH帧中,然后送到SDH传送网上。

155Mbit/s PoS线路接口板的主要功能就是实现IP数据包和SDH帧的映射和去映射,具体功能可从接收和发送二个方向详细描述。

在接收方向(到达路由器)的主要功能有:

接收外部线路光信号,进行光/电转换,以串行数据输出;

对串行数据进行串并转换,得到SDH帧;

对SDH帧进行去开销和拆帧处理,输出SDH网管信息并提取出HDLC帧;

从HDLC帧中提取出PPP分组;

检测PPP分组类型,区分PPP协议分组和PPP数据分组;

对于PPP协议分组,送到线路接口处理机去处理;

对于PPP数据分组,提取出其中的IP包或MPLS包,按照要求格式转换后送到缓存(FIFO)中。 发送方向(离开路由器)的主要功能有:

接收输出处理模块的IP分组,去除内部IP包头,形成PPP分组,并将它输出到相应的线路接口上;

接收本地生成的PPP协议分组;

将PPP协议分组与该线路接口上的PPP数据分组进行合路;对每一路PPP分组进行HDLC成帧和SDH成帧处理;

对SDH帧数据进行并串行转换;

将串行数据进行电光转换后发送出去。

2 系统设计

根据155Mbit/s PoS线路接口板要实现的主要功能和PoS的工作原理,可以将155M PoS线路接口分为8个模块:光电转换模块、定时处理模块、串并转换模块、SDH和HDLC处理模块、PPP处理模块、处理机模块、输入缓存模块和输出缓存模块,其逻辑结构框图如图2所示。

其中,光电转换模块主要实现光信号和电信号之间的转换。定时处理模块负责从接收的串行数据中提取时钟信号。串并转换模块实现串行数据和并行数据之间的转换。在接收方向上,在对信号进行串并转换之前,对于串行的输入数据需要进行帧和字节边界的检测。SDH和HDLC处理模块是155M PoS线路接口的关键模块,完成STM-1的映身教 处理及HDLC帧格式的封装和拆装。PPP处理模块主要完成对PPP分组的硬件处理。处理机模块负责单板的初始化、状态监测和控制、处理PPP协议分组以及与主控通信等任务。输入缓存用来存放线路接口发送转发处理的数据包,输出缓存用来存放调度输出后送给线路接口的数据包。 [p]

根据目前的技术水平,可选择如下方案:光电转换模块由专用的光电器件完成,串并转换、定时处理、HDLC/SDH等物理层处理功能由专用电路完成,而PPP处理由FPGA完成。

3 关键电路的选型及说明

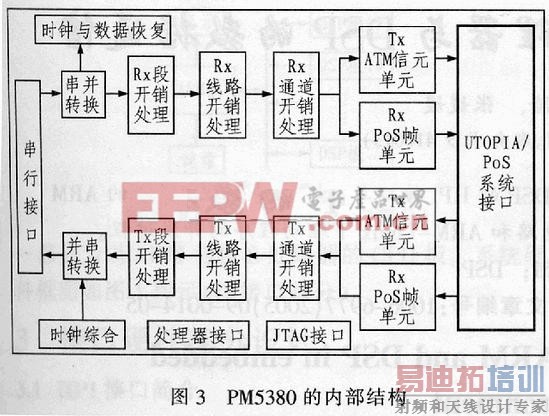

物理层处理电路采用PMC公司的PM5380,它是一款新型的PoS/ATM专用处理电路,支持8路独立的ATM/PoS接口。该电路具有极高的集成度,将定时提取模块、串行转换模块、段开销处理模块、通道开销处理模块、路开销处理模块和HDLC处理模块等集成到一起,功能非常强大。其内部结构见图3。

PM5380的设计符合IETF PPP工作组提出的PPP over SDH/SONET规范;支持8路全双工155Mbit/s的STM-1接口,并带有数据和时钟恢复(CDR)电路;完全符合Utopia-2接口规范,支持多地址和奇偶校验;对PoS应用提供相当于Utopia-2的系统接口,16位总线宽度,支持包传送和字节传送,内置8个FIFO缓存对应接口的数据;提供串行的155Mbit/s的接口与光器件对接,并且都是差分线路;提供一个通用的八位微处理器接口来完成PM5380的初始化配置、工作控制以及状态监测;支持线路环回、串行环回和并行环回;单电源3.3VCMOS制作工艺,输入兼容PECL和TTL电平,输出为TTL电平。在本设计中,需要通过处理机配置相应的寄存器,使PM5380工作于PoS模式。

FPGA选用Xilinx公司VIRTEX-II PRO,该电路是300万门级的FPGA,其高速I/O模块可提供多达16路Rocket I/O,内置Power PC核提供高性能的数字时钟管理,并且具有强大的开发软件支持。

4 实现方案

图4为155Mbit/s PoS接口的实现方案图。在输入方向上,从光纤传入的信号经光电转换后送入PM5380,完成定时处理、帧同步,从输入比特流中提取出SDH帧并进而恢复出PPP帧,并按接口缓存于内部8个FIFO中。输入链路处理模块轮询读取PM5380的FIFO,获得PPP帧并完成PPP相关处理,恢复出IP报文并且完成查IP地址表的工作,将协议报文交处理机,而普通的数据报文合路输入FIFO,进而通过FPGA的Rocket I/O(高速I/O)送转发处理。

在输出方向上,从转发过来的数据报文 经Rocket I/O送FPGA内部,在输出链路处理模块中完成与协议报文的合路并且封装成PPP帧,然后根据内部报文格式中的出接口号来判断送往ASIC的哪个接口;ASIC完成SDH帧的映射,最后经电光转换通过光纤送到外部SDH网络。

5 FPGA设计

图5中的虚线框内为输入FPGA设计原理。输入FPGA的轮询接收模块从PM5380的FIFO中轮询读取8个外部接口的数据,并将完整的PPP包缓存;分拣模块查本地IP表,将协议报文缓存于协议FIFO并经处理机送交主控处理,需转发的数据报文送转发FIFO。图中的MPM5380管理模块负责产生处理机管理PM5380时所需要的时序,CPU模块负责和860的交互,时钟模块产生系统时钟,它们是公共模块。

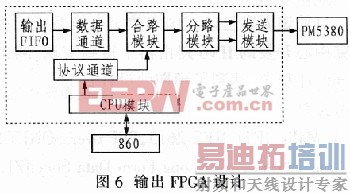

图6示出输出FPGA设计原理。从转发过来的数据经Rocket I/O后缓存于输出FIFO,合路模块将数据报文和从处理机下发的协议报文合路送发送模块按照PM5380要求的时序写到相应接口的FIFO中发送,但这里必须严格满足PM5380的写时序要求。

6 结束语

本文根据IPv6路由器155Mbit/s PoS接口的需求,提出并实现了一种基于ASIC+FPGA的设计方案。目前该方案已经在国家数字交换系统工程技术研究中心开发的IPv6路由器中得到实现,测试后的系统性能稳定,达到了预期的设计目标。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于FPGA的防盗定位追踪系统

下一篇:电压空间矢量研究及Matlab仿真