- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于PC104总线和CPLD的测频模件设计

摘要:根据某测试系统的需要,设计基于PCl04总线和CPLD的高精度测频模件,采用多周期同步测频法实现对所测频段的等精度测量。设计了该测频模件的硬件电路,并给出用CPLD实现数字频率计的详细VHDL源代码。采用原理图的方式编写PC104总线的接口逻辑,并利用Max+P-lusⅡ软件进行仿真。结果显示频率计及接口逻辑均可正确工作。实际应用表明,该测频模件具有精度高,可靠、稳定等优点。

关键词:PCl04;CPLD;多周期同步测频;VHDL

随着科学技术的发展,嵌入式产品在军事领域的应用日益广泛,特别是在各种系统的自动化测试领域。频率测试是测试系统中的重要测试项目,在此设计一种基于PC104嵌入式计算机和CPLD的高精度测频模件,以满足对频率量的测试。

1 测频原理

传统的频率测量方法有两种:直接测频法和测周期法。直接测频法就是在给定的闸门信号中填入被测脉冲,通过必要的计数线路,得到填充脉冲的个数,从而算出待测信号的周期。它的主要缺点是存在被测脉冲的±1个误差,难以兼顾低频和高频实现等精度测量,所以测量准确度较低。测周期法是在一个信号周期内记录下基准定时脉冲的个数,然后换算成频率f。主要缺点是存在基准脉冲的±1个误差,适用于较低频率的测量。

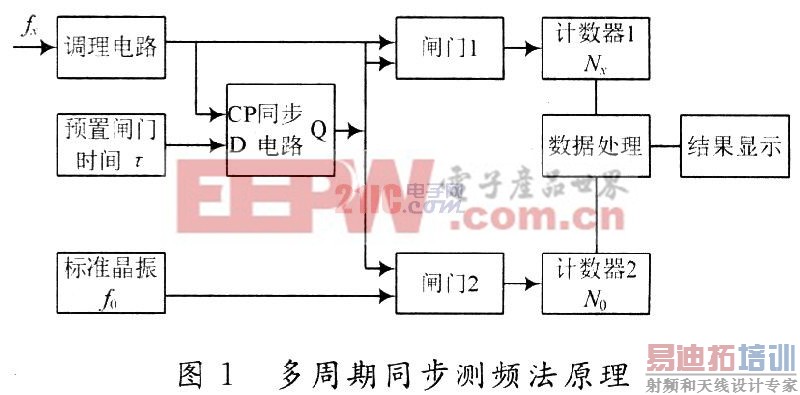

多周期同步测频方法是在直接测频的基础上发展而来的,其特点在于测量过程中实际闸门时间不是固定值,而是被测信号周期的整数倍,即与被测信号是同步的,因此消除了对被测信号计数产生的±1个误差,测量精度大大提高,而且达到了在整个测量频段的等精度测量。多周期同步测频法的原理,如图1所示。

如图1所示,首先,由控制线路给出闸门开启信号,计数器等到被测信号的上升沿到来时,真正开始计数;然后,两组计数器分别对被测信号和标准频率信号计数。当控制线路给出闸门关闭信号后,计数器等到被测信号下降沿到来时结束计数,完成一次测量过程。可以看出,实际闸门与设定闸门并不严格相等,但最大差值不超过被测信号的一个周期。被测频率的计算方法为:

式中:Nx为被测信号的计数值;N0为标准频率信号的计数值;f0为标准频率信号的频率;τ为闸门时间,计数器的开闭与被测信号完全同步,即在实际闸门中包含整数个被测信号的周期,因而不存在对被测信号计数的±1个误差。

2 硬件电路设计

如图2所示,该模件硬件主要包括PC104控制处理模块、CPLD测试模块、信号调理模块、继电器驱动模块和高精度20 MHz晶振。在该系统中为了实现对多路频率信号的测量,采用了通过继电器控制来选择信号的方案。通过CPLD控制继电器的动作,接通不同的继电器开关,被测信号通过继电器之后,由6N137高速光电隔离器隔离、电平转换之后送入CPLD进行测频。由于CPLD的I/O口驱动电流较小,所以加了一级ULN2803驱动器来驱动继电器的线包。CPLD主要完成的功能是实现数字频率计,采用多周期同步测频法完成对输入信号频率的测量,并通过与PC104的接口逻辑,将测量结果送给PC104主机,由主机进行频率值的计算及显示,从而完成整个测频模件的功能,CPLD选用Altera公司的EPM7128SQCl00芯片。

3 软件设计

3.1测频电路程序设计

对于CPLD的编程,一般有通过电路原理图的方式和通过硬件描述语言即VHDL语言两种方式。第一种方式直观性强,较好理解,适用于小规模数字电路的设计;第二种方式具有多层次描述系统硬件功能的能力,可读性强,适用于时序电路及大规模电路的设计。本文采用两者相结合的方式,用VHDL语言实现数字频率计的设计,用原理图的方式实现了PC104主机的接口逻辑,并进行仿真。结果表明完全可以满足功能需求,编译环境为Max+PlusⅡ。

以下为数字频率计的VHDL语言源代码。设计了两个32位计数器,一个8位数据选择器及一个触发器控制闸门信号。

以上程序通过软件编译后生成数字频率计的逻辑功能模块图如图3所示。以下是程序的仿真波形(见图4),标准频率为20 MHz,被测信号频率为O.1 MHz,仿真时间设为120μs。

从仿真的结果可以看出,在定时脉冲CL到来时,计数器并没有开始计数,而是等到被测信号的上升沿到来时,START信号才开启,计数器开始计数,定时脉冲结束时,计数器也是等到被测信号的上升沿到来时才结束计数,实现了多周期同步测频。图4中被测信号频率的计算方法如式(1)所示。与系统预设值相同,可以实现所需的功能。

3.2 PC104接口电路实现

该设计中PC104接口电路部分在Max+PlusⅡ中用原理图的方式实现。使用的PC104总线信号有地址线A0~A9、数据线D0~D7、读写信号线IOR/IOW、复位信号RESET、中断信号IRQ3、地址允许线AEN。在PC104总线的接口电路部分遵循一个原则:就是输出加锁存,输入加缓冲驱动。该接口电路示意如图5所示,首先地址线的A3~A9位与外部波段开关设置地址及AEN信号通过译码电路中的比较器进行比较,若相同,则说明该模块被选中,然后根据A0~A2的译码结果,结合读写信号线产生输出锁存器74HC273及输入缓冲器74HC244的脉冲信号或使能信号,完成对数字频率计及外部电路的读写及控制。在总线工作方式上采用中断方式。设计中,将计数器的实际计数结束信号EEND作为总线的中断触发信号IRQ3,以此来提高PC104总线的工作效率。该接口逻辑的仿真结果如图6所示。

从仿真结果可以看出,接口逻辑可以很好地控制外部继电器的接通,产生清零及定时脉冲,并能正确地读取数字频率计的计数结果,实现模块预定的功能。该接口逻辑已在实验中得到了验证。

3.3 PC104应用程序设计

在调试该模件时系统采用Windows。Me操作系统,编译环境采用TC 3.0。主程序包括系统初始化、中断初始化、接通继电器及产生清零和定时脉冲模块。在中断服务程序中主要完成了读取计数值、计算频率值及显示打印功能。它的程序流程图如图7所示,在此不再列出具体代码列。

4 实验结果

实验采用的方法是将板载的20 MHz的晶振在CPLD内部分别进行2分频和20分频,得到10 MHz和1 MHz的信号,然后再将这两个频率信号分别进行2.4,6,8分频,得到共9个被测信号,闸门时间为1 s,测试结果如表1所示。

由测试结果可以看出,模件的测频精度较高,完全能够满足一般性测试系统的需要。

5 结语

采用多周期同步测频技术设计并实现了基于PC104总线和CPLD的测频模件。给出硬件设计原理图和数字频率计的VHDL程序源代码,PC104总线的接口逻辑电路,最后得出仿真结果,编制了PCl04总线应用程序。实际应用表明,该模件精度高,稳定性好,能够很好地完成对频率量测试的任务。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...