- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的DDS设计

摘要:利用现场可编程门阵列(FPGA)设计并实现直接数字频率合成器(DDS)。结合DDS的结构和原理,给出系统设计方法,并推导得到参考频率与输出频率间的关系。DDS具有高稳定度,高分辨率和高转换速度,同时利用Ahera公司FPGA内的Nios软核设置和显示输出频率,方便且集成度高。

关键词:现场可编程门阵列;直接数字频率合成器;Nios;VHDL

直接数字频率合成DDS(Direct Digital Synthesis)是一种把一系列数字信号通过D/A转换器转换为模拟信号的合成技术。该技术的主要特点:具有超高的捷变速度(0.1μs)、超细的分辨率(可达1μHz)和相位的连续性;输出频率的稳定度及相位噪声等指标与系统时钟相当;全数字化便于单片集成等。基于以上优点,DDS得到广泛应用,但由于其输出带宽小和杂散指标不高,限制了其应用范围。

现有的DDS产品应用于接收机本振、信号发生器、通信系统、雷达系统等,特别是跳频通信系统。这里介绍基于FP-GA的DDS信号源,可在1片FPGA器件上实现信号源的信号产生和控制。将DDS信号源设计嵌入到FPGA器件所构成的系统中,其系统成本不高,但可实现更加复杂的功能。

1 DDS原理

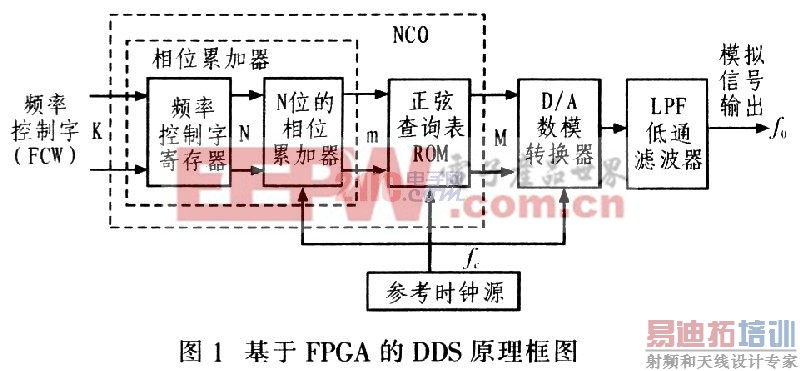

DDS基本结构原理如图1所示,其中数控振荡器(NCO)为FPGA实现部分。其工作原理是:在参考时钟的作用下,相位累加器按照预先设置好的频率控制字进行线性累加,其输出作为波形查找表的地址,通过寻址输出相应的波形幅度码,再由数模转换器将这些数字码变换为模拟电压/电流输出,最后经低通滤波器平滑输出波形。假设要输出的频率是同定的,那么相位增量就是一个常数,在每个时钟周期,相位累加器的数值就按照这个相位增量累加一次,相位增量的大小由频率控制字决定。如果相位增量增大,则相位累加器的增加就比较快,输出的频率就比较高。

假定一个频率为fc的载波,其时域表达式为:

则由式(1)、式(2)看出:C(t)是关于相位的一个周期函数,如果记下一个周期内每个相位对应的幅度值,那么对于任意频率的载波,在任意时刻,只要已知载波的相位φ(t),就可通过查表得到C(t)。[p]

2 DDS结构

2.1 相位累加器

相位累加器是DDS系统的核心,可完成DDS实现原理中的相位累加功能。为充分发挥DDS的优越性,一般累加器的位数都比较大,频率字可控制DDS的输出频率,可根据需要设定。

2.2 波形查询表

该电路的核心是一个查找表,查找表主要完成相位序列(相位码)向幅度序列(幅度码)的转换。这里,用ROM构造一个查找表。如果把相位码作为ROM的地址,只要在该地址中存储相应的正弦幅度码作为数据,就可通过相位码寻址ROM,输出信号函数。

2.3 D/A转换器与低通滤波器

D/A转换器和低通滤波器的作用是将幅度码转变成模拟信号。由于D/A转换器输出为阶梯波,需通过低通滤波器取出其低频成分(即DDS输出)。

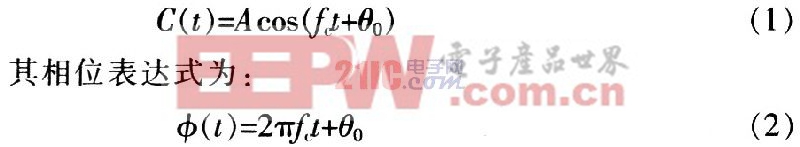

3 DDS频率分析

相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器加满时就会产生一次溢出,从而完成一个周期,这个周期也就是DDS信号的一个频率周期。

可见,通过设定相位累加器位数、频率控制字K和基准时钟的值,可以产生任意频率的输出。DDS的频率分辨率定义为:△fmin=fc/2N。

由于基准时钟一般固定,因此相位累加器的位数即决定频率分辨率。如果相位累加器为32位,那么频率分辨率就可以认为是32位。位数越多,分频率越高。只要N足够大,即累加器有足够的长度,总能得到所需的频率分辨率。输出频率f0由频率控制字K决定,即f0=K(fc/2N)。根据奈奎斯特采样定理,DDS的最大输出频率f0Max应小于fc/2,在实际中,f0Max一般只能等于fc的40%。

4 DDS的杂散分析

DDS输出频率中的杂散信号是一个最重要的问题,而且是由于多种原因引起的。这里主要介绍以下3种原因:

1)电压幅度截断 幅度量化误差,就是ROM存储能力有限引起的舍位误差,也可以认为是由D/A转换器分辨率有限引起的误差。参照相关数据资料,波形ROM的位数为D,由幅度量化误差造成的输出背景噪声的单边带功率谱密度为:![]()

量化误差引起的量化失真,可以用输出信号与量化噪声功率之比SQR来衡量。当D/A转换器满幅度输出时,有![]()

式中,D是幅度量化的位数,D一定时,则噪声的功率就一定。

2)相位截断 由于ROM无法实现2N个地址单元的容量,因此截断相位码的高B位。主谱与最大的杂散幅度之比满足如下关系:

式中,N为相位累加器的位数,B为相位截断位数。

由上式可看出,由相位截断引入的最强杂散相对主谱的电平由相位累加器输出的有效位数决定:有效寻址位数每增加1位,杂散性能约提高6 dB。

3)D/A转换器本身的问题 由于实际中D/A转换器的非线性、瞬间毛刺等非理想转换特性在输出频谱中会产生杂散。[p]

5 DDS的FPGA实现

FPGA即现场可编程门阵列,它是作为专用集成电路领域中的一种半定制电路而出现的,既解决定制电路的不足,又克服原有可编程器件门电路有限的缺点。本设计采用Altera公司的Cvclone:II型器件。在实现DDS功能的同时,还能利用其中集成的Nios软核进行控制模块设计,加强集成度,减少器件使用和简化电路设计。

本设计的软件开发环境为Altera公司的Quartus II和Nios II IDE。

5.1 QuartusⅡ下的DDS设计仿真

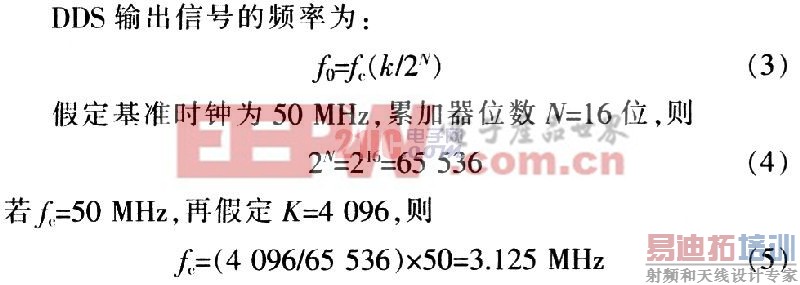

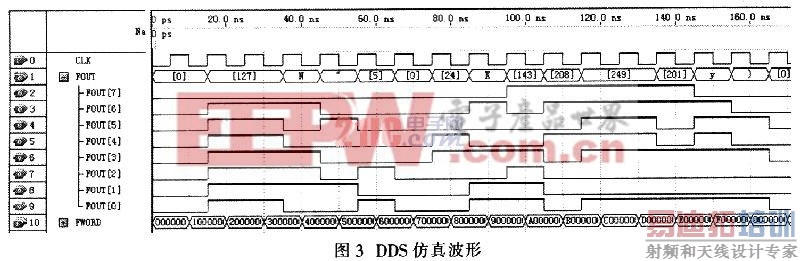

在Quartus II环境下利用VHDL语言对DDS内的寄存器、累加器及波形存储器进行设计及仿真,最后链接生成DDS模块,如图2所示。

在检查编译文件后对DDS模块进行仿真,仿真图如图3所示。至此在FPGA内已成功建立DDS模块。根据所选用的具体器件内部存储量的不同,可以根据自身需要更改ROM有效地址位数和ROM存储波形的有效位数以提高系统的杂散抑制能力。

5.2软核的硬件定制和软件设计

利用Quartus II内的SOPC Builder工具完成Nios软核内的CPU、Memory、I/O口等所需硬件定制。同时在NiosⅡIDE环境下运用C语言完成软核内控制系统功能设计。

6 结束语

本文对直接数字频率合成器结构、工作原理及DDS杂散分析进行了较深入研究,并在理论研究的基础上结合Ahera公司的CycloneII器件完成了DDS的设计和实现。同时利用CyclonelI器件内的Nios软核将DDS与控制系统模块集成到一块FPGA器件内,简化设计难度,减小电路复杂程度。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:怎样理解EMC电路

下一篇:基于FPGA快速A

律压缩编码的设计与实现