- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

ISPl362在基于FPGA的红外成像系统中的应用

摘要:ISPl362是飞利浦推出的一款USB可编程控制芯片,其内部集成了一个高级主控制器,一个外设控制器,主机和设备控制器兼容USB 2.O协议,支持12 Mb/s的全速传输和1.5 Mb/s的低速传输;芯片有三种工作模式,即主机控制器模式、设备控制器模式和OTG模式。主要针对USB控制芯片ISPl362在基于FPGA的红外成像系统的数据采集中的应用,利用Verilog HDL语言完成其在设备控制器模式下的功能,具有很好的可移植性。

关键词:FPGA;ISP1362;USB接口;固件;Verilog HDL

O 引言

近年来,红外热成像系统已越来越多地应用于军事和工业上,因此对红外图像的研究也成为热点话题。为适应很多实时图像处理方法的需求,图像处理系统对图像数据采集的速度及准确性的要求也越来越高。而传统的接口,如ISA接口、PCI接口、PS/2接口等都是非共享式接口,不但体积庞大,而且规格不一。USB接口克服了传统接口的上述缺陷,具有高速、双向、低成本以及兼容性好、通用性强等优点,已经在IT各个领域得到了广泛的应用。与此同时,各种型号的USB接口控制芯片也应运而生。ISPl362芯片以其成本低、可靠性高、功耗低以及易于扩展等优点,也受到了用户的广泛关注。ISPl362由主机控制器、设备控制器、OTG控制器、USB收发器、OTG收发器和寄存器等组成。其中,OTG控制器主要提供包括监控和转换功能在内的所有OTG控制,在OTG模式下,既可用作主机,又可用作外设,并支持主机通信协议(Host Neg-otiayion Protocol,HNP)和对话请求协议(Ses-sion Request Protocol,SRP)。考虑到以后进一步完善系统的需要,设计中选用此款芯片来完成USB接口的设计。该芯片内部没有集成MCU,设计中采用Altera的现场可编程门阵(Field-Programmabte Gate Arrav,FPGA)中的EP2C70-F672C6来控制芯片的正常运行,操作简单可靠。EP2C70F672C6具有低功耗、高密度以及低成本等优点,可提供4 608~68 416个逻辑单元,包括了多达150个嵌入式18×18位乘法器、专用外部存储器接口电路,最高操作频率可达到260 MHz。基于以上原因的考虑,选用此款FPGA芯片来实现红外成像系统中的各项功能。

l 红外成像系统

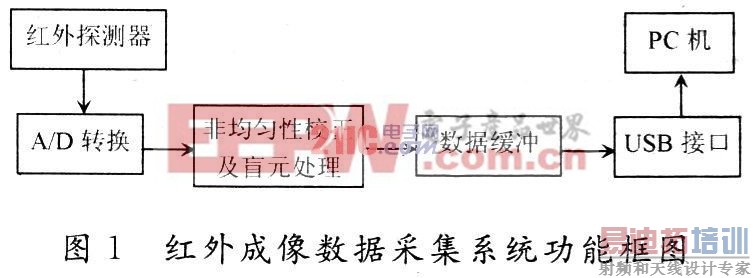

红外成像系统的功能框图如图1所示。整个系统功能在FPGA上实现。系统上电后,FPGA进行配置,红外焦平面探测器在驱动信号的作用下响应红外目标辐射,将辐射信号转变为模拟电压信号输出;A/D转换模块将模拟电压信号转变为数字信号,经非均匀性校正、盲元处理等过程,将数据存入FPGA外部存储器中。本工作的主要任务就是把存储器中的数据通过USB接口传输到PC机,以便于根据需要对数据做进一步的处理工作。

[p]

2 USB固件结构设计

USB固件结构设计包括枚举过程和数据传输过程。数据传输过程与枚举过程中的in中断的处理方法类似。因此这里主要介绍枚举过程的固件编写。

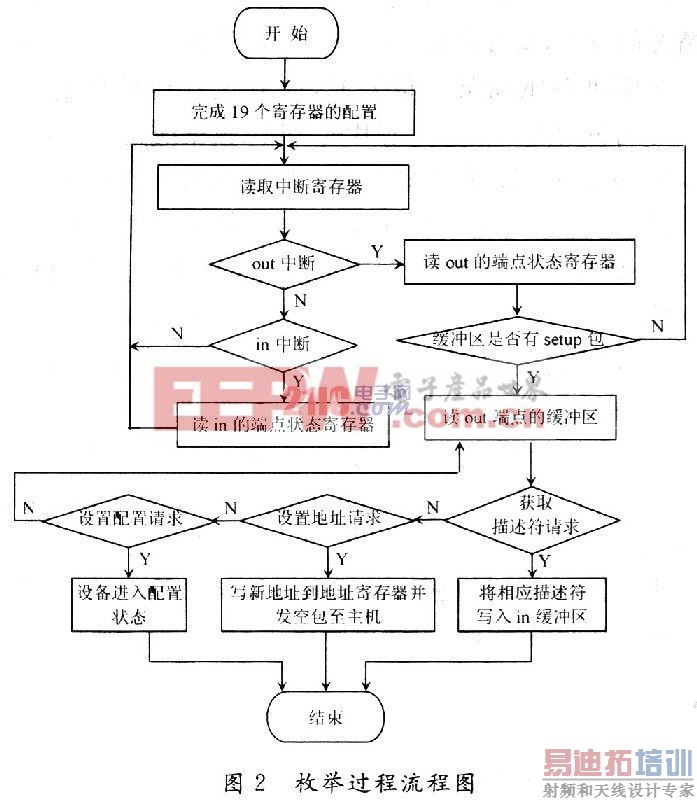

枚举过程的流程图如图2所示。

枚举过程就是主机通过向设备发送一系列请求来识别设备的过程。USB一共定义了11种标准USB请求,其中有些请求是必须的。例如,主机必须通过Get Descriptor请求来获取设备的设备描述符、接口描述符和端点描述符等信息,才能识别设备;必须通过Set Address请求为设备分配惟一的非零地址,以便于主机识别设备并与设备进行数据传输;必须通过SetConfiguration请求为设备分配非零的配置值等。USB请求只能使用控制管道来进行传输。主机在没有识别连上的是何种设备之前,会为未知设备分配一个默认地址O,主机通过0地址与设备通信,直到主机确定真正有设备连接了之后,就会为该设备分配一个惟一的非零地址。在此之后,主机可通过这个非零地址跟设备通信,包括获取该设备的所有配置信息、接口信息以及完成最后的数据传输等。

2.1 芯片初始化

芯片的初始化主要包括工作模式、速度的选择以及寄存器的配置等操作。工作模式的选择可通过设置ISPl362的第62引脚A1为高电平来实现。这里实现的是全速的数据传输。下面主要介绍寄存器的配置。[p]

ISPl362设备控制器内部40多个寄存器。编写代码时的重点工作就是根据寄存器每一位代表的意义确定配置值,特别是有些关键位,只有正确配置方能保证芯片的正常工作。在使用ISPl362之前,要先配置的寄存器有模式寄存器、硬件配置寄存器、中断使能寄存器等,端点配置寄存器可以在任何时刻完成,但仅在枚举后的初始化后才有效。为了便于程序设计,在一开始对模式寄存器、硬件配置寄存器、中断使能寄存器等配置的同时,也对16个端点配置寄存器进行配置。端点0为控制端点,包括in和out端点,这两个端点大小固定,均为64 B。枚举过程就是通过这个端点进行的。其余14个为可编程端点,也可以被配置成双缓冲端点进一步提高吞吐量。设计中端点1配置为64 B双缓冲批量in端点;端点2配置为16 B中断out端点;端点3配置为16 B中断in端点等;可以禁能不用的端点。配置模式寄存器时,尤其要注意可以通过第三位来使能所有中断。对于硬件配置寄存器,要注意中断输出管脚INT2的设置,这里选择低电平有效的中断信号模式。对这些寄存器正确配置之后,ISP1362就会进入预期工作模式。

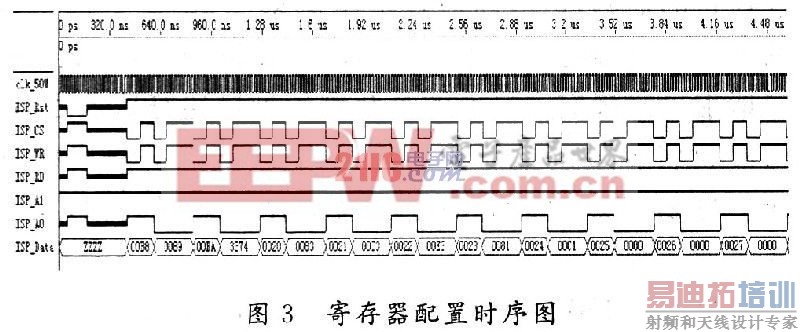

由于ISP1362中需要配置的寄存器很多,因此本设计中先在FPGA生成一片16位,大小为128 B的ROM,再将需要配置的寄存器的写命令和配置值按照顺序写入ROM中,配置时,只需将ROM中的数据依次写入芯片中即可。寄存器的配置时序如图3所示(为便于观察,图3中只截取了部分寄存器的配置情况)。

图3中信号clk_50M为全局时钟;ISP_Rst为芯片的复位信号;ISP_CS,ISP_WR,ISP_RD分别为ISPl362的片选信号、读信号、写信号,均为低电平有效;ISP_Al为模式选择信号,当其值为1时,芯片工作于设备控制器模式,为O时芯片工作于主机控制器模式;ISP_A0为高时对应的ISP_Data为DC的初始化命令,当ISP_AO为低时对应的ISP_Data为写入相应寄存器的配置值。

2.2设备接收请求

主机的每次请求,都是将请求以setup包的形式发送到out端点的out缓冲区。当out缓冲区接收到数据时,芯片的INT2管脚将会有中断产生。在模式寄存器、硬件配置寄存器、中断使能寄存器正确配置之后,当有中断事件产生时,ISP1362内部的SIE就能够检测到中断,并置中断寄存器的相应位为高电平。固件通过读取并分析中断寄存器的值来判断中断类型,再进行中断事件的处理。

固件首先检测到的是out中断。这是因为在上电复位以后,主机就向out缓冲区发第一个setup请求包。当接收到out中断时,固件首先读取out端点的端点状态寄存器将中断清除,以便于芯片接收其他的中断。接着固件再根据端点状态寄存器的值判断out缓冲区内是否含有setup包,然后固件读取out缓冲区。

根据out缓冲区的内容判断是何种请求,再决定做何响应。in中断的产生不同于out中断。in中断是在in缓冲区由空变满之后才产生的,in中断的产生需要固件进行写in缓冲区的操作。换而言之,是写in缓冲区的操作引发了in中断的产生,而不是in中断的产生引发了写缓冲区的操作。当固件检测到in中断时,同样要通过读in端点的端点状态寄存器将中断清除。[p]

2.3设备响应请求

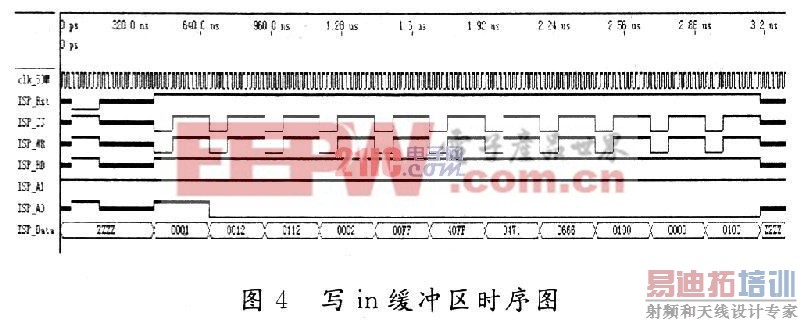

当芯片工作于设备控制器模式下时,设备端的工作就是被动的执行主机发来的请求。请求类型的确定是通过读取out缓冲区里的setup包来完成的。一个setup包(即请求包)有8个字节,根据其中第二个字节能够判断出请求类型。由流程图可以看出,枚举过程中主机要发出获取描述符、设置地址、设置配置等请求,对于获取描述符的请求,还需要进一步判断是获取何种描述符的请求,这可以通过请求的第三,四字节的值来确定。一旦确定了请求类型,设备就可以确定该如何响应请求。当确定主机发的是获取何种描述符请求之后,固件就将相应的描述符的值写入in端点的端点缓冲区。写in端点缓冲区的方法与寄存器配置类似,其时序如图4所示。

图4中ISP_A0为高时对应的ISP_Data(即0001)是写in缓冲区的命令,ISP_A0为低时对应的ISP_Data为写入的数据,其中第一个数据即(0012)为要写入的数据的长度,其余为设备描述符。当需要发送数据时,只需使能in缓冲区即可。若是设置地址请求,固件的工作就是将地址值取出来写入设备地址寄存器,然后再向主机发送一个空包。

3 LISB固件代码实现

在FPGA上用Verilog HDL实现上述功能时,难点有:一是多驱动问题;二是输入/输出端口的使用问题。由于程序中有多个模块同时作用于ISP1362的控制信号线以及数据线,如果处理不当,可能会产生同一时刻对同一信号有两次或两次以上的赋值的现象。为了避免这种情况的发生,就要在适当的时刻给信号线附上高阻,即当一个模块在驱动某一信号时,应避免其他模块也在这一时刻驱动这一信号。芯片的16位数据线为双向,这可以减少管脚的数量,节省资源。但在使用时若不注意,同样容易出错。inout管脚在使用时一般用三态门来实现,当inout端口不输出时,要将三态门置高阻。这在具体的软件实现中可以使用一个连续赋值(Assign)语句来实现,通过连续赋值语句将一个条件操作符赋值给这个输入/输出变量。该设计的代码中,双端口用语句ISP_Data=en

data:16’hzzzz实现其输入/输出功能。当en信号为高时,ISP_Data作为输出信号使用,其值即为data的值;当en信号为低时,ISP_Data作为输入信号使用。因此,程序中就可以根据需要通过控制en信号的高低来实现ISP_Data的输入/输出使用。

4 结语

采用高性能的Altera的FPGA中的EP2C70F672C6作为主控器件,实现了ISP1362在设备控制器工作模式下的功能,为解决红外图像处理系统中的数据传输问题提供了新的途径。在具体的软件实现中,成功地解决了多驱动问题和双向端口的使用问题。验证结果表明,程序的稳定性好、可移植性高,并且容易实现、易于维护。在成功地进行了枚举的过程之后,加载上设备驱动程序即可实现数据向主机以12 Mb/s的传输。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...