- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用VHDL设计的全数字锁相环电路设计

0 引言

全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。从而具备可靠性高、工作稳定、调节方便等优点。在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。随着电子设计自动化(EDA) 技术的发展,采用大规模可编程逻辑器件(如CPLD 或FPGA) 和VHDL 语言来设计专用芯片ASIC 和数字系统,而且可以把整个系统集成到一个芯片中,实现系统SOC ,构成片内锁相环。下面介绍采用VHDL技术设计DPLL 的一种方案。

1 DPLL 的基本结构

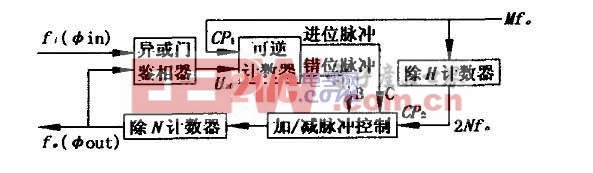

全数字锁相环结构框图如图1 所示, 由数字鉴相器、数字环路滤波器和数控振荡器3 部分组成。

设计中数字鉴相器采用了异或门鉴相器;数字环路滤波器由变模可逆计数器构成(模数K 可预置) ;数控振荡器由加/ 减脉冲控制器和除N 计数器构成。

可逆计数器和加/ 减脉冲控制器的时钟频率分别为Mf0和2Nf0 。这里f0 是环路的中心频率,一般情况下M 和N 为2 的整数幂。时钟2Nf0 经除H( = M/2N) 计数器得到。

2 数字锁相环的原理与实现

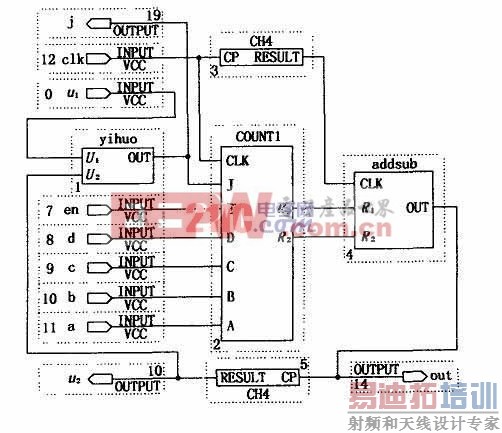

全数字锁相环原理如图2 所示, 其中: clk 为时钟频率,等于32f 0 ; U1 为输入,频率为f0 ; j 为异或门鉴相器的输出,它作为变模可逆计数器的方向控制信号;out 为加/ 减脉冲控制器的输出; U2 为DPLL 的输出,在相位锁定的频率为f0 , 相位与输入U1 相差Π/ 2 ; D、C、B 、A 可预置变模可逆计数器的模数,它在0001 ―1111 范围内变化, 相应的模数在2.3 ―2. 17 范围内变化; En 为可逆计数器使能端。

图2 数字锁相环原理图

2. 1 鉴相器的设计

异或门鉴相器用于比较输入信号u1 与数控振荡器输出信号u2 的相位差, 其输出信号ud 作为可逆计数器的计数方向控制信号。当ud 为低电平时( u1 和u2 有同极性时) ,可逆计数器作加计数。反之,当ud 为高电平时,可逆计数器作减计数。

当环路锁定时, f i 和f o 正交,鉴相器的输出信号Ud 为50 % 占空比的方波,此时定义相位误差为零,在这种情况下,可逆计数器加和减的周期是相同的,只要可逆计数器只对其时钟的k 值足够大( k> M/ 4) , 其输出端就不会产生进位或借位脉冲, 加/ 减脉冲控制器只对其时钟2Nf o 进行二分频, 使f i和f o 的相位保持正交。在环路未锁定的情况下, 若Ud = 0 时它使可逆计数器向上加计数,并导致进位脉冲产生, 进位脉冲作用到加/ 减脉冲控制器的加控制端i , 该控制器便在二分频过程中加入半个时钟周期, 即一个脉冲。反之, 若Ud = 1 时, 可逆计数器进行减计数, 并将反出解围脉冲到加/ 减脉冲控制器的减输入端d ,于是,该控制器便在二分频过程中减去半个时钟周期,即一个脉冲。这个过程是连续发生的。加/ 减脉冲控制器的输出经过除N计数后。使得本地估算信号U2 的相位受到调整控制,最终达到锁定的状态。[p]

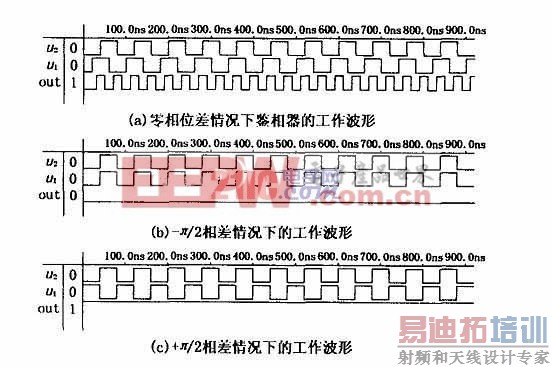

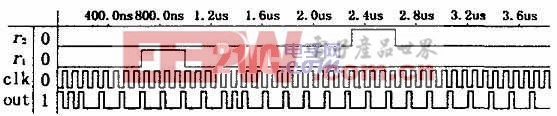

异或门鉴相器在环路锁定时和相位误差达到极限时的相应波形如图3 所示:

图3 异或门鉴相器工作波形

2. 2 数字环路滤波器的设计

数字环路滤波器是由变模可逆计数器构成的。该计数器设计为一个17 位可编程(可变模数) 可逆计数器,计数范围是,由外部置数DCBA 控制。假设系统工作无相位差,由锁相环原理知, u1 和u2 的相位差0 ,异或门鉴相器输出是一个对称的方波,如图4 (a) 所示。因此可逆计数器在相同的时间间隔内进行加或减计数,只要k 足够大,那么从零开始的计数就不会溢出或不够。

若u1 开始落后u2 ,异或门输出不对称,那么计数器加计数时间比减计数时间长,其结果计数器随着时间的增长将溢出,产生一个进位脉冲。相反,若U1 开始滞后U2 ,计数器将产生一个借位脉冲。进位和借位脉冲可用来控制DCO ,使得DCO 输出的脉冲数根据进位和借位来加上或者是删除一些脉冲,实际上也就改变了DCO 的输出频率。变模可逆计数器的设计由VHDL 完成,程序如下:

library ieee ;

use ieee. std_logic_1164. all ;

use ieee. std_logic_unsigned. all ;

entity li is

port (clk ,j ,en ,d ,c ,b ,a :in std_logic ;

r1 ,r2 :out std_logic) ;

end li ;

architecture behave of li is

signal cq ,k ,mo :std_logic_vector (16 downto 0) ;

signal cao1 ,cao2 :std_logic ;

signal instruction :std_logic_vector (3 downto 0) ;

begin

instruction = d c b a ;

with instruction select

mo ="00000000000000111"when"0001",

"00000000000001111"when"0010",

"00000000000011111"when"0011",

"00000000000111111"when"0100",

"00000000001111111"when"0101",

"00000000011111111"when"0110",

"00000000111111111"when"0111",

"00000001111111111"when"1000",

"00000011111111111"when"1001",

"00000111111111111"when"1010",

"00001111111111111"when"1011",

"00011111111111111"when"1100",

"00111111111111111"when"1101",

"01111111111111111"when"1110",

"11111111111111111"when"1111",

"00000000000000111"when others ;

process (clk ,en ,j ,k ,cq)

begin

if clk'event and clk = '1'then

k = mo ;

if en = '1'then

if j = '0'then

if cq k then cq = cq + 1 ;

else cq = (others = > '0') ;

end if ;

else

if cq > 0 then cq = cq - 1 ;

else cq = k ;

end if ;

end if ;

else cq = (others = > '0') ;

end if ;

end if ;

end process ;

process (en ,j ,cq ,k)

begin

if en = '1'then

if j = '0'then

f cq = k then cao1 = '1';

else cao1 = '0';

end if ;

cao2 = '0';

else

if cq ="00000000000000000"then

cao2 = '1';

else cao2 = '0';

end if ;

cao1 = '0';

end if ;

else cao1 = '0';cao2 = '0';

end if ;

end process ;

r1 = cao1 ; r2 = cao2 ;

end behave ;

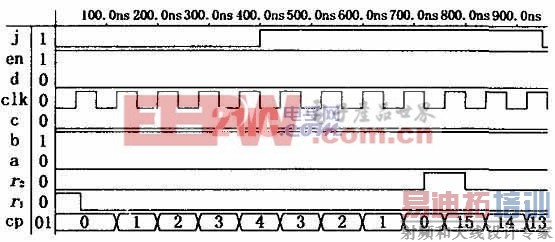

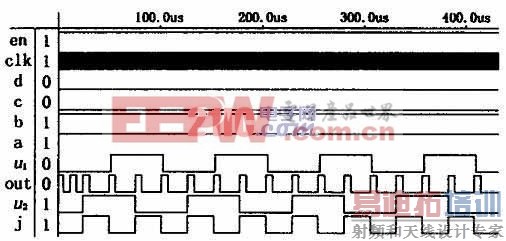

变模可逆计数器(取k = 24) 的仿真波形图如图4 所示。

图4 变模可逆计数器(取k = 24) 的仿真波形图[p]

2. 3 数控振荡器的设计

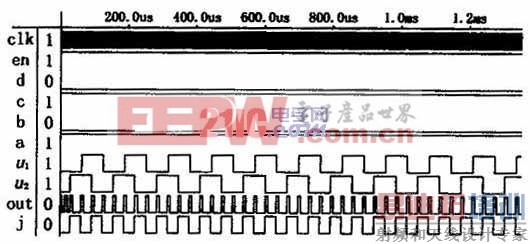

数控振荡器由加/ 减脉冲控制器和除N 计数器组成的。加/ 减脉冲控制器其实是一个增量―减量计数器式DCO。它和环路滤波器连用。如果在环路滤波器无进位、错位的时候,加/ 减脉冲控制器对时钟2NFo 进行二分频。当加/ 减脉冲控制的增量输入端( I = 1) 输入一个进位脉冲时, 输出脉冲中通过该计数器内部加上一个时钟脉冲。反之,当加/ 减脉冲控制的减量输入端( D = 1) 时输入一个借位脉冲输出脉冲中就减去一个时钟脉冲。因此通过借位和进位脉冲可以使输出频率得到改变, 输出频率能被进位和借位脉冲的最高频率控制在一个给定的范围内。加/ 减脉冲控制器由D 触发器和J K 触发器构成,根据功能分析,可以设计出相应的VHDL 程序。其运行后仿真波形如图5 所示:

图5 加/ 减脉冲控制器仿真波形图

3 实验仿真结果与分析

本设计中全数字锁相环路采用软件来实现的,通过用VHDL 语言编写模块,然后仿真,例化,逐渐由下而上的实现整个电路,最终达到整体仿真下载成功。

环路锁定( k = 2^5) ,DPLL 系统仿真波形如图6所示。

图6 环路锁定(取k = 2^5) 时的仿真波形

由仿真波形可以看出, u1 和u2 达到锁定状态时的仿真时间是70us。

环路锁定( k = 27) 时,DPLL 系统的仿真波形如图7 所示:

图7 环路锁定(取k = 27) 时的波形仿真图

在这种情况下, u1 和u2 达到锁定状态的仿真时间是180ms。

显然,模k 愈大,环路进入锁定状态的时间越长。k 取得过大,对抑制噪声、减少相位抖动有利,但是同时又加大了环路进入锁定状态的时间。反之, k 取得过小,可以加速环路的锁定,而对噪声的抑制能力却随之降低。

4 结语

采用VHDL 设计全数字锁相环路,具有设计灵活,修改方便和易于实现的优点,并能够制成嵌入式片内锁相环。该类数字锁相环路中计数器的模数可以随意修改,这样,就能够根据不同的情况最大限度地、灵活地设计环路。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电子密码锁的EDA技术设计方案

下一篇:光电PCB技术简介