- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的语音信号LPC参数提取算法的实现

关键词: 部分相关系数舒尔递推算法FPGA 并行处理技术

随着语音技术应用的发展,越来越多的语音信号数字处理系统需要按照实时方式或在线方式工作,特别在嵌入式系统设计中,对系统的硬件环境要求更高。随着语音处理算法的日益复杂,用普通处理器对语音信号进行实时处理,已显得力不从心。本文将采用新一代现场可编程门阵列FLEX10K系列的FPGA芯片实现语音信号的LPC分析,并通过舒尔(Schur)递推算法,提取语音信号处理中的重要参数――部分相关系数,即PARCOR系数。

1 LPC分析及舒尔递推算法

1.1 LPC分析基本原理

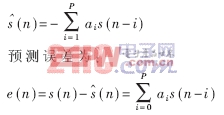

线性预测分析(LPC)是对一给定的时域离散线性系统用输出信号的过去值的线性组合来估计即将到来的输出值。即某一时刻n的语音信号的估计值为:

按均方误差最小准则,即LMS算法,可求得预测器最佳预测系数ai应满足下列方程组:

这组方程称为LPC正则方程,其中R(l)称为自关函数,它们是进行LPC分析的基础。

1.2 舒尔递推算法

将正则方程作适当变换,定义一个变量Ql(m)如下:

其中r(l)=R(l)/R(0)为归一化自关函数。

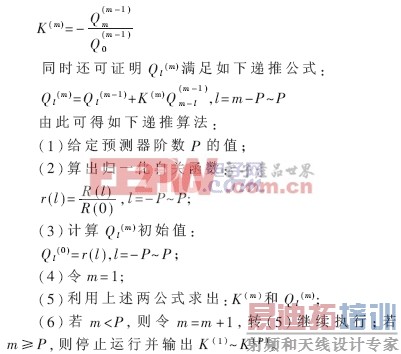

根据Ql(m)的性质和正交定理[1]可证明部分相关系数K(m)与Ql(m)有下列关系:

由于部分相关系数K(1)~K(P)与最佳预测系数a1(P)~aP(P)间存在简单对应关系,因而部分相关系数K(m)被广泛应用于语音识别、语音合成和低速语音编译器中。[p]

2 系统设计

2.1 系统总体设计

由于语音信号具有短时平稳性,因此在进行处理时需进行分帧处理,然后逐帧对语音信号进行LPC分析。本系统中,语音信号S(n)的精度为12位,采样率为20k,帧长为10ms,相应于每帧有200个采样点,每帧提取的部分相关系数K(m)的阶数取为12。

对取出的每帧语音S(n)还需进行加窗处理,即用窗函数W(n)乘S(n),形成加窗语音信号SW(n)。为减小Gibbs效应的影响,本系统采用的窗函数为哈明窗。

为实现语音信号的LPC分析过程,选择FLEX10K系列中的EPF10K100器件作为目标芯片进行设计,因其具有独特的嵌入式阵列块EAB而特别适合于对数字信号进行处理[2-4]。系统设计中,采用自顶向下的设计思想,在顶层采用电路原理图的设计方法将系统分为几个功能模块,在底层则采用VHDL语言来实现各功能模块的设计。为保证系统整体的处理速度,电路设计采用了流水线作业方式,以数据流驱动各模块协调工作,同时在一些影响系统整体速度的环节采用了并行处理技术,很好地解决了制约系统速度的“瓶颈”。

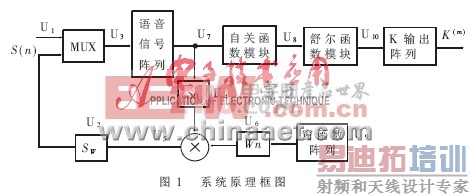

系统的原理框图如图1所示。图中U3、U10分别为由EAB构成的200×12bit和12×12bit的双口RAM阵列;U9为由EAB构成的200×12bit的ROM查找表,内置n=0~199的窗函数值W(n);U2、U4、U6为数据缓冲器;U7、U8分别为自关函数模块和舒尔递推算法模块;U1为多路转换开关;U5是12位乘法器。

系统工作原理如下:将一帧语音信号S(n)经U1送入U3,同时启动加窗过程,窗函数值W(n)通过查找ROM表U9获得,将取出的Wn和Sn送入乘法器U5相乘,乘积经U2和U1又送回U3,得到加窗语音信号SW(n),然后将SW(n)送入自关函数模块U7算出归一化自关函数r(n),再将r(n)送入舒尔递推模块求出部分相关系数K(m),存入U10。至此,一帧数据的LPC分析即告结束。

2.2 自关函数模块

自关函数的计算是影响系统速度的关键环节,它要进行大量的乘积累加操作。为提高系统运行速度,将加窗语音信号SW(n)同时存入两组RAM,采用并行取数的方式,同时取出参与运算的两个量,进行乘法运算,运算结果立即送入累加器进行累加。而此时乘法器又可进行下一对数据的乘积运算。整个过程中,乘法器和累加器一直在并行工作,从而保证了系统的流水线操作持续进行,最大限度地保证了系统的运行速度。

自关函数模块的原理框图如图2所示。图中U1、U2为EAB构成的200×12bit的双口RAM阵列;U8是带清零功能的数据寄存器,U7为加法器,它们二者共同构成累加器,为保证中间运算结果的精度,累加器的宽度为32位;U3、U4、U6、U9、U10为数据寄存器;U5为12位乘法器,乘积为24位;U11为32位除法器,商取16位。

该模块的工作过程是:将前面得到的加窗语音信号SW(n)同时存入U1和U2,然后按要求从中同时取出两乘数Sn和Sn+l送入乘法器U5进行乘运算,将乘积作为一个操作数同U8中的数进行累加。U8起始值被置为零,以后的值就是各次累加的和,最后一次累加的结果就是自关函数R(l)的值。然后再将它的值送入U10,将它同U9中的R(0)相除即得归一化的自关函数值r(l)。整个过程中,由于采用了并行处理技术,乘法器U5和累加器U7与U8一直处于工作状态,从而保证了系统的高速运行。[p]

2.3 舒尔递推模块

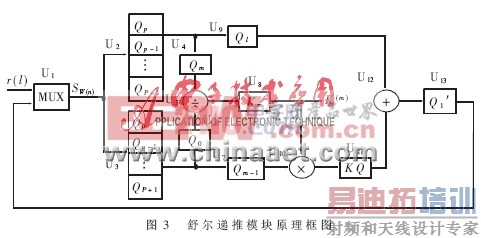

舒尔递推算法一个很重要的特点是在整个递推过程中全部参与运算的量的初值、中间值和最终值皆小于1,因此特别适宜于采用定点运算的硬件系统来实现。该模块的设计也采用双RAM结构和同时取数同时运算的并行处理技术,所有运算单元的精度都是16位,每处理一次递推过程,就输出一个K(m)值。

舒尔递推模块的原理框图如图3所示。图中U2、U3为12×16bit的双口RAM;U4、U6、U7、U8、U9、U11、U13为数据寄存器;U5、U10、U12分别为16位的除法器、乘法器和加法器;U1为多路转换开关。该模块的工作过程是:当归一化自关函数r(l)通过U1送入U2和U3后,立即从中取出Qm和Q0送入除法器U5进行除运算,除得的结果送入U8;与此同时又分别从U2和U3中同时取出Ql和Qm-l,将Qm-l与Km在U10相乘后,送入U11,接着与Ql在U12进行相加,将结果经U13、U1重新送回U2和U3,接着又进行下一轮递推,该过程一直要进行到递推阶数完成。在每一次递推过程中,当U12在进行当前数据的加运算时,U10就可进行下一个数据的乘运算。这样整个过程就可在连续的流水线方式不间断地进行。

2.4 算术运算单元

本系统所用到的算术运算单元有加法器、乘法器和除法器三种。加法器采用标准的全加器来构成,而乘法器则采用2的补码的BOOTH乘法器。下面介绍除法器的设计思想和工作原理。

由于本系统所使用的除法运算都是商小于1的除法,而且除法运算又比乘法运算少得多,因此对速度的影响也较小。综合考虑速度和资源占用两方面因素后,设计了下面的算法来实现除法器。设有两个数A和B,A是被除数,B是除数,现在求它们的商Q=A/B,Q1。现将Q表示成下列形式:

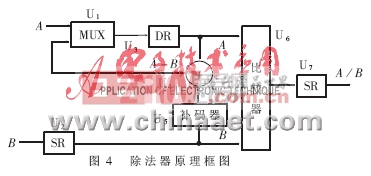

由于上述算法只需进行减法运算和除2运算,所以非常便于用硬件实现,据此算法设计的除法器原理框图如图4所示。图中U2为并入并出移位寄存器,每右移一位,实现一次除2操作;U5为补码器,它由反相器和加一电路构成,用于对B求补码;U7为串入并出移位寄存器;U6为比较器,用于对A、B两输入数进行比较,若A≥B,则输出“1”,否则输出“0”;U3为数据寄存器;U1为多路转换器;U4为加法器。该电路按下述原理工作:被除数A经U1送入U3并加到比较器U6的A端,除数B送入U2后右移一位再加到U6的B端。经U6比较后,若输出“1”,则先将U6的输出移入移位寄存器U7,再将A与B送入由U4和U5组成的减法器进行减法运算,所得差值再经U1送入U3;若输出为“0”,则仅将U6的输出移入U7即可。该步完成后,又将U2右移一位,再重复上述过程。整个操作一共要进行K次,最后U7中的数即为A/B的商。

在本系统中,将LPC分析与FPGA技术结合,充分利用了FPGA作为一种快速、高效的硬件平台在数字信号处理领域所具有的独特优势,实现了语音信号特征参数的快速提取,为语音信号的进一步处理打下基础。本系统采用50MHz的时钟频率进行工作。为考察其工作性能,对其整体性能指标进行了评估。由于影响整个系统速度的是乘法累加运算,因此它的工作性能也就决定了系统的性能。在求归一化自关函数r(l)过程中,涉及到近200次的乘积累加,采用并行处理技术和流水线操作方式的FPGA则可以用接近50MHz的数据速率进行工作,整个系统的性能同其他芯片相比约提高40%~60%,因此用FPGA技术来处理语音信号具有得天独厚的优点。

本系统除具有处理速度快的特点外,还具有独立灵活的输入输出接口及一组检测和控制信号线,可以方便地同任何一种处理器直接连接。由于FPGA自身所具有的抗干扰能力强、可靠性高的优点,本系统可广泛应用于自动控制、工业机器人、语音合成和语音编译码等领域,特别对嵌入式系统的设计具有重要意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...