- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用PLD简化边界扫描测试

引言

随着JTAG标准IEEE1149.1的定型,及随后开始在集成电路Intel 80486中采用,边界扫描测试已被广泛应用于测试印刷电路板的连接,以及在集成电路内进行测试。边界扫描测试受到设计人员的欢迎,因为它能够在线测试,而无需昂贵的钉床在线测试设备。然而,在大的电路板上,边界扫描链路很长,电路板设计人员面临着多种挑战,诸如故障检测和隔离、测试时间、物理布线,同时还要管理偏移,电压转换和满足各种特殊需要。传统上使用ASSP来应对这些挑战,然而基于ASSP的解决方案更为昂贵,有固定的电平和一些端口,不允许任何的定制,还要手工干预。本文主要探讨如何利用可编程逻辑器件作为一个颇具吸引力的选择,以解决大的电路板上与边界扫描测试相关的挑战。

电路板设计人员面临的边界扫描挑战

在电信和网络路由设备中使用的那些大的电路板通常包含许多有边界扫描功能的器件。在这些板上实施边界扫描测试时,设计人员通常面临着以下挑战:

故障检测/隔离

测试长的扫描链路是困难的,因为在一个扫描链路上的故障可能会导致整个系统不能进行测试。此外,由于这些器件是处于菊花链之中,测试系统以链路中最慢的器件的速度运行。 这既增加了测试时间,还增加了成本。

物理布线至平衡时钟偏移

虽然扫描测试数据端口为菊花链输入,典型的控制信号,如TCK(测试时钟)TMS (测试模式设置) 和TRST(测试复位) 是直接分配的,从测试端口到扫描链路中的每一个器件。图1展示了边界扫描测试的一个典型的安排。当扫描链中器件的数量增加时可以观察到偏移的影响。解决这个问题的最常见的方法是要增加缓冲器,以便管理板上的偏移,但是这样做增加了成本和复杂性。

图1:典型的边界扫描链路

电压转换

边界扫描I / O电压应该与扫描链路中连接器件之间的电压相兼容。然而,电路板上器件的I / O的信号电平往往是不兼容的。为了解决这个问题,设计人员通常添加电压转换器件。图2展示了这样一个扫描链路,其中元件具有不同的I / O电压。当一个器件的I / O电压与链路中的下一个器件的I / O电压不同时,已在扫描链路中插入一个电压转换器。在这个例子中,根据 I / O的电压,在扫描链路中的器件已放在一起。当器件的I / O电压不能放在一起时,更多的电压转换器可能需要插入到扫描链。

图2:工作在不同I / O电压的器件的扫描链路

[p]解决特殊要求

在扫描链中的一些器件通常有特殊的要求。例如,一块电路板上可能同时拥有ASIC / ASSP器件和可编程逻辑器件。ASIC / ASSP器件只能够工作在一个模式,要么是主模式,要么是从模式。通常根据对JTAG主方的用户输入,需要边界扫描控制器从一种模式切换到其他的模式。同样,往往通过JTAG接口对可编程逻辑器件进行配置,有可能需要实现自定义逻辑,对两个不同的JTAG主方进行选择,一个用于测试,而另外一个用于对可编程逻辑器件进行配置。有一些特殊要求的实例,根据个案情况必须采取不同的管理方法,而且往往需要额外的外部硬件。

针对边界扫描控制的基于ASSP的解决方案

设计人员通常用ASSP来应对以上所述的挑战。 ASSP改进了大型电路板上的故障检测和隔离,不再把较长的扫描链路划分成更小的链路。但是,仍然存在着许多与使用ASSP相关的问题:

ASSP不能去除使用电压转换器, ASSP有固定的电平,不支持较新的低电压I / O接口。因此仍然需要电压转换器。

ASSP并不能去除需要缓冲, ASSP有固定的端口,这意味着在较大的子链路上仍然会观察到偏移效应。

自定义的单芯片解决方案并不可行 - ASSP需要额外的逻辑来解决特殊的要求。

ASSP需要大量的人工干预,这些解决方案中,设计人员必须改变电路板的跳线设置,添加或删除子链路。因此需要大量的人工干预,以便进行调试和生产测试。

针对边界扫描控制的基于PLD的解决方案

现在很多设计人员在大的电路板上使用PLD实现边界扫描控制。在一个典型的可编程逻辑器件的边界扫描控制应用中,设计人员在PLD中实现多边界扫描端口连接器。将多个端口扫描连接在一起的关键是将一个长的扫描链路划分成更小的子链链路。将长扫描链路划分成更小的子链路,通过软件控制添加或删除子链路,这样使得故障检测和隔离更加容易。有特殊要求的器件可以放置到单独的子链路,使复杂的系统变成简单的测试。为了改进测试时间,设计人员经常将慢的器件放至单独的子链路,针对较慢的和更快的子链路,使用不同的测试时钟。

现代PLD拥有多个I/ O bank,可单独配置以支持I/O工作在不同的电压。例如,莱迪思半导体公司的MachXO PLD具有能够放置LVCMOS输入到任何I / O bank的功能,因此可以方便地通过可编程逻辑器件实现电压转换。

针对LVCMOS输出,一些PLD提供能够调整驱动强度的功能。设计人员利用这个功能来增加高扇出控制信号的驱动能力。通过将长的扫描链路分成较短的子链路,以及增加高扇出信号的驱动强度,设计人员去除了缓冲控制信号。这可以简化电路板的布局,因为电路板设计人员不必构建精确的偏移匹配网络来分配高扇出信号。同样,通过减少电压转换和连接要求,设计人员可以降低对电路板面积的要求,使得布线有更大的余地。

PLD用于边界扫描控制的电路板通常包括FPGA。使用JTAG接口对FPGA进行配置时,设计人员还在执行边界扫描控制的可编程逻辑器件中实现了复用器逻辑。这提供了一个更大的系统集成度。通过去除电压转换器、缓冲器和实现定制解决方案的额外逻辑,可编程逻辑器件提供比ASSP成本更低的解决方案。通过JTAG主方软件,可控制添加和删除子链路,因此减少了人工干预。

边界扫描控制器的应用

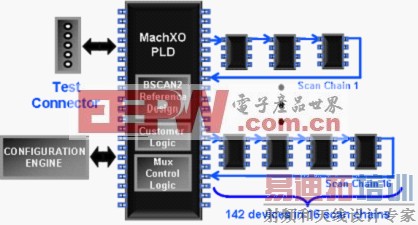

图3展示了可编程逻辑器件用于边界扫描控制应用的实例。在这个例子中,莱迪思的MachXO – 640器件用来实现多边界扫描端口连接器,在16个子链路中将142个器件连接在一起。该MachXO器件还实现了多路逻辑,可以在测试接口和配置接口之间进行选择。在同一个PLD中,其余的查找表被用来实现额外的用户逻辑。

[p]此应用使用莱迪思的多个边界扫描端口连接器(BSCAN2)参考设计。BSCAN2参考设计可免费从莱迪思的网站上下载,根据应用的需要,可以对HDL源代码进行修改。该参考设计允许连接多达8个子链路到一个边界扫描测试接口。多个BSCAN2示例可以级联在一起,以增加可用的子链路的数目。这个设计使用两个BSCAN2示例实现16个子链路。BSCAN2还可以启用不同的测试时钟用于每一个子链路。此功能是用来加速电路板调试和生产测试,导致电路板的制成时间减少了60%。

图3:在边界扫描控制应用中的MachXO - 640

总结

基于PLD的边界扫描控制解决方案将一个长的扫描链路划分成更小的子链路,改进了故障检测和隔离。通过去除电压转换器和缓冲器,在同一块集成电路中整合了定制逻辑,加强了自动化功能,可编程逻辑器件提供了一个优越的替代ASSP的方案。基于PLD的解决方案使设计人员降低了电路板的成本,简化了电路板的布局,减少了测试时间,并支持更大的系统集成。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...