- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的PCI硬件加解密卡设计

摘要:提出一种基于FPGA的PCI硬件加解密卡的设计方案,用硬件加解密取代了传统的软件加解密,将加解密模块和PCI接口模块集成在一个FPGA芯片内实现。分析了PCI加解密卡的软硬件的结构和原理,详细介绍了DESX加解密算法的原理、步骤和硬件实现、PCI接口模块的IP核设计以及USB接口模块的电路连接。系统硬件以FPGA为核心,使用QuartusII7.2软件和VHDL语言设计,软件由DriverStudio2.7和VisualC++6-.0设计。采用192位密钥的DESX分组对称加解密算法来取代64位DES算法,密文和密钥在专用硬件中存储,计算机内只有明文,有效防止黑客攻击,保护数据安全。设计采用逻辑综合式取代时钟驱动级联式来实现DESX算法,使加密一组数据的时间由16

个周期缩短为1个周期。

关键词:DESX算法;硬件加解密;FPGA;PCI;USB

数据加解密分为软件加解密和硬件加解密两种。目前,采用软件加解密的方法对数据进行加解密较为普遍,原因是软件加解密方法实现起来较为简单和经济,但其弱点是软件加解密的明文、密文和密钥都需要在计算机内存储,容易被窃取、攻击和破译,难以应用到需要高级保密的商业机密和军事机密中。硬件加解密可以较好解决软件加解密的不足。硬件加解密的密文和密钥可以在专用硬件中存储,计算机内只有明文,而且硬件加解密基于硬件层处理,CPU不参与加解密的执行过程,不会占用系统资源。因此使用硬件加解密方法,更为安全可靠,是保证数据安全的根本方法,适用于军事机密和高级商业机密。

但同时硬件加解密实现起来较为困难,主要表现在其较高的生产成本、加解密的硬件实现、加解密速度的提高。以及在调试时不易做分级验证等。另外,在本PCI加解密卡的接口模块设计中用到了复杂的USB、PCI协议,增加了开发的难度。

1 设计思想

PCI硬件加解密卡是基于加解密器件和PCI总线技术的安全保密设备,为重要的计算机信息提供加密、解密、存储和分发的功能,有效防止机密信息的截获和破译,可以应用在需要高级保密级别的商业和军事领域。系统采用硬件加密方式对数据进行加密存储和解密读取。加解密过程在专用硬件中进行,加密强度较高。系统最大特点是密钥和密文均不在计算机中存储,而是存储在专用硬件中,计算机中只存有明文,可有效防止窃取、攻击和破译。

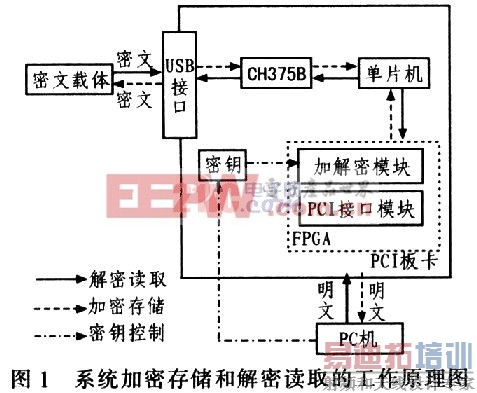

加密操作时,PC机的明文数据通过PCI接口传输到FPGA内的加解密模块进行硬件加密,加密后的密文通过USB接口送到密文载体中存储和分发。解密操作时,数据的传输过程相反。加解密算法采用DESX分组对称密钥加密算法.密钥为192位二进制数,与传统的DES相比,更为安全、可靠。密钥存储在PCI卡上的非易失存储器(EEPROM)中,当密钥由于不再安全或者过期等原因需要更新时,通过执行相应软件来更新EEPROM上的密钥信息,而不需要拆卸硬件。系统加密存储和解密读取的工作原理图如图l所示。

2 系统硬件结构和实现

2.1 硬件结构

加解密卡为PC机PCI卡形式,通过PCI插槽与PC机相连,密文载体与PCI卡的USB接口相连。其硬件主要由三部分组成:加解密模块、PCI接口模块和USB接口模块。其中,加解密模块和PCI接口模块在FPGA内实现,FPGA型号是EP1C12Q240C8,设计软件为QuartusⅡ7.2,采用自顶向下(Top-Down)的实现方式,编辑语言为VHDL。

2.2 加解密算法的硬件实现

硬件加解密是本系统的核心部分。DES算法在加解密和密钥生成过程中全部使用逻辑运算和查表运算,FPGA在实现算法方面具有灵活性、物理安全性和比软件更高的速度,而且可移植性好,便于升级,因此FPGA已成为硬件实现DES算法的最佳选择。[p]

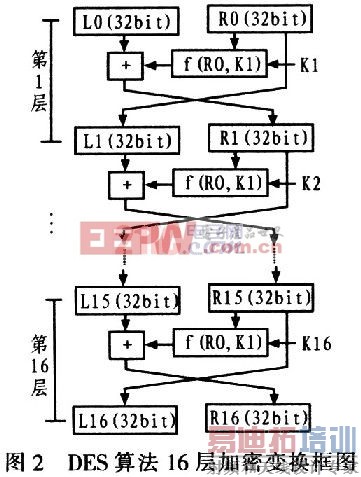

DES算法的加密过程分为4步:初始置换、迭代过程、子密钥生成和逆置换。DES算法16层加密变换框图如图2所示。

若采用时钟驱动级联式来实现DES算法,数据在时钟的驱动下从上一级的输出送入下一级循环的输入,那么对同一组数据完成加解密需要16轮时钟循环,至少需要16个时钟周期才能完成,加解密时间长。为了提高速度,采用了逻辑综合式进行DES设计。采用循环嵌套展开的方式完成16轮循环。利用编译综合器将16轮循环的整体逻辑结果用等效的逻辑电路来实现,当输入数据和密钥有效后,逻辑直接输出16轮循环的逻辑结果,使加密一组数据的时间由16个周期缩短为1个周期,时间延迟仅仅取决于电路的逻辑延迟。这种方法的缺点是占用了较多的系统资源,而且开发过程中不易做分级验证。

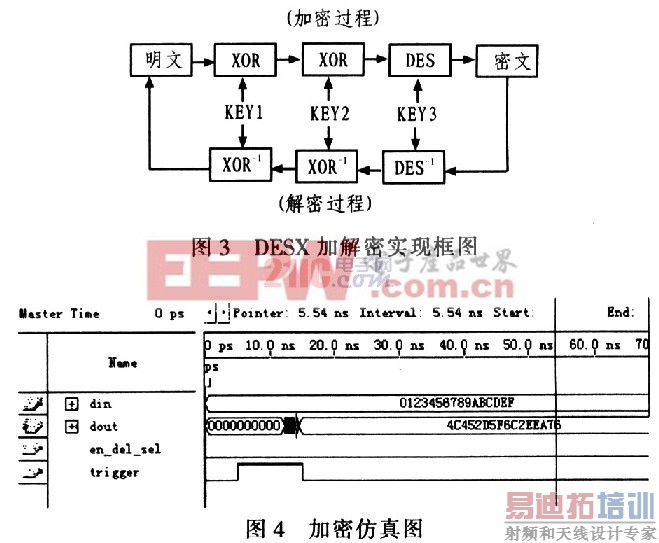

本系统使用的DESX算法是在DES基础上改进的加密算法。将DES的64位密钥扩展到192位,即使用3把64位的密钥。KEYl、KEY2和KEY3对数据块进行3次加密,充分保证了数据的安全。DESX加密过程分为3个步骤:1)使用KEYl对数据块做XOR运算;2)使用KEY2对上一步的结果再做XOR运算;3)使用KEY3对第二步的结果进行DES加密从而得到密文。与DES和3DES相比,只做一次DES运算。但密钥长度提高到192位,在保证安全性的前提下,最大限度提高了加解密的执行效率。DESX的解密过程与加密过程相反,其加解密流程如图3所示。图4是对数据0x0123456789-ABCDEF进行加密测试的仿真图,其系统时钟为50 MHz。

2.3 PCI接口模块设计

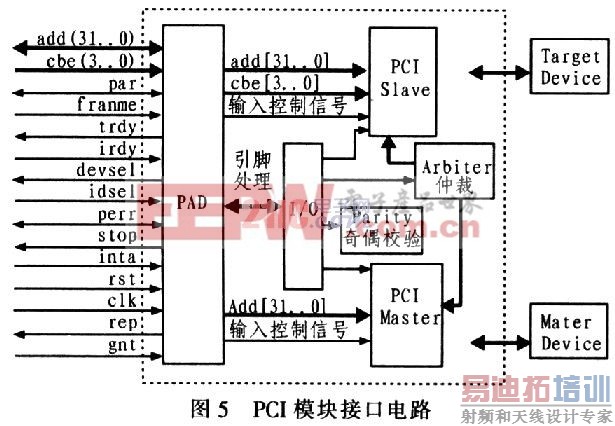

PCI接口模块是PCI总线与加解密卡之间的转换接口,也可认为其主要功能是起一个桥梁作用,完成用户设备与PCI总线之间的数据传输。从技术要求和成本方面考虑,以及本数据采集卡的特点,可以将加解密模块和PCI接口模块在一个FPGA内实现,用户可以按需要进行配置,而且提高了系统集成度,可移植性好。

PCI接口模块采用自顶而下的设计方法,在数据流和控制流分析的基础上,按照PCI接口的内部逻辑功能及结构,分成几个单独的模块,结构清晰,便于单独模块的测试。在设计PCI接口模块时,需要考虑支持PCI总线协议中的有关内容。PCI接口模块可以只包含PCI-Slave(从PCI),也可以选择同时包含PCI-Mater(主PCI)。其中,PCI-Slave是接口模块必须的,PCI-Mater是可选的,但是如果实现PCI-Mater,则Arbiter(仲裁器)就是必须的。完整的PCI接口模块电路如图5所示。

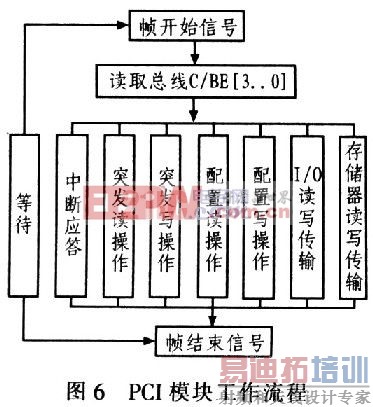

PCI接口模块的核心设计分为时序控制和配置空间两部分。时序控制部分保证了板卡能按正常的PCI时序工作,配置空间部分保证了PCI卡的即插即用功能。在时序控制程序中采用状态机模型来实现不同时序的转换,各种命令、数据交换、控制均在状态机的管理下进行工作。本设计中的状态机主要由中断应答、突发读操作、突发写操作、配置读操作、配置写操作、I/O读写传输、存储器读写传输等7个部分组成,工作流程如图6所示。

[p]

2.4 USB接口模块设计

本系统的USB选用CH375B,工作于USB-HOST主机方式,采用并行接口。在USB主机方式下,CH375B支持各种常用的USB全速设备,外部单片机需要编写固件程序按照相应的USB协议与USB设备通讯。USB接口模块电路图如图7所示。

CH375B并行接口信号线包括:8位双向数据总线D7~DO、读选通输入引脚RD#、写选通输入引脚WR#、片选输入引脚CS#、中断输出引脚INT#以及地址输入引脚A0。CH375B的RD#和WR#可以分别连接到单片机的读选通输出引脚和写选通输出引脚,CS#由地址译码电路驱动,INT#输出的中断请求是低电平有效,可以连接到单片机的中断输入引脚,单片机使用中断方式获知中断请求。当WR#为高电平并且CS#和RD#及A0都为低电平时,CH375B中的数据通过D7~DO输出;当RD#为高电平并且CS#和wR#以及A0都为低电平时,D7~DO上的数据被写入CH375B中;当RD#为高电平并且CS#和WR#都为低电平而AO为高电平时,D7~DO上的数据被作为命令码写入CH375B中。

3 软件的设计与实现

软件主要分为驱动程序和应用程序两部分,分别用DriverStudio和Visual C++开发。驱动程序的设计关键是如何完成硬件操作。基本功能包括设备的初始化、IO端口的读写操作、内存读写操作、中断的设置响应和调用等部分。PCI卡插入主机时,从设备中读出产品ID(PlD)和厂商ID(VID),由这2个值来搜索匹配的inf文件,再由inf文件加载相应的驱动。应用程序通过调用Win32 API函数CreatFile来打开设备,然后使用DeviceloControl与驱动程序通信。在应用程序退出前使用CloseHandle关闭设备。DeviceIoControl使用不同的IOCTL命令来调用驱动程序完成不同的任务。

4 结束语

经测试,本PCI加解密卡数据加密存储速度为612 KByte/s,解密读取速度为630 KByte/s。FPGA使用情况:total logicelements 903l/12060(75%),total pin 84/173(49%)。在以后的设计中,应重点解决系统加解密速度较慢的问题,另外,FPGA和USB的选型、加解密算法的优化等有待改进。

本设计的创新点在于用硬件加解密方法取代了通常的软件加解密方法,采用更为安全可靠的DESX算法来弥补DES算法的不足,使用了FPGA的IP软核设计方法实现DESX加解密模块和PCI接口模块,提高了系统集成度,可移植性好,便于系统升级。在加解密速度方面,用逻辑综合式取代时钟驱动级联式,使加解密一组数据的时间由16个周期缩短为1个周期。本系统在需要高级保密的商业和军事领域,有着较好的应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...