- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FSL总线的UART外设IP核设计

引 言

在基于MicroBlaze的SOPC系统中,将用户IP核整合到基于MicroBlaze的嵌入式软核处理器系统中,通常有两种方法:一种是将IP核连接到OPB总线;另一种是将用户IP连接到MicroBlaze专用的FSL总线上。尽管OPB和FSL总线都是MicroBlaze软核与FPGA其他片上逻辑资源连接的主要途径,但它们的分工足不同的。OPB总线适用于将要求低速和低性能的设备连接到MicroBlaze系统中;而FSL总线则适用于将对时间要求高的用户自定义IP核,整合到基于MicroBlaze的软核系统中,以实现硬件加速。

在Xilinx公司提供的IP核中,有基于OPB总线的UART外设IP核,但是没有基于FSL总线的IP核,使得该UART外设在对时间要求高的系统中性能受到制约。在这种情况下,有必要设计基于FSL总线的UART外设,以使得UART能够在高速系统中发挥最佳性能。

Xilinx公司的MicroBlaze软核是支持CoreConnect总线的标准外设集合。MicroBlaze处理器可以运行在150MHz时钟下,提供125 DMIPS的性能,非常适合于设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1 MicroBlaze体系结构

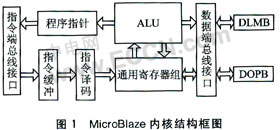

1.1 MicroBlaze内核结构

MicroBlaze是基于Xilinx公司FPGA的微处理器IP核,与其他外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据。内核结构如图1所示。

1.2 MicroBlaze的总线接口

MicroBlaze处理器软核具有丰富的接口资源。最新版本的MicroBlaze软核支持的总线接口有:

◆带字节允许的OPB(On_chip Peripheral Bus,片上外设总线)V2.0接口;

◆高速的LMB(Local Memory Bus,本地存储器总线)接口;

◆FSL主从设备接口;

◆XCL(Xilinx Cache Link,Xilinx缓存链路)接口;

◆MDM(Microprocessor Debug Module,微处理器调试模块)连接的凋试接口。

OPB是对IBM CoreConnect片上总线标准的部分实现,适用于IP核作为外设连接到MicroBlaze系统中;LMB用于实现对片上的BlockRAM的高速访问;FSL是MicroBlaze软核特有的一个基于FIFO的单向链路,可以实现用户自定义IP核与MicroBlaze内部通用寄存器的直接相连;而XCL则是MicroBlaze软核新增加的,用于实现对片外存储器的高速访问。MicroBlaze软核还有专门的调试接口,通过参数设置,开发人员可以只使用特定应用所需要的处理器特性。

2 基于FSL总线的UART IP核设计

UART(Universal Asynchronous Receiver Transmit-ter,通用异步收发器)是广泛使用的串行数据传输协议,允许在串行链路上进行全双工的通信。串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路(即UART)实现。8250、8251、NS16450 等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时并不需要使用完整的UART功能和这些辅助功能。如果设计上用到了FPGA器件,那么可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。

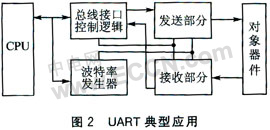

2.1 UART的典型应用

UART主要由数据总线接口、控制逻辑、波特率发生器、发送部分和接收部分等组成。UART内部所实现的功能包括微处理器接口、发送缓冲器、发送移位寄存器、帧产生、奇偶校验、数据接收缓冲器、接收移位寄存器等。UART的典型应用如图2所示。

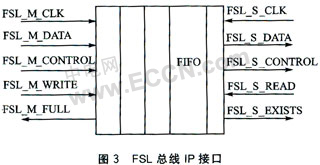

2.2 FSL总线接口

FSL总线是一个基于FIFO的单向点对点通信总线,主要用于FPGA的两个模块间进行快速的通信。FSL接口的I/O信号如图3所示。

该接口的主要特点:

◆单向的点对点通信;

◆非共享的无仲裁通信机制;

◆支持控制位与数据分离的通信;

◆基于FIFO的通信模式;

◆可配置的数据宽度;

◆高速的通信性能(独立运行达到600 MHz)。

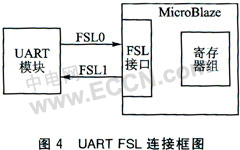

2.3 FSL总线UART硬件设计

设计中的主要内容是UART IP模块和MicroBlaze之间的FSL总线接口,该接口提供了UART模块与MicroBlaze之间通信的桥梁。Xilinx公司提供的IP核中包括基于OPB总线的UART模块,但是没有提供基于FSL总线的UART模块。如果设计中需要在UART模块和MicroBlaze之间进行高速交互,设计一个基于FSL总线的UART无疑是最佳的选择。UART经过FSL总线与MicroBlaze的连接如图4所示。

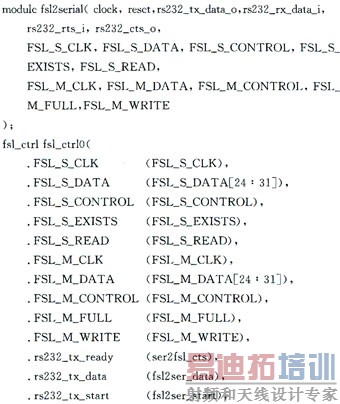

从图4中可以看出:对于FSL1,MicroBlaze是主设备,UART模块是从设备,MicroBlaze可以发送数据或者命令给UART模块;而对FSL0来说,UART模块是主设备,而MicroBlaze是从设备,UART模块可以发送数据给MicroBlaze来处理。FSL0和FSL1构成了一个FSL总线对,使得MicroBlaze和UART模块可以进行全双工通信。其设计的顶层实现部分代码如下:

2.4 FSL总线UART驱动设计

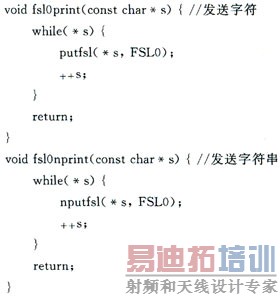

对用户自己设计的IP核来说,如果要集成到SOPC系统中,就必须为该IP核开发相应的驱动程序。驱动程序提供一组操作自定义IP核的操作宏,通过这些操作宏,软件程序开发者可以在高层对IP核进行操作。本设计中的驱动程序,提供了串口对字符或者字符串的发送和接收,用C语言来设计。部分驱动代码如下:

3 FSL总线UART外设IP核的验证

3.1 硬件平台

无论基于何种总线,用户开发的IP核开发完毕之后,都要组建一个基本系统对IP核进行验证。这个基本系统要包含必要的外设,重点对IP核的性能进行测试。如果在测试中发现错误,则需修改错误然后导入到系统中,再进行测试,直到满足基本功能、达到设计预期目标为止。如图5所示,本验证平台包括以下处理器和外设:MicroBlaze,数据指令BRAM,调试模块,DCM模块和用户IP模块。特别注意,增加了2条FSL总线组成一个FSL总线对,用于用户IP与处理器进行通信。

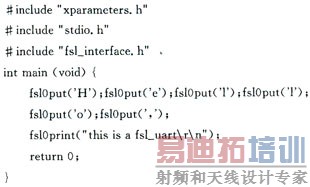

3.2 软件开发

在上述硬件平台基础上,开发一个基本的C程序,对FSL总线UART进行测试。代码如下:

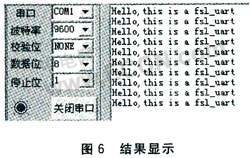

打开串口调试工具,观察到的结果如图6所示。

通过验证,所设计的基于FSL总线的UART外设IP核达到预期目标,可以集成到SOPC系统中正常工作。

结 语

通过本文的设计,给广大SOPC设计人员一个提示:设计基于FSL总线的外设IP核,并通过FSL总线集成到SOPC系统中,可以显著提高系统性能,而且设计过程不是很复杂,比较容易实现。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于Verilog

HDL的异步FIFO设计与实现

下一篇:消除状态机毛刺策略探讨