- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

系统控制器免费IP 核的应用

1.前言

随着集成电路业工艺的发展,单位面积晶体管的数量急剧增加。按传统的方法,能满足芯片功能和时序要求设计的IC设计工程师,产能约为100门/天,要完成 1200万门的芯片设计需要500人年。设计复用(Design Reuse)技术成为解决问题的有效方法。根据业界经验,任何模块如果不作任何修改就可以在10个或更多项目中复用,都应该开发成IP 。基于IP的数字IC设计方法是有效提高设计产能的关键技术。IP核又称IP (Intellectual Property)Core指具有独立知识产权的电路核。设计复用不但适用于ASIC设计,也适用于CPLD/FPGA。在该类电路设计过程中,由于开发工具的通用性、设计语言的标准化,使得设计过程基本与器件硬件特性无关,成功设计的各种功能电路模块(core)具有很好的兼容性(Compliable)和移植性(Portable),恰当的复用使设计效率大大提高。

用于系统集成(Integration)的IP Core通常是私有的,必须向开发商购买,这些花费对资金短缺的设计团体来说是很大的负担。而特殊的设计及测试工具给私有IP Core的整合带来一些困难。有时私有IP Core还可能缺乏足够的文档,且购买者无法得到源代码使得整合工作更加困难。以上原因使IP core 的推广没有预想地那样顺利。

作为一种尝试,国际上一些非盈利组织(如Opencores等)和个人致力于自由(或称免费,Open 或Free)IP Core的发展,为设计者提供遵循GNU GPL或LGPL 协议的免费开源IP core。本文以系统控制器(system controller)的IP核为例,介绍了免费IP Core的使用,包括资源的获取方式和工具,文档的应用,测试方法等问题,希望以此引起设计人员对免费资源的关注。本文的资源来自Opencores组织。

2.资源的获取

免费IP Core资源通常由非盈利性组织或个人提供,有些CPLD/FPGA芯片厂家也提供部分类似资源,但因大多是针对某个特定的芯片,所以可移植性较差。本文主要关注以发展免费开源IP核为宗旨的Opencores组织提供的资源,该组织也是免费IP开发中最有影响的组织之一。

Opencores是国际上成立较早、比较有影响的组织,致力于LGPL(GNU Lesser Public License)协议下设计和发布IP Core,以保证设计资源能被自由免费使用。该组织还制定和发展开放式IP Core设计标准及平台,为用户提供关于设计资源和平台完备的文档支持。

该组织官方网站上的资源以CVS工具管理,设计人员可以直接通过CVS工具或HTTP下载该组织提供的所有资源。因其开发者会不断更新资源,所以网站推荐使用CVS软件整体下载资源 。该组织提供的资源包括算术模块、微处理器、存储器、协处理器、通信控制模块、DSP 核、系统控制器、视频控制器等电路模块。该组织维护管理的Wishbone总线标准(由Sillivore公司开发并移交)因其具有开放性,且有丰富免费 IP Core资源支持,实际已成为免费IP Core设计的互连标准。该组织提供的OR1000处理器已被数家公司的开发系统(SOPC)采用并在ASIC上实现。

CVS(Concurrent Versions System)是国际上最成熟的版本控制管理系统。版本管理工具是指在软件开发过程中涉及到的各种软件资源的自动化管理工具。互连网上最大的开源社区SOURCEFORGE 就以它管理9万个项目。该管理系统包括客户端CVS和服务器端CVSNT。CVS最先只能工作于UNIX 或Linux平台,现已有Windows版本即WinCVS。WinCVS可从其官方网站下载。下载并安装WinCVS后,就可以从WinCVS访问 Opencores官方网站提供的资源,该网站提供相关资源所在服务器的配置信息和资源管理信息,使用者以所提供的信息,可以直接访问所需网站的指定资源,执行浏览、下载等操作。

完善的IP Core一般包含该电路核的源代码文件(VHDL或者Verilog HDL)、说明文件、用于仿真的测试向量文件、仿真结果及综合结果。以下以Opencores提供的系统控制器中的OCIDEC (OpenCores IDE Controller)为例,说明如何利用好该组织提供的免费IP Core资源。

系统控制器广泛应用于现代微计算机系统,控制特定电路设备与电路模块之间能进行正常工作,有时也称为接口电路。Opencores官方网站提供的系统控制器有AC 97 Controller,IDE Controller,OCIDEC,Memory Controller,PCI Bridge,RS232 Sy stem Controller等。

首先用WinCVS工具下载所需要的资源(此例的Module名为ata),下载到本地后的文件目录将有若干文件夹。其中CVS文件夹下文件由CVS版本控制系统自动产生,使用者可不去理会;bench文件夹下的文件为测试向量,用于对IP Core进行功能仿真;doc文件夹下为说明文件;rtl文件夹下为该IP Core的源代码,一般使用Verilog和/或VHDL语言书写;sim和syn文件夹下分别为仿真和综合的结果。由于应用者可能使用各种不同的仿真和综合软件,为使读者便于了解应用的过程,本文使用较为通用的软件Active-HDL和Synplify Pro作为处理工具。

3.资源的使用

3.1 了解IP Core的功能特性

要使一个他人所写的IP Core为自己的设计所用,首先要对其文档和特性做全面的了解。凡是Opencores组织提供的资源里均附有相应IP Core的说明(specifICation),该SPEC文件一般包含变动记录(Revision History)、功能特性简介(Introduction),IO及参数说明(IO Port & Parameter)、寄存器说明(Registers)、工作原理(Operation)、源代码文件结构(Architecture)等内容。

本例的SPC文件表明了该IP Core是WISHBONE总线兼容的ATA/ATAPI-5主控器。

ATA(AT Attachment)接口也称为IDE(Integrated Drive Electronic)接口,用来连接硬盘、CDROM/DVD、CF卡及PC卡等周边设备,并且SPEC内有详细的IO和寄存器描述。

[p]用EDA工具对IP Core分析验证

在---ata tlverilog目录下有两个子目录ocidec-1和ocidec-2,为该IP Core相互独立的两种源代码,分别用于支持CF/PCCard的简单ATA传输功能和快速ATA传输功能。使用者可以根据需要选用,并对所选的IP Core的源代码进行分析,了解其实现特定逻辑功能的编程方法,这也有助于对该电路核进行修改。该电路核能否正常工作只能通过仿真和测试来确定。主流仿真软件有Modelsim、Active-HDL、Cadence NC-Verilog/NC-VHDL等。 本文使用Active-HDL 6.3、Synplify Pro 7.7、Quartus II 4.2 Web Edition Full对ocidec-1进行了验证。

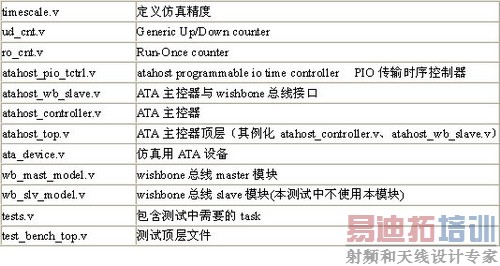

本例中bench目录下存放该电路核ocidec-1的测试文件(test_bench_top.v),可以用来对电路所实现的逻辑功能做仿真测试。由于资源是免费的,该文件里给出的测试向量可能是不完全的或只对部分电路功能做测试。如果要做更全面的测试,使用者要在分析源代码的基础上继续添加测试项来完善该测试文件。ocidec-1源代码文件如下表1。

表1 系统控制器OCIDEC-1 (OpenCores IDE Controller)的源代码文件

对ocidec-2的分析验证

本例从Opencores得到的测试文件只能对ocidec-1进行测试,作者没有提供对ocidec-2的测试文件。如果要使用ocidec-2核,使用者必须自行对ocidec-2测试。可以通过修改ocidec-1的测试文档或重新写测试文档。由于ocidec-2是对ocidec-1功能的加强,且该测试文件也包含了对ocidec-2功能的部分测试项,所以通过修改形成ocidec-2的测试文档比较省时。但是一般而言,一个测试文件只针对某一 IP Core,不同的IP Core应该有各自的测试文件。

4 结束语

免费IP Core可以用于教育,学术研究、商业等领域,充分利用这一丰富共享资源将带来巨大的价值。Opencores组织的调查表明:该组织的资源19.0%被商用,28.4%被用于教育,23.3%被用于研究,29.1%出于爱好使用。

免费IP Core的商业应用将减少开发成本和研发周期,缩短产品投放市场的时间;爱好者可以利用该资源来设计实现和验证自己的设想;在教育和研究领域对免费IP Core的使用将进一步完善其设计。但是从本文的例子也可以看出,免费资源并不是成熟或完善的资源,要妥善处理后才可以得以发挥作用。

参考文献

[1] 牛凤举,刘元成,朱明程. 基于IP复用的数字IC设计技术.北京:电子工业出版社.2003

[2] 徐剑. 版权开放:Copyleft的法学释义.上海:上海交通大学学报 2003

[3] 朱敏. 版本管理工具CVS概述.无锡: 高性能计算技术. 2 002

[4] 付燕,王玮,王福源. 免费IP核的应用.郑州:河南科技. 2004

[5] http://sourceforge.net/index.php

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...