- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用于CDR电路的相位插值选择电路设计

0 引言

在高速多通道串行收发系统中,由于数据在传输时会受到多种噪声的影响而失真,因此在接收端要进行时钟的恢复和数据的重定时,即时钟数据恢复(CDR)。然而由于工艺、电压的影响以及系统对功耗和抖动性能的要求,过去采用的各通道拥有独立锁相环路的方案已逐渐被设计者舍弃,取而代之的是双环时钟数据恢复环路。其基本思想是:时钟数据恢复单元的各个通道共享同一个锁相环,由该环路统一向各通道提供多相参考时钟,各通道的CDR环路则利用已经产生的多相时钟完成数据的重定时。这样既避免了由于不同锁相环输出时钟间的差异而造成系统性能的下降,又减小了芯片面积和系统功耗。 本文研究了时钟数据恢复环路中多相正交参考时钟的产生原理,根据所设计的2.5 Gbit/s CDR的要求,通过对传统正交时钟产生过程的分析,提出了一种新的相位插值一选择方案,并采用0.18μmCMOS工艺实现。在SMIC 0.18μm CMOS工艺下采用Spectre进行了验证,结果显示该电路有效地提高了输入抖动容限。

1 电路结构及产生方案

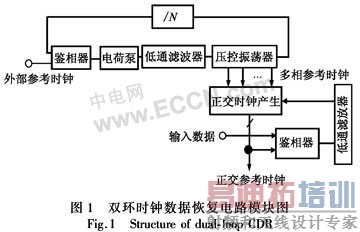

图1给出了双环时钟数据恢复环路的基本结构,其中,鉴相器(PD)比较输入数据和参考时钟的相位,必须在且只需在数据跳变处检测出两者问的相位误差,即为了进行数据的自动重定时,鉴相器必须利用时钟对数据进行采样,这就需要多点采样方案。为了满足采样要求,参考时钟相位的最小数目是2,文献[1]认为数目为4是因为每个时钟信号在差分完成方式下都自动产生了各自的互补信号,所以这里将参考时钟相位的最小数目定为2。这两个时钟的相位相邻,且呈正交关系,尽管可以采用更多的时钟相位来降低噪声灵敏度,但正交时钟产生相对简便,而且对于数据的抖动性能要求低,同时也可以降低时钟分布网络的复杂度以及功耗和面积。

1.1 传统的正交时钟产生方案

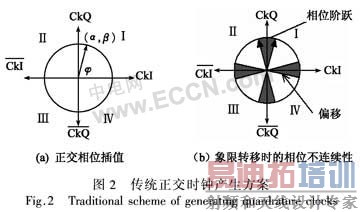

为了实现正交相位时钟,把整个360°的插值范围离散地划分为4个象限,如图2(a)所示,每个象限的插值范围是90°。当插值向量从一个象限转移到另一个象限时,时钟就被它的互补时钟所代替。为了降低抖动和相位不连续性,这种替换必须在不影响环路正常工作的情况下完成,于是采用象限边界控制单元来保证时钟的替换只发生在时钟混频权重为0的时候,这样在理论上实现了时钟相位所在象限的平滑转移。然而在实际实现时,由于各种负面因素,比如相位边界控制单元的偏移,工艺、电压、温度的变化等,会产生如图2(b)所示的相位阶跃,从而导致抖动性能的下降,时钟的偏移较大。

1.2相位插值-相位选择的正交时钟产生方案

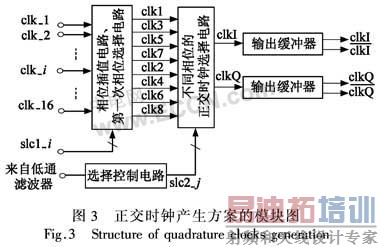

相位插值一相位选择的正交时钟产生方案可描述为:首先由图1所示的第一个环路产生16相标准参考时钟,相位间隔为2π/16,即π/8,每个时钟clk_i的相位可以表示为Pclk_i=(i-1)π/8;然后利用每两个相邻相位的时钟进行插值,从而得到32相参考时钟,此时得到的插值后时钟与其相邻时钟相位间隔为π/16,时钟clk_i和clk_i+1进行插值后得到的时钟相位可以表示为Pclk_i,i+1=iπ/8-π/16;在进行时钟相位插值的同时对32相时钟进行第一次相位选择,选择出8相两组时钟clk1~clk8,其中clk1、3、5、7组和clk2、4、6、8组的组内相邻相位问隔为π/2,而且每组内部4个时钟各有4个不同相位,相位问隔为π/16;之后根据低通滤波器对鉴相器工作结果的译码,得出在这两组正交时钟中的选择方案,即相位的选择,最后把选择后的时钟送人输出缓冲器,完成单端到双端的转换,生成各时钟的互补时钟送到后续的半速率鉴相器中完成数据的重定时工作。

这样就完成了正交时钟的生成工作,该对正交时钟在完成数据重定时的过程中,相位的调整步伐为π/16,即数据周期的1/32,可以达到数据重定时的精度要求。图3所示为正交时钟产生方案的模块图。

2 实现电路及晶体管级仿真

2.1 相位插值及第一次相位选择电路

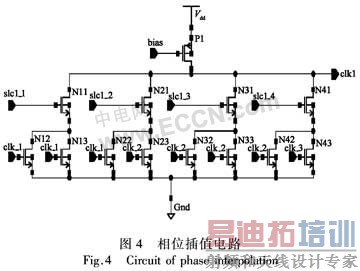

根据上文,从图1所示的第一个环路送出的16相参考时钟进入正交时钟产生模块后,首先完成相位的插值操作,生成32相参考时钟。这里把16相参考时钟信号进行相邻交叉重叠分组,共分8组,分别送人8个相位插值电路。每个相位插值电路对输入时钟完成插值操作后,经slc_i,i=1、2、3、4信号选择出一相,共得到8个相位的时钟。图4所示为一组相位插值电路图,从图中可以看出该组相位插值电路的输出时钟信号clk1的表达式为(其余7组类似)

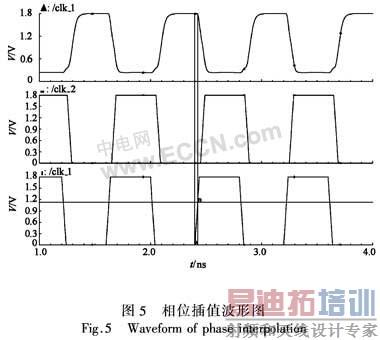

四个选择信号slcl_1、slcl_2、slcl_3、slcl_4同一时间内只有一个有效,比如slcl_2信号为高时,输出为clk_1与clk_2进行相位插值后的结果。设计中N12、N13、N22、N23、N32、N33、N42、N43具有相同的宽长比,N11、N21、N31、N41有相同的宽长比且其宽长比为N12宽长比的两倍。以slcl_2信号有效为例,输出节点clkl的上升时间由P1决定;下降时间与对clkl节点负载电容的放电电流成正比,仅由N22和N23的导通情况决定,N22和N23同时导通时其放电电流是N22和N23仅有一个导通时的两倍,将N22和N23同时导通时clkl的下降时间记为τ,则N22和N23仅有一个导通时clkl的下降时间为2τ。如果N23输入上升沿滞后于N22输入上升沿的时间小于τ,从N22输入上升沿时刻到N23输入上升沿这段时间内的放电电流是N23输入上升沿之后放电电流的1/2。记N23输入上升沿滞后于N22输入上升沿的时间为T,这种情况下总的延时约为T+(2τ-T)/2=τ+T/2;输出信号的相位位于clk_1和clk_2相位差的1/2处,实现了相位插值。其插值过程波形可用Cadence Spectre仿真得到,如图5所示。

这里注意到有些进行插值的时钟是同一个时钟信号,这是为了使各种情况下输出时钟信号的延时相匹配。

这个相位插值电路只要满足T<τ就可以在很宽的时钟范围之内实现相位插值,所产生的时钟相位与电源电压、工作温度无关,仅取决于用于插值的NMOS管尺寸的匹配程度,通过版图设计可以将用于插值的NMOS管的不匹配程度降到最低。输出相位的稳定程度只取决于输入时钟的稳定程度,不会降低电路的抖动指标。

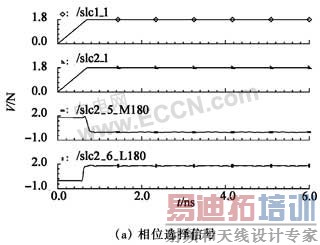

2.2不同相位的正交时钟选择电路

经过第一次时钟相位的选择,已经得到了相位正交的参考时钟,但是还需要选择用哪一对正交时钟对输入的数据进行重定时。图6所示为正交时钟的选择电路图,最终选择输出的时钟信号clkI和clkQ对应的时钟彼此正交,其相位关系与行为描述一致:slc2_5信号有效时,clkI的相位在π和2π之间,按照slc2_1、slc2_2、slc2_3、slcl_4的顺序依次有效,输出时钟clkI的相位递减,步长为π/4;slc2_6信号有效时,clkI的相位在0和π之间,按照slc2_1、slc2_2、slc2_3、slcl_4的顺序依次有效,输出时钟clkI的相位递增,步长为π/4。

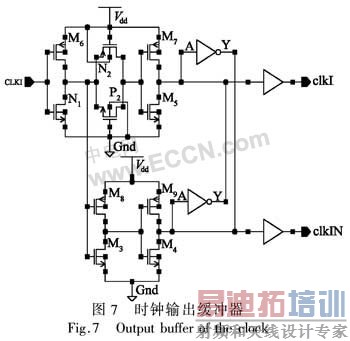

2.3时钟输出缓冲器

为了增加电路的驱动能力,并产生两个正交时钟的互补信号用于后续的半速率鉴相器等电路,在把时钟信号clkI和clkQ送人后续电路进行数据恢复之前,先将其送入如图7所示的时钟缓冲器。时钟信号在此经过缓冲放大,而且两个互补时钟信号的输出彼此构成正反馈,提高了转换速率。

2.4 总体电路的晶体管级仿真

采用Cadence Spectre在0.18μm CMOS工艺库下对整个电路进行晶体管级仿真,结果如图8所示。电路的输入是16相频率为1.25 GHz,即周期为800 ps、相邻相差为π/8,即相差50 ps的时钟,以及相位选择信号,从图8可以看到插值后的时钟与预期一致,所分两组时钟组内相差为200.47 ps和201.472 ps,呈正交关系。

3 结论

本文描述了双环时钟数据恢复电路利用相位正交的参考时钟进行工作的原理,通过对传统的正交时钟产生过程的分析和现有电路的改进,提出了一种相位插值一相位选择产生方案,并进行了理论分析,同时在TSMC 0.18μm CMOS仿真工艺Spectre环境下进行了验证。该电路与电源电压、工作温度和工艺无关,在输出的相位上不会引入附加抖动,在数据时钟恢复电路中应用相比采用传统电路可以提高输入抖动容限。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:处理器设计的谬误—第二部分

下一篇:基于DDS技术的任意波形发生器研究与设计