- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

JTAG控制电路的应用与研究

所有逻辑器件的厂商生产的器件都支持JTAG加载电路,它是一种通用的加载电路.几乎所有的逻辑工程师或硬件开发工程师都曾被这种简单的JTAG控制电路困惑过.本人通过多次的现场应用,把JTAG电路的应用技巧总结如下.(以ALTERA,并且FPGA支持CPU+JTAG编程模式为例).

典型的JTAG控制电路

很多设计者在应用此电路的时候,往往达不到理想的效果.该电路使用方法不正确,可能导致如下结果:

问题一:电路无法正常加载.

问题二:电路可以正常加载,编程软件显示加载过程正常,但加载后内部逻辑被复位.(多出现在CPLD+FLASH方式和CPU+FLASH方式)

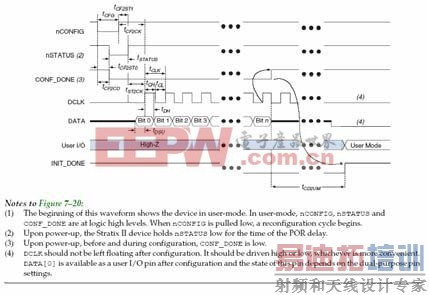

问题三:CONF_DONE信号不能够正常变高.

工程师在使用此电路的时候,不要忽略nCONFIG,MSEL[3..0]和DCLK等特殊管脚的作用,更不要忽略上拉和下拉电路的作用.

nCONFIG,MSEL[3..0],DCLK等特殊管脚的作用.

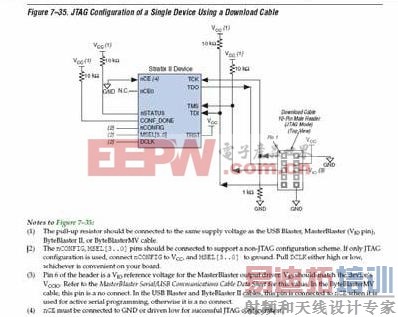

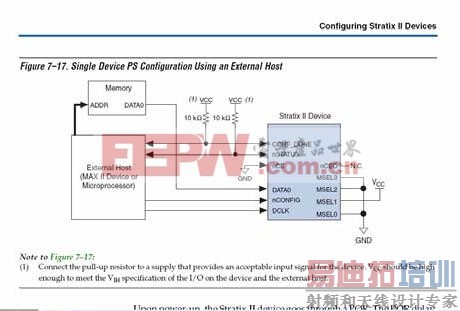

1.nCONFIG信号是FPGA的另一种加载模式PS(PassiveSerial)的握手信号,该信号低电平有效.因为PS模式的时钟可以由设计者灵活控制,并且时序简单.PS模式常用于CPU加载或CPLD+FLASH等方式的加载,以方便CPU或CPLD模拟PS的时序.其典型电路为:

CPU加载或CPLD+FLASH加载方式

PS模式时序图

FPGA既采用CPU加载又采用JTAG的加载模式.这是一种典型的应用,CPU加载可以避免使用昂贵的配置芯片,在产品量产时使用.JTAG加载模式一般用于量产之前的调试.在调试的过程中,如果不对nCONFIG信号进行正确的处理,可能导致”问题二”.从PS模式的时序图上可以清楚的看到,nCONFIG信号是低电平有效,PS的控制电路检测该信号的下降沿.如果采用CPU+JTAG模式编程FPGA,因在调试时只会用到JTAG模式,那么此时的nCONFIG必须保证为高电平.也就是PS模式无效.

2.MSEL[3..0]是ModeSelect管脚.因为FPGA支持不同的加载模式.在用到特殊模式编程FPGA时,必须把MSEL[3..0]设置为对应的状态.

从下面的注释可以看到,JTAG模式对MSEL[3..0]无任何要求,可以接’1’,’0’,NC等.由于电路支持CPU加载模式.MSEL[3..0]以PS模式的要求为准.

3.DCLK属于AS(ActiveSerial)模式的时钟管脚.AS模式是专用配置芯片和FPGA的连接电路.如果电路只支持CPU+JTAG方式,那么DCLK应为一个确定的电平,可以为高/低电平,但不能够接NC.

上拉和下拉电路的作用

Altera公司不断优化JTAG模式中的上拉和下拉电路,这是随着FPGA内部的JTAG控制的发展而发展的.这些电阻有不可低估的作用,不但需要设计者在PCB上一个不漏,而且需要灵活应用.

上拉/下拉电阻的三大作用:

1.保证电路的初始值.比如TCK信号采用下拉电阻.为什么采用下拉电阻,而不采用上拉电阻呢 因为下拉电阻使TCK信号的初始值为0,由于是时钟信号,可以保证时钟信号在初值后第一个边沿为上升沿,而JTAG控制电阻正是以TCK的上升沿向FPGA内部写配置数据的.

2.这里的上/下拉电阻仅仅属于推荐值,并非确定值,目的是保证信号质量.以上拉电阻为例,如果上拉电阻为10K以上,由于管脚对地有一个等效电容,由于T=RC,C由器件的工艺决定,电阻越大,充放电时间越长,信号的上升沿就越缓慢,斜率就越小.上升时间如果超过JTAG控制电路的要求,向FPGA内部写数据就可能出错.那么,如果上拉电阻越小呢 会不会上升时间变小呢 是的.电阻变小,上升时间变小,斜率变大,但是却带来了另一个严峻的问题,如果电阻小到一定程度,信号将在上升沿出现上冲现象,情形严重时会出现信号的振铃.如果电阻太小,产生的倒灌电流超过器件IO的容限,JTAG控制电路会烧坏.[p]

那么,这个电阻究竟多大才满足一般PCB的要求呢 一般情况使用4.7K.

3.保证信号的驱动能力.前面提到,电阻越小,信号的斜率越小,同时信号的驱动能力越强.电阻越大,信号斜率越大,同时信号的驱动能力越弱.这一点在JTAG菊花链电路中有及其重要的重要.

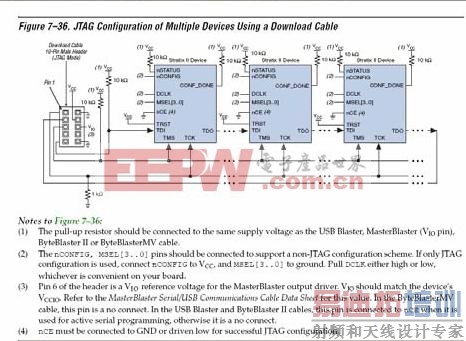

JTAG菊花链电路

如有多个FPGA在同一板卡中,在板卡集成度较高的情况下会采用该电路.一般情况,菊花链不超过3三级,也就是不超过三个FPGA时,可以采用上述电路.由于JTAG控制电路的信号的吸电流较大,加上PCB走线的功率损耗,可以通过调节上/下拉电阻的方式来调节信号的驱动强度.

如果菊花链超过三级,也就是超过三个FPGA.则推荐使用Buffer增强JTAG各个信号的驱动强度

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:DDR2

SDRAM介绍及其基于MPC8548

CPU的硬件设计(08-100)

下一篇:基于故障注入的基准电路故障响应分析