- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的线阵CCD驱动时序及 模拟信号处理的设计

电荷耦合器CCD具有尺寸小、精度高、功耗低、寿命长、测量精度高等优点,在图像传感和非接触测量领域得到了广泛应用。由于CCD芯片的转换效率、信噪比等光电特性只有在合适的时序驱动下才能达到器件工艺设计所要求的最佳值,以及稳定的输出信号,因此驱动时序的设计是应用的关键问题之一。通用CCD驱动设计有4种实现方式:EPROM驱动法;IC驱动法;单片机驱动法以及可编程逻辑器件(PLD)驱动法。

基于FPGA设计的驱动电路是可再编程的,与传统的方法相比,其优点是集成度高、速度快、可靠性好。若要改变驱动电路的时序,增减某些功能,仅需要对器件重新编程即可,在不改变任何硬件的情况下,即可实现驱动电路的更新换代。

2 CD 1501D CCD工作参数及时序分析

2.1 TCDl50lD CCD工作参数

所选器件是日本TOSHIBA公司的TCDl50lD CCD作为光电传感器,该芯片是高灵敏度、低噪声和宽动态范围的线阵CCD器件。主要参数如下:

光敏像元数:5000个 像元尺寸:7μm×7μm×7μm

光谱响应范围:300~l 000 nm灵敏度:10.4~15.6V/Lx.s

动态范同典型值:3 000 nm饱和曝光度典型值:0.23Lx.s

驱动时钟频率最大值:12 MHz

该器件正常工作的驱动脉冲主要有:复位时钟RS、移位脉冲φ1、φ2和转移脉冲SH。该器件具有5 000个有效像元,正常工作还需要76个虚设单元输出(dummy outputs)信号。由于该器件是两列并行传输,所以在一个周期内至少需要2538个φ1(或φ2)时钟脉冲才能完成一帧图像转移。

2.2 驱动时序分析

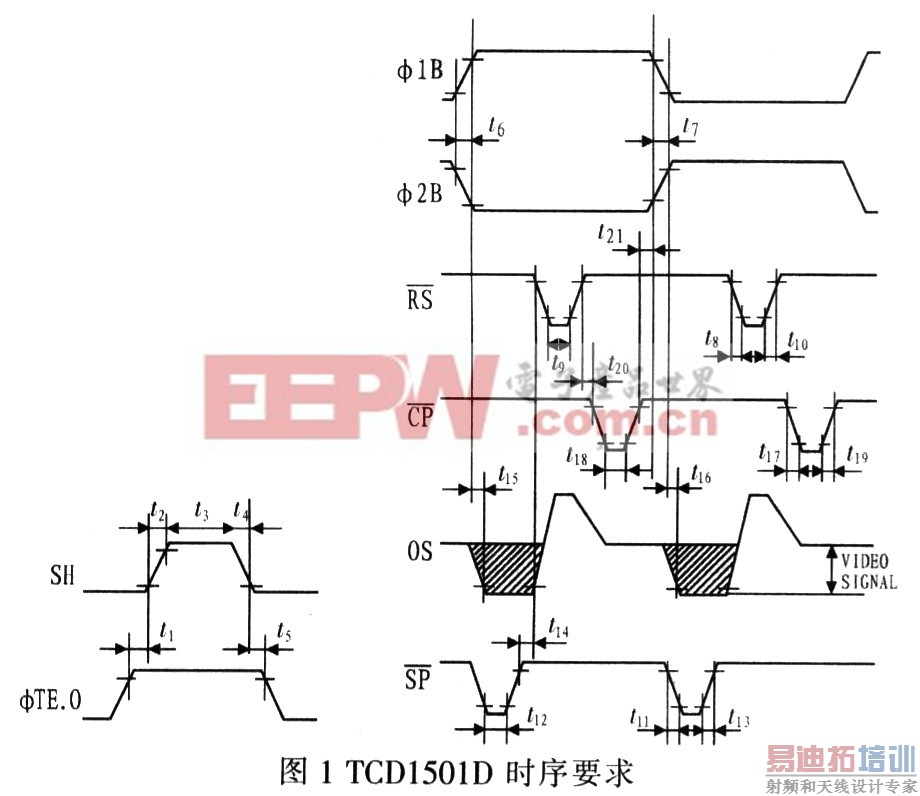

各驱动时序之间正确的先后关系是保证CCD正常工作的前提。具体时序关系如图1所示。

3 CCD输出信号的采集

CCD器件输出的原始信号中除了有用的信号外,还夹杂着各种噪声和干扰,主要有光子噪声、散粒噪声、暗电流噪声、复位噪声以及输出噪声等,而影响最大的是复位噪声。通过理论及实验可知,相关双采样是消除复位噪声最有效的方法之一。其原理是利用复位噪声在同一像素周期内近似为常数,因此,只要把同一像素周期内的参考电平和信号电平进行两次采样,再进行相减,即可消除复位噪声。

3.1 内部信号处理

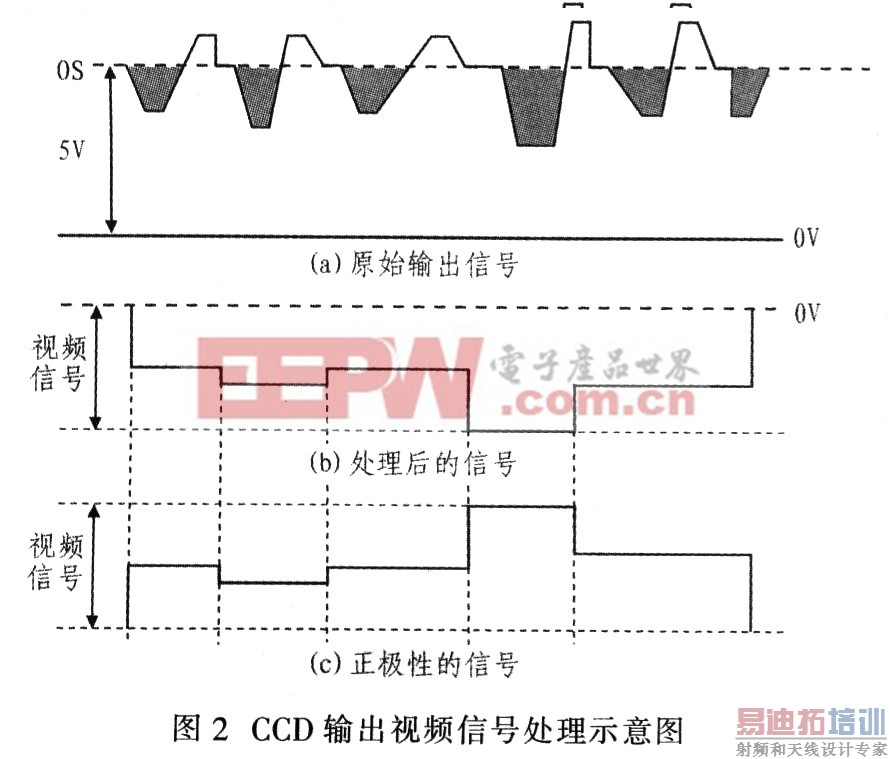

与其他线阵CCD不同的是TCDl50lD内部包含有采样保持电路。由图1可知,OS经SH脉冲采样后,得到所有视频信号的包络,经CP箝位电平后输出一个大概为5 V左右的直流分量,两个波形再通过差分即可得到有用的视频信号。若要保证信号的不失真输出,则t12和t18需越小越好,必须满足时间最小值要求,即让采样脉冲SH和箝位脉冲CP对OS信号在很短时间内准确地对阴影部分信号电平和参考电平分别进行采样,然后两者差分。输出视频信号的示意图如图2所示,图2(a)中的阴影部分是有用的视频信号,白色部分是参考电平,图2(b)是相关双采样后CCD每个像元中视频信号包络的集合,是一个负极性的离散模拟信号,图2(c)是翻转之后的正极性信号。这个过程相当于对CCD输出信号进行内部CDS,由于CCD内部时序要求非常严格,在某些情况下可以采用外部的相关双采样技术,在实际应用中可根据具体情况选择使用内部采样处理还是外部采样处理。

[p]

[p]

3.2 外部信号采集

外部电路对CCD信号采集主要包括除噪和A/D转换,前者是为了在不损失图像细节的前提下尽可能消除噪声和干扰,以获取高质量的图像;后者则是为了完成对输出信号的数字化,以便进一步进行软件处理。

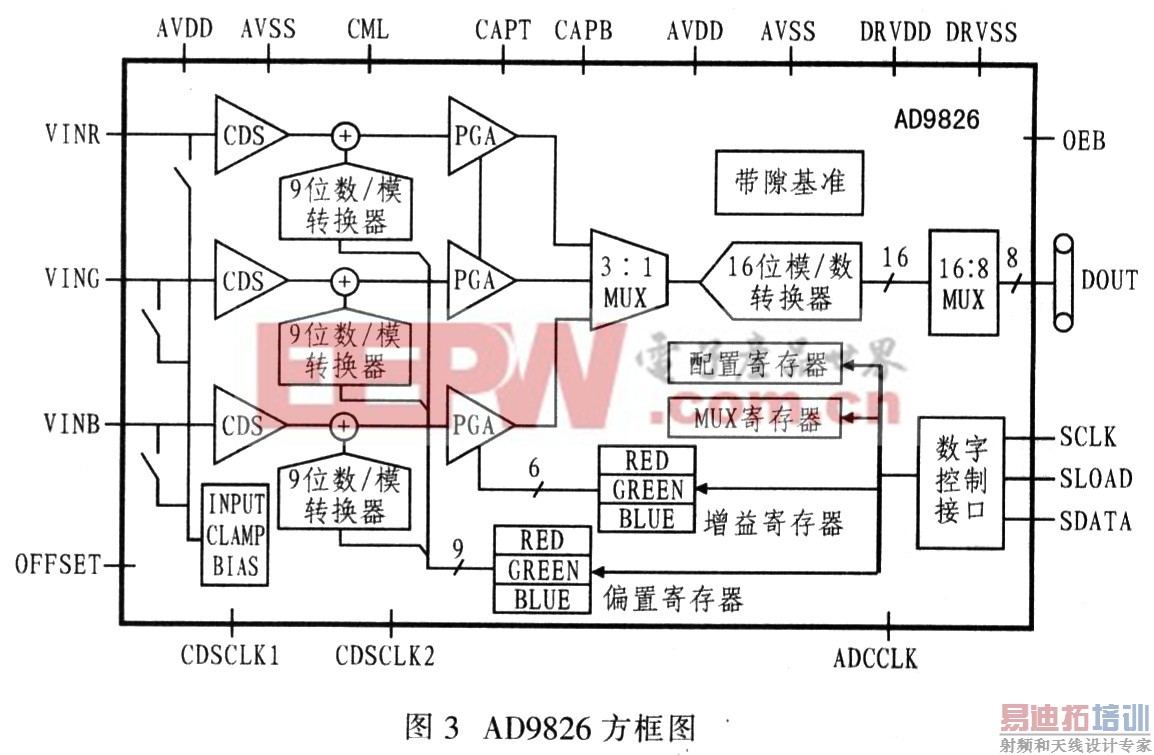

传统CCD除噪和A/D转换是采用分立电路来完成对输出信号的数字化处理,对于高速采集系统而言,传统方法显然满足不了要求。为了简化电路设计、提高系统可靠性,这里采用单片集成的CCD模拟信号的预处理芯片AD9826来完成CDS及A/D转换。该芯片内部集成了CDS电路和16位20MHz A/D转换器。而AD9826输出只有8位,因此采用分时输出高8位和低8位的方法来实现16位数据的输出.方框图如图3所示。由于AD9826对输入信号幅值的要求可以达到4V,而未经处理的TCDl501D输出信号幅值为3 V左右,其中还有一个接近5 V的直流分量,需用一个差分放大器消除直流后,再放大才能接到AD9826的输入端,实现对CCD输出信号不失真的进行处理。AD9826的CDSCLK时序驱动脉冲由FPGA产生,串口的配置可通过单片机或DSP写入。

4 时序设计及波形仿真

通过对TCDl50lD的驱动脉冲及时序关系的分析,下面将用ALTERA公司的Quartus II 7.2作为开发平台,对各路时序进行相关的设计及仿真。Quartus II 7.2开发系统是一种全集成化的可编程逻辑设计环境,它支持硬件描述语言(VHDL)、状态图及原理图3种输入方式,设计包括4个阶段:设计输入;设计实现;设计验证和器件编程。其原理输入方式简单直观,而硬件描述语言输入方式的优点是可移植性和可读性好,因而系统采用VHDL语言的输入方式。

4.1 TCDl501D时序设计及仿真

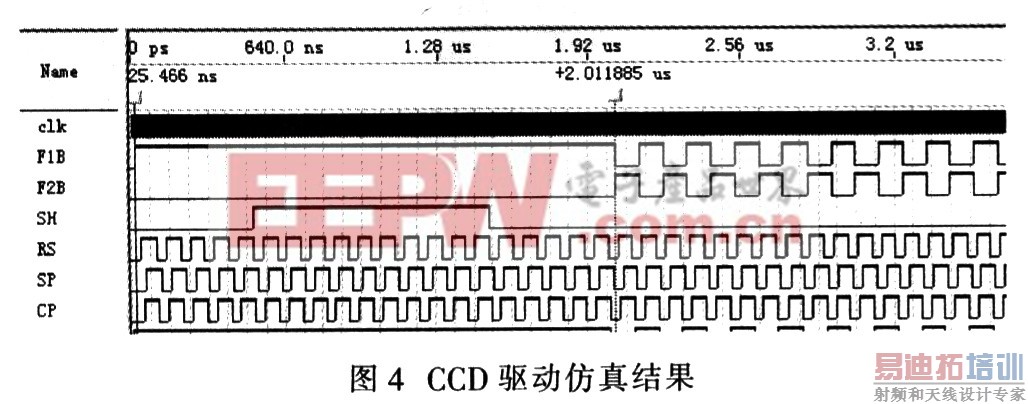

系统所选的基准时钟为100 MHz,工作频率为10 MHz。依据TCDl501D驱动时序要求,采用硬件编程语言(VHDL)的输入方式,设计出各脉冲产生的程序。各项驱动脉冲均由基准时钟分频产生。其脉冲参数分别为:φl=φ2=5 MHz,占空比为1:1,波形为方波,φ1、φ2在并行转移时有一个大于SH高电平的宽脉冲,脉宽为2000 ns;复位脉冲RS=10MHz:占空比为3:2,波形为方波;SH在转移时的宽脉冲为1000 ns;箝位脉冲CP和采样保持脉冲SP分别为RS脉冲的延迟。正确编译后,最后通过波形仿真,得到TCDl501D驱动时序的仿真波形图,仿真结果如图4所示,其中FlB、F2B分别表示移位脉冲φ1、φ2,图中+2.011885 μs线表示相对于25.446 ns的基准线偏移量,可知F1B宽脉冲几乎为2 000 ns,能满足器件手册的要求。同理,可判定其他驱动脉冲也满足要求。

[p]

[p]

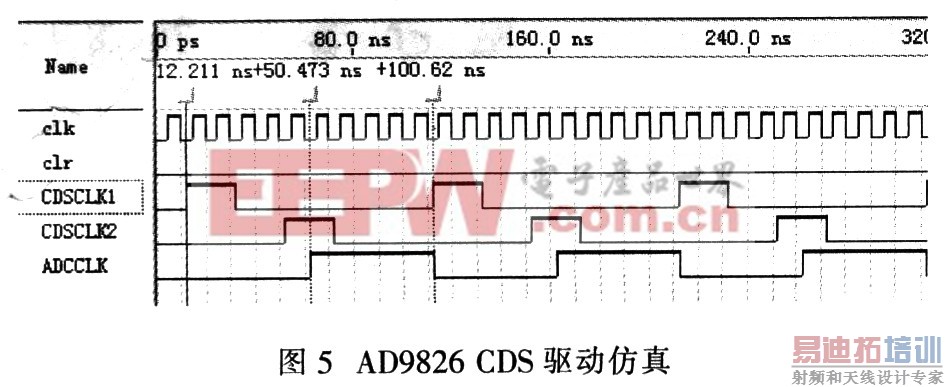

4.2 AD9826时序设计及仿真

通过对AD9826单通道CDS采样时序分析,结合TCDl501D输出信号的特点,设计出正确合理的CDS驱动时序是保证该器件正常工作的基础。充分利用硬件编程语言(VHDL)的优点,产生各项时序。依据TCDl501D输出信号OS的时序要求及AD9826对CDS的要求,可设定各脉冲的参数为:主时钟为100 MHz,CDSCLK1=CDSCLK2=10 MHz,占空比为l:4,两次采样间隔为40 ns,均为下降沿采样;AD―CCLK=10MHz,占空比为1:l,低电平有效。编译后通过波形仿真的结果如图5所示,其中12.211 ns线为基准,+100.62ns线为相对基准线的偏移量,可知CDSCLKl周期为100 ns,满足器件手册中所规定的要求。

5 结语

通过对TCDl50lD输出图像信号特征的简要分析,分别阐述了内、外2种除噪方法,并给出了相应的时序,再利用Quartus II 7.2软件平台对TCDl501D CCD驱动时序及AD9826的采样时序进行了设计及结果仿真,使CCD的驱动变得简单且易于处理,这是传统逻辑电路无法比拟的,对其他CCD时序驱动及后续处理提供了一定的参考价值。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...