- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速数据中继器设计的研究

1 前言

高速以太网可以满足新的容量需求,解决了低带宽接入、高带宽传输的瓶颈问题,扩大了应用范围,并与以前的所有以太网兼容。全双工的以太网协议并无传输距离的限制,只是在实际应用中,物理层技术限制了最大的传输距离。不过可以通过使用高性能的收发器或链路扩展器来延长以太网链路的长度。但是面向流量高达数十G的高速以太网中,如何快速、可靠地实现数据的转发与链路延伸并不是一件很容易的事情。尤其是高速以太网中,对设备时延非常敏感,因此要求数据中继设备处理速度有足够的快、同时还能够对转发的数据进行简单分析与处理,才能实现高速、可靠的数据转发功能。另一方面,在10G以太网标准出台之前,就已经有多家厂商推出了基于10G以太网标准草案的10G以太网设备。国外厂商如Foundry、Cisco、Enterasys、Extreme、Forcel0、Nortel、A1catel、Juniper、Avaya、HP、Riverstone等公司纷纷推出了10G以太网设备,国内几家著名的通信设备制造商,像华为、港湾也研发出具有自主知识产权的10G以太网产品。不同公司的产品、设备在对协议实现的一致性、互操作性、稳定性、成熟性等方面都有所不同,因此要设计并实现一个可靠、高速数据中继器必须深入研究高速以太网标准,并充分考虑其设计的灵活性,因此本文提出了一个基于FPGA的高速数据中继器设计方案。

2 高速数据中继器功能分析

高速数据中继器主要需完成以下功能是对外部光纤链路发送过来的高速、大量数据处理,主要包括有: 10G以太网的物理层处理。包括将10Gbps光信号转换为电信号和将10Gbps高速串行数据转换为低速率的并行数据,便于上层处理;10G以太网的链路层处理。包括对10Gbps数据进行PCS解码和MAC控制的链路层处理,最后输出完整的MAC帧;对MAC帧格式进行判断来识别其中封装的上层数据是协议报文还是数据报文;对IP数据报文进行查表处理,看是否有发往本机的IP报文;将需要上交到转发进行深层次IP层处理的数据报文封装成内部数据报文格式并上交;将需要上交到板极处理机的协议报文和发往本路由器的IP报文封装成内部协议报文格式并上交。

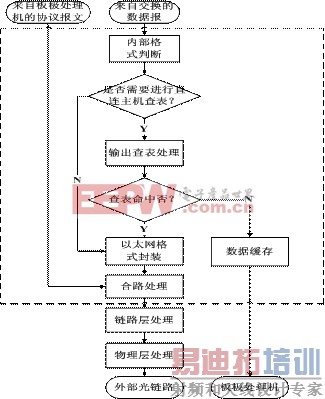

数据中继器对需要转发出去的数据需要完成如下处理:对交换发送过来的数据报文进行内部格式判断,决定是否进行查表处理;对不需要进行查表的IP报文直接从内部头中提取目的MAC地址;对需要查表的IP报文进行查表处理,若查表命中则返回目的MAC地址,若不命中则将该数据报文上交到板极处理机;对得到目的MAC地址的报文进行以太网格式封装;对板极处理机下发的协议报文和封装好的以太网帧进行合路处理;10G以太网的链路层处理。包括对MAC帧进行MAC控制链路层处理和PCS编码;10G以太网的物理层处理。包括并/串转换和电/光转换。其处理流程如图一所示

图 一:高速数据中继器数据处理流程

3 方案的选取与实现

从以上输入处理和输出处理流程来看,物理层和链路层的功能可以通过选择相应的商用器件来实现,实现起来并不复杂;但图1中虚线框内的处理功能是在10Gbps的高速率下进行的,实现起来比较困难。目前在高速数据处理中,能完成这部分功能的处理器件可分为固定功能器件和可编程器件两种,其中固定功能器件主要指ASIC(Application Specific Integrated Circuit),可编程器件又有FPGA(Field Programmable Gate Array)和NP(Network Processor)两种,下面对这三种器件进行比较。

首先能够同时提供极高转发性能和较低成本的只有ASIC芯片了。ASIC的硬件资源最为丰富,处理能力是NP不能比拟,万兆核心层设备采用ASIC是对于性能的一种保障。但是它的先天不足也是无法回避的,由于ASIC的固定特性一直无法解决路由器对多业务支持的需求,ASIC芯片一旦产出后,其原有的功能无法添加,也可以把业内目前需要的功能都做在ASIC里面,但是现在主流的很多技术如MPLS、QoS等都是只停留在草案阶段,还未标准化,所以现在就做死在ASIC里面显然是有很大风险的。由此可看出,ASIC可为任何固定功能提供高性能,但却几乎没有灵活性和可扩展性。第二种NP,目前网络处理器(NP)技术是业内非常受欢迎的技术之一,NP技术本身就是通过厂家自己编写微码的方式对网络协议处理进行优化,通过内置微引擎的方式实现加速处理,性能是CPU无法比拟的。这样的结构注定了NP就比ASIC拥有更多的灵活性,对新增业务的支持能力永远都比ASIC强。但是NP也有其自身不能克服的缺点,NP的硬件资源对比ASIC肯定还是有很大差距的,所以其在处理海量多业务时转发性能下降很快,不能达到线速。

第三种是FPGA,FPGA对任何高速并行数据处理都非常理想,具有可编程的能力和较高的灵活性,便于实现多业务支持,同时,由于其可编程性是通过硬件实现的,因此可以提供较高的高速数据处理性能。考虑到硬件的可编程性没有软件灵活,所以最新的FPGA上可以加上一个微处理器的核心(core),加上了微处理器核心的FPGA,在可编程性上变得“软硬兼备”。 除了加上微处理器的核心,FPGA芯片公司还花大力开发芯片的高速I/O,通过网络友好的功能,该类型FPGA可提供高性能数据和网络控制处理功能。这使他们成为WAN/MAN/LAN网络中专用高速数据处理的理想候选器件,并将在灵活性/性能间进行折衷的控制权交到用户手中。此外,FPGA对任何高速数据的并行处理都比较理想,而且具有非常的灵活性和扩展性,且开发周期短,能够形成具有自主知识产权的内核,最终还可以形成自己的ASIC,因此在本文设计中选择了FPGA作为高速数据处理的核心部件。[p]

根据高速数据中继器的功能需求,并考虑高速数据中继与转发中路由器的实际性能指标,确定了该高速数据中继器需要达到以下技术指标:具有10Gbit/s线速度处理40字节长IP包的能力;支持100MSPS的查表速度;可提供64K条本机地址表项。

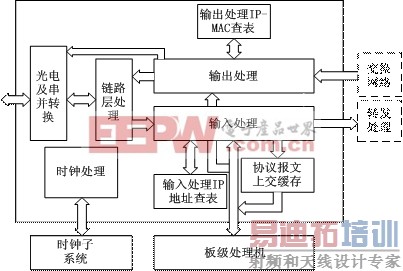

从上述三点性能指标来看,第一点通过选择性能指标高的FPGA即可实现,而第二点和第三点则无法由FPGA单独完成。从这两点性能指标来看,都是关于路由查表方面的,一个是表项容量方面的指标,一个是查表速度方面的指标。目前流行的查表方案是采用CAM(Content Addressable Memory)来实现,因此本文总体设计中也采用CAM来实现查表处理。由此得出的高速数据中继器总体设计结构如图二所示。

图 二:基于FPGA的数据中继器设计结构

在该设计结构中,输入处理和输出处理使用FPGA来实现,由于这些处理功能都是在10Gbps的高速下完成的,占用的FPGA资源较多,加之输入输出处理时都有查表模块,占用的FPGA I/O资源也较多,要在一片FPGA内完成这些处理功能是很困难的。为降低设计难度和为以后功能扩展预留一些FPGA资源,对输入处理采用一片FPGA来完成,对输出处理同样采用一片FPGA来完成。对于其他功能部分,控制管理平面(板极处理机)采用Power PC来实现,输入查表和输出查表使用CAM来实现。在10G以太网链路层处理上选用商用ASIC芯片S19205来实现,S19205可以兼容IEEE802.3ae标准,能工作在10G-LAN、10G-WAN和10G-POS(Packet Over SDH)三种模式;在10G以太网的PMA和PMD子层的功能实现上选用了Gtran公司的GT10来实现,它是一个Transponder,在内部即实现了光电转换,又实现了串并转换,通过提供不同的时钟网络配合S19205就可以实现这三种10G接入方式。对于10G-LAN接入和10G-WAN接入而言,FPGA程序的处理流程是相同的,这样,S19205在GT10的配合下,可以将10G-LAN和10G-WAN的差别屏蔽在FPGA功能处理之外,使得该设计结构既可工作在10G-LAN模式,也可工作在10G-WAN模式,达到设计复用的目的。

4 测试与分析

高速数据中继器设计制板完成后,还要将其置于整个路由器环境中进行性能测试,其测试结构如图三所示,最下面四个模块组成了高速数据中继器。

图 三:测试结构图

从图中可以看出,测试时需要两个10GbE接口,一个用于接收测试仪的数据报文,另外一个则是对经过转发处理和端口交换后的数据报进行处理后返回给测试仪进行分析。下面给出衡量系统性能的关键参数的测试情况。

测试中选用的数据包长是46、60、64、65、128、256、512、1024、1280、1508,测试时间是1分钟,测试结果如下:

图 四:系统时延测试曲线图

由于我们的中继器设计时的性能指标是可以达到10Gbps速率下40字节IP包的处理能力,在测试仪的吞吐量下不应该丢包,实际测试结构在上述10种包长的情况下,IPv4和IPv6的单播、组播包的丢包率均为0。系统时延测试结果如图四所示。从测试结果可以看出,高速数据中继器应用在高速路由器中后完全满足高速路由器对数据中继要求的各项性能指标。

5 创新点总结

本文的创新点是提出了一种基于FPGA的高速数据中继器设计方案,并综合分析了ASIC和NP等方法设计的高速网络中继器设计方法,在设计的功能和灵活性两方面做了很好的权衡。从测试结果可以看出,本文设计很好地满足了网络处理的基本功能以及高速数据中继的性能指标要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...