- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

无线传感器网络SOC芯片的低功耗设计 (1)

1. 引言

无线传感器网络(WSNs)集成了传感器技术,嵌入式计算技术,无线网络通信技术,分布式信息处理技术以及微机电技术,是当前的一个研究热点。无线传感器网络可以在广泛的应用领 域内实现复杂的监测和追踪任务,是一种随机分布的集成传感器,数据处理单元和通信的微小节点,通过自组织的方式构成的无线网络。无线传感器网络节点一般包括传感单元,嵌入式处理单元,无线通信单元以及电源自供电系统,定位系统等。作为一种特殊的Ad hoc,它除了动态拓扑,自组织,多跳路由,带宽受限等,还具有其一个极为显著的特征:对于能量的限制。所以,网络节点具有低功耗,低成本和小体积的特点。

随着IC制造工艺的迅速发展,片上系统(SOC)得到广泛的应用。SOC把系统的处理机制、模型算法、芯片结构、各层次电路及器件的设计紧密结合,在一块芯片上完成了整个系统。它相对于传统的多IC组成的电子系统有以下几个优势:低功耗、高可靠性(减少芯片对外管脚数,减少外围驱动接口单元与电路板间的信号传递,内嵌的线路可以避免系统干扰)、高集成度。

本文提出了一种无线传感器网络节点的SOC解决方案,分析了无线传感网络节点的体系结构,并从系统级,结构级,RTL级及物理设计几个方面阐述了无线传感网络节点芯片的低功耗设计。

2. SOC片上系统及VLSI低功耗实现

随着IC制造工艺的迅速发展,片上系统(SOC)得到广泛的应用。SOC把系统的处理机制、模型算法、芯片结构、各层次电路及器件的设计紧密结合,在一片完成了整个复杂的系统。它相对于传统的多IC组成的电子系统有以下几个优势:低功耗、可靠性(减少芯片对外管脚数,减少外围驱动接口单元与电路板间的信号传递,内嵌的线路可以避免系统干扰)、高集成度、较少开发成本、较短的开发周期。

VLSI低功耗设计及优化是一个非常复杂的问题,一般从下面几个阶段来考虑:

1. 系统设计阶段。在这个阶段要从软硬件协调设计综合来考虑。在实现应用功能的基础上,来选择哪些功能由硬件来实现,哪些功耗大的操作由软件来执行。同时,在系统设计,还要考虑硬件本身的电源模式:设计睡眠模式及唤醒操作。同时采用功耗管理策略,及变电压技术。

2. 结构层次。采用总线编码技术,主要是通过降低翻转活动来降低功耗。采用并行结构,用面积换性能的同时,可以把工作频率降低下来,以降低功耗。采用流水线结构,这个方法其实为重定时(retiming)的特例,通过缩短关键路径,减少路径上充放电容的数值,来减少功耗。其它的Retiming(重定时),Unfolding(展开)也可以在算法层次上降低功耗。

3. RTL级。主要通过采用低功耗的综合流程来降低功耗。在这个阶段会加入门控时钟从而降低动态翻转率。

4. 物理设计。采用多电源多阈值电压单元库,及低功耗

物理设计流程及EDA软件。设计多电源域,优化动态功耗来降低功耗。在时钟树综合时,在平衡skew的同时,尽量在翻转率较低的节点插入驱动。

3. 系统层次上的低功耗设计

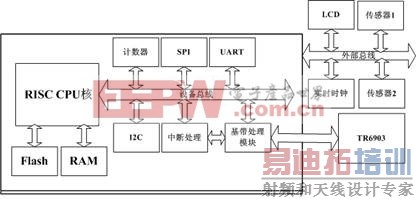

从软硬件协调工作的角度来考虑,设计出来无线传感器网络节点结构如图 1所示。整个系统通过核心单元RISC CPU核来协调各子模块的通信及工作。TRF6903芯片为低功耗低电压的多频带射频RF收发芯片,它支持315/433/868/915 Mhz可选频段,支持跳频协议,内部完成FSK/OOK调制,速度可达64kbps。TRF6903低功耗的特点使其适合于电池供电,这与网络节点的低功耗要求是一致的。

基带处理单元模块,用来实现基于IEEE 802.15.4协议的物理层及部分数据链路层的功能;数据链路层以上层协议可以采用软件实现可以节省功耗。这是因为复杂的网络层,传输层,应用层如果用硬件实现,虽然在速度上会有所提高,但是硬件复杂度也随之提高,这样必然带来功耗的提高。

图 1无线传感器网络节点SOC设计框图 [p]

在系统层次上,RISC CPU核设计了空闲模式及停止模式,来节省功耗。RISC CPU核进入空闲模式或停止模式时,CPU内部时钟停止运行,同时内部寄存器保持数据。

4. 结构层次上的低功耗设计

通过仔细分析整个SOC芯片的功耗来源,可知RISC CPU核,RAM,Flash及基带处理模块占去了绝大部分。下面从结构层次进行低功耗设计。

4.1 RISC CPU核的低功耗设计

微处理器的功耗降低可以通过降低频率,及降低工作电压的方法来解决。在网络节点SOC结构层次上的设计中,除了采用慢速时钟,及低电压供电的方法,还同时针对数据路径进行优化,主要目的是为了减少电路中不必要的翻转。指令译码数据路径的优化:一般情况下,CPU中所有的执行单元直接接在指令译码单元后面。一旦有新的译码数据输入,与其相连的所有执行单元电路也去进行翻转,造成不必要的功耗浪费。所以,在不影响时序功能的情况,设计分离的内部总线,将不执行的单元输入数据及控制信号锁存,其输入信号保持不变,动态功耗可以减少。芯片内部集成了RAM及Flash ROM。为了降低这两者的功耗,避免不必要的翻转,内部总线与RAM,Flash 的接口单元设计锁存器,这样的话,只有CPU访问相应的地址时,RAM及Flash内部才进行翻转。

4.2基带处理模块的低功耗设计

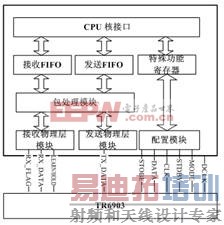

基带处理模块的设计框图如图 2所示;其基于IEEE 802.15.4协议的物理层帧及数据链路层帧结构如图 3所示。从提高cpu的效率和减少功耗角度出发,基带处理模块采用中断方式与CPU通线。基带处理模块发送完接收FIFO的数据帧,向CPU申请发送中断,等待CPU写入新的数据到发送FIFO;当基带处理模块接收到TR6903模块发来的数据帧,存放入接收FIFO中,产生接收中断等待CPU处理。

图 2 基带处理模块结构框图

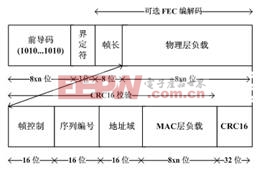

图 3 物理层及数据链路层帧结构

基带处理模块主要采用并行结构与流水线技术来降低功耗。发送功能与接收功能的物理层发送模块,缓冲区都是并行结构。配置模块也是分开来设计,数据的处理方式也是并行。包处理模块的中CRC16也是采用并行结构进行校验的。这样设计的好处,是为了在慢时钟频率下,通过并行设计提高性能,达到与高速时速一样的性能。在图 2中的各子模块与子模块之间都有流水级,也就是锁存器,不仅仅为了减少不必要的翻转,更重要的减少关键路径上的长度,从而达到间接降低功耗的目的。

基带处理模块低功耗结构设计如下:[p]

发送FIFO,接收FIFO:为接收,发送帧缓冲区,用来存放MAC层的数据负载。

SFR特殊功能寄存器:1、中断寄存器。主要有发送、接收中断标志、中断使能位,FIFO溢出标志位,发送、接收启位位。2、配置寄存器。CPU 通过写入SFR寄存器,来选择TR6903的工作模式,工作速率等。3、状态寄存器:存放FIFO的数据字节数等。

包处理模块:用硬件实现数据链路层部分功能。发送模式下,添加可变字节的前导码,3位的界定符,1个字节的帧长,可选的前向纠错编码,2个字节CRC16校验这些数据作为MAC层负载;接收模式下,包处理模块完成对数据包的解包,主要工作为前导码的检测,界定符的检测,可选的1个字节地址比较,2个字节的CRC16校验。

配置模块:配置控制模块,根据SFR中相应的配置来控制CLK,DATA,STOBE引脚的时序来控制TR6903相应的状态,实现跳频的功能。

接收物理层模块:接收控制模块,实现物理层发送数据的功能。在RX_FLAG信号为高,即检测界定符之后,在DCLK上升沿时采样RX_DATA引脚的状态,依次接收帧长字节,物理层有效负载,2个字节的CRC16校验,送给包处理模块处理,并同时从LEARN/HOLD引脚向TR6903芯片输出相应的高电平,来应答接收状态。

发送物理层模块:发送控制模块,实现物理层发送数据的功能。在DCLK的上升沿将包处理模块送来的物理层有效负载发送出去。

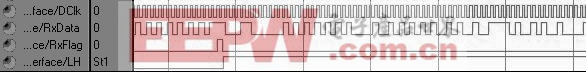

配置TR6903模式下仿真波形如所图 4示,以串行方式向TR6903写入6个字节的配置,改变TR6903工作频率,实现跳频。此时在ConfigClock的上升沿时从ConfigData送出10110010,00111010,01010110,00111010,10101010,10110010数据。Strobe为高时,ConfigClock停止。发送物理层帧部分仿真波形如图 5所示,以串行方式向TR6903发送物理层的帧。此时,先送出32位的0101…0101同步码,3个位的界字符111(TR6903检测到3个时钟周期以上的高电平),后面紧接是帧长及物理层负载。接收物理层帧部分仿真波形如图 6所示。TR6903在界定符发送完毕的最后一位,送出1个时钟周期高电平RxFlag信号;基带处理模块检测有效高电平,作为有效数据帧的开始,同时基带处理模块从LH引脚输出高电平,来响应TR6903。

图 4配置波形

图 5发送物理层帧波形

图 6接收物理层帧波形

5. RTL级及物理设计的低功耗实现

RTL级物理设计低功耗实现跟选用的EDA软件有很大关系。在0.35um CMOS工艺下,采用synopsys的Design Compiler进行低功耗综合,布局布线基于Cadence的SOC Encounter平台。用Cadence的Voltage Storm对其进行门级功耗分析,动态功耗为103.6617mw。

6. 结束语

无线传感器网络SOC芯片与传统的MSP430+TRF6903方案比较起来更有优势,前者在可靠性,功耗,面积方面都更好。此方案在FPGA验证平台上验证成功,设计的工作频率为20Mhz,速度传输率达到64kbps,满足了无线传感器网络传输速度要求;并在Cadence的数字后端平台实现芯片的后端设计,工作频率可达到100Mhz。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...