- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

动态重构两种模式的分析与对比

1、引言

随着数字逻辑系统功能的复杂化,单片系统的芯片正朝着超大规模、高密度的方向发展。然而,随着数字逻辑系统规模的扩大,在相同速度的条件下,在一定的时间区间,由于从时间轴上来看,系统中的各个功能模块并不是任何时刻都在激活或工作,所以其功能模块的平均使用率将下降。也就是说,随着系统规模的扩大,单片电路的资源利用率反而下降。因此,系统设计能不能从传统的追求大规模、高密度的方向,转向如何提高资源利用率上来呢?

FPGA动态重构技术正适应了这种要求,用有限的资源去实现更大规模的逻辑设计,大大提高了资源利用率。但它决不仅仅是一种新型功能电路的应用,其涉及数字系统设计方法、设计思想的变革,可以使数字系统单片化的设计从追求逻辑规模转向追求逻辑的分时复用;从专用的固定功能逻辑系统转向功能可自适应进化的逻辑系统。动态重构技术是未来FPGA研究和使用方向。

2、基本理论

严格来讲,系统重构的概念可分为静态系统重构和动态系统重构。静态系统重构是指目标系统的逻辑功能静态重载,即在系统空闲期间通过各种方式进行在线编程,而不是在其他部分动态运行时重载。

动态系统重构是指在系统实时运行当中对FPGA的逻辑功能实时地进行动态配置,能够只对其内部需要修改的逻辑单元进行重新配置,而不影响没有被修改的逻辑单元的正常工作。动态重构特征引出了一种新的设计思想[3]:即用有限的硬件逻辑资源来实现大规模系统时序功能;将传统的空间分布的硬件逻辑,分为器件外部特征不变,而内部逻辑在时间上交替变换的硬件逻辑,并共同在时间空间上构成系统整体逻辑功能。

当器件的同一个区域需要载入不同的设计功能并且又不需要重新配置整个电路也不影响其他电路的运行时就需要部分动态重构。这样既可以降低电路能量消耗又可以提高板子利用率、加快下载速度。

可重构系统的历史很短,目前还处于研究、验证阶段,但已经被应用到了很多方面,如军事目标匹配[4,5] 、集成电路计算机辅助设计[6]等。可重构系统研究的关键之处在于硬件方面即FPGA,有代表性的主要有MI芯片[7]、SIDSA FIPSOC结构[8]、MIT的DPGA[9]和Virtex系列,目前使用较多的是Xilinx 公司推出的Virtex系列。

Virtex器件的有效部分重构可以使用Select映射模式或者Boundary Scan(JTAG)模式下载。不需要重新配置器件也不需要下载完整的配置,新的数据只需下载到器件的可重构部分。对于目前的FPGA器件来说,数据是以column为基础下载,最小的可下载单元是一帧(frame)的配置比特流,它根据目标器件的不同而有不同的大小。

FPGA的动态可重构有两种不同的方式:基于模块(Module-based)的部分动态可重构和基于差异(Difference-based)的部分动态可重构。基于模块的部分动态可重构将设计分解成模块,对一个设计来说,每个模块都是完全独立的。如果模块之间需要交流通信,就需要一种特殊的总线宏,它允许信号穿过部分可重构的边界。总线宏为设计的内部通信提供了一个固定的总线。每次实现部分可重构时,总线宏就用来确保模块间布线通道没有改变,保证正确的连接。而基于差异的部分可重构只是比较部分重构前后的电路差别,产生一个只包含重构前后设计差别的比特流。

3、基于模块的部分可重构

部分可重构定义了一些特殊的区域,这些区域可以在器件的其他部分还在运行的情况下进行重构,这些特殊区域称作可重构区域。基于模块的部分可重构就是将电路功能划分成一个个的模块,这些模块包括可重构模块(可以实现重构的特殊区域)和固定模块(功能不变不能实现重构的区域)。其中可重构模块是重构技术的关键,具有以下特性:

重构模块的高度是整个器件的高度。

重构模块的宽度最小可以是四个slice最大可以到整个器件的宽度,但必须以四的整数倍个slice增加。

重构模块放置的水平坐标必须是四的整数倍个slice的边界,例如:左边边界可以放置在x=0,4,8,……

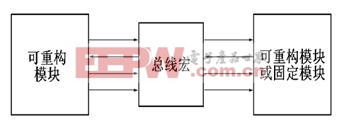

可重构模块和其他模块之间的通信(包括可重构模块和普通固定模块之间、可重构模块和 可重构模块之间)都是通过使用特殊的总线宏,如图1。

图1 总线宏用作模块内部通信

重构模块宽度范围内包括的所有逻辑资源都被看作是可重构模块的一部分,包括slice、TBUF、RAM块、乘法器、IOB和布线资源。

时钟逻辑和可重构模块是相互分离的,时钟和比特流是相互独立的。

可重构模块上部和下部的IOB是可重构模块资源的一部分。

如果一个可重构模块贯穿了整个板子的左部和右部,那么每一边的IOB都是可重构模块资源的一部分。

为了降低设计难度,要尽量减少可重构模块的个数(理想状况下,如果可能的话,最好只有一个可重构模块)。

可重构模块的边界不能改变。任何一个可重构模块的位置、所占据的区域都是固定的。

为了保证重构的时候实现合适的操作,需要外在的握手逻辑。

在可重构过程之前和之后,要保存可重构模块内的存储元素的状态。

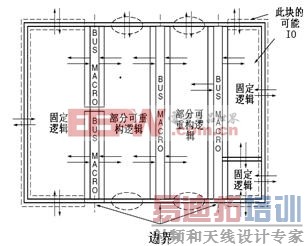

如图2所示,是一个具有两个部分可重构模块的设计,各模块间都是通过总线宏来通信。通过合理的时序控制,实现在其他电路还在运行时的动态配置重构模块,实现硬件复用。从而用更少的硬件资源去实现更大的系统功能,提高资源利用率。同时,可重构模块比整个系统小很多,下载速度也得到大大提高。[p]

图2 具有两个可重构模块的设计布局图

4、总线宏的通讯

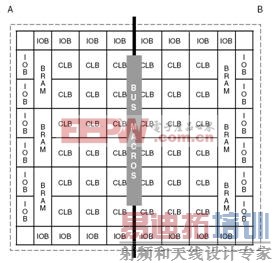

为了促进可重构模块之间的通信,需要保证穿过可重构模块边界的布线资源是完全固定而且必须是静态的,这就需要一种特殊的总线宏。如图3就是所需的这种总线宏。

其中,左边的A是一个模块,右边的B是另一个模块,A或者B是可重构模块,或者AB全是可重构模块。A和B中间的总线宏,就是支持AB之间通信的特殊总线宏。它保证AB间布线资源的不变性。也就是说当一个模块进行重构时模块内部信号用到的布线资源不能改变。如图3,总线宏是两个模块间的一个固定的布线桥。它是一个事先已经布线好的用来确定精确布线轨道的宏,并且在编辑改变的时候保持不变。对于每个不同的设计应用来说,它是一个绝对固定不变的总线宏。

图3 总线宏

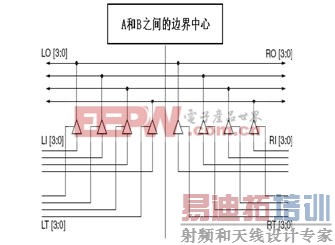

目前使用的总线宏由八个三态缓冲器组成如图4。总线宏允许信息双向传递,一个比特的信息使用一个三态缓冲器的长线。Virtex器件的每一行支持一个总线宏的四个固定的通信。总线宏的信息通讯是双向的,既可以从左到右又可以从右到左。但是对于这个设计来说,一旦信息通信方向确定以后就不能再改变。

图4 总线宏的物理执行

5、基于差异的部分可重构

基于差异的部分可重构比较重构前后的电路差别,产生一个只包含重构前后设计差别的比特流。可以使用两种方法来改变设计、产生重构前后的差别,分别是前端改变(HDL描述)和后端改变(NCD文件)。使用前端改变,设计必须重新综合,创建新的NCD文件。后端改变只需直接修改NCD文件,不必重新综合,可通过FPGA Editor工具修改NCD文件。

在FPGA Editor中可以进行三种方式的修改:改变I/O标准、BRAM内容、LUT设计。其中可以选择的最小逻辑元素是slice。首先打开NCD文件,看到逻辑块后找到可选择的最小逻辑元素slice,打开slice的结构图窗口,可以分别将重构前的I/O标准、BRAM内容、LUT设计修改为重构后的形式,如图5所示。

图5 改变LUT设计

以上三种修改都符合有效的重构流程。除了这三种方式还有其他的修改方式,比如:颠倒极性、振荡器的初始化和重新设置值、上拉、下拉外部管脚或者RAM写方式。所有这些特性都能够在实际的slice、RAM逻辑块或IOB中修改。但是,最好不要进行任何有可能影响布线或者产生内部连接冲突的修改行为。

实现上述修改后,使用BitGen就可产生可下载的差异比特文件。可重构前后开关配置的改变非常迅速,比重新配置整个电路要快很多,就像差异比特流比整个电路的比特流小很多一样,所以能够迅速而简单的下载到电路中。

6、结论

当电路只需要修改比较少的内容时,往往选择基于差异的部分可重构。差异比特流比整个电路的比特流小很多,所以能够迅速下载到电路中。

但是如果电路功能比较复杂则差异文件会非常庞大,部分动态重构的优势并不十分明显。所以基于差异的部分可重构只适用于功能简单的电路,对于功能复杂的电路需要使用基于模块的部分可重构。

综上所述,基于差异和基于模块的部分动态重构都可以大大节省系统的硬件资源,加快文件的下载速度,提高资源利用率,相信会有广阔的研究和应用前景。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...