- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于LVDS总线的高速长距数据传输的设计

随着接入通信设备的广泛应用,数据传输速率急剧增加。采用低电压差分信号LVDS(Low-Voltage Differential Signalings)技术的设备电路系统可使传输速度每秒高达数百Mb。但LVDS只能满足短距离的数据高速传输,而不支持长距离传输。目前许多设备都要求具有长距离传输数据能力,以确保百米以上的电缆传输数据。自适应均衡器能够自动补偿信号损耗,使电缆传输的串行数字信号能够重新恢复其原有性能。利用这一特点,并采用高速串行数字接口SDI(Serial Digital In―terface)自适应电缆均衡器及电缆驱动器构建系统,可扩大LVDS技术的数据传输范围,实现高速长距离数据传输。因此,这里给出采用DS92LVl023型LVDS器件,CLC006型高速驱动器以及CLC014型自适应均衡器构建的系统设计,该系统能够实现导弹飞行前实时检测的数据传输。

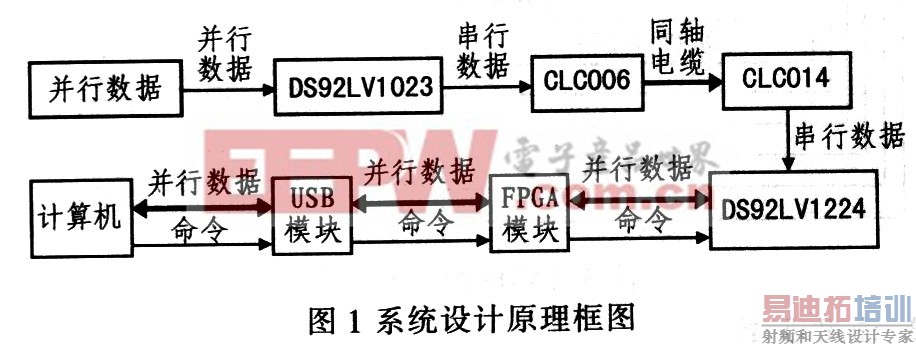

2 总体设计方案

该系统设计要求在100Mb/s速度下传输数据,其传输距离为300 m,因此,该系统设计主要解决延长传输距离和速度匹配问题。图1为系统设计原理框图。其中,DS92LVl023和DS92LVl224型LVDS器件,分别称为串行器和解串器。串行器是一种将并行数据转成串行数据的器件,而解串器则是将串行数据转成并行数据的器件。CLC006和CLC014分别是高速驱动器和自适应均衡器,高速驱动器可驱动同轴线传输更长距离,经电缆长距离传输的信号会出现衰减,自适应均衡器则用于均衡器电缆传输的信号。

3 硬件电路设计

该系统设计中,计算机与USB模块通过USB电缆连接,计算机向USB模块发送读数命令,启动DS92LVl224命令及其他操作命令,USB模块再将控制命令传给FPGA模块,FP-GA直接控制LVDS器件工作。由于USB模块向计算机传输数据的速度最高可达140 Mb/s,因此。可将100 Mb/s速率的数据适时地传入计算机。

3.1 延长距离设计

LVDS信号传输是依靠串行器和解串器完成的,串行器和解串器都需一个外部时钟。只有这两个外部时钟频率同步时,串行器和解串器才能正常通信。利用FPGA引脚与内部逻辑,完全能够解决工作时钟频率同步的问题。

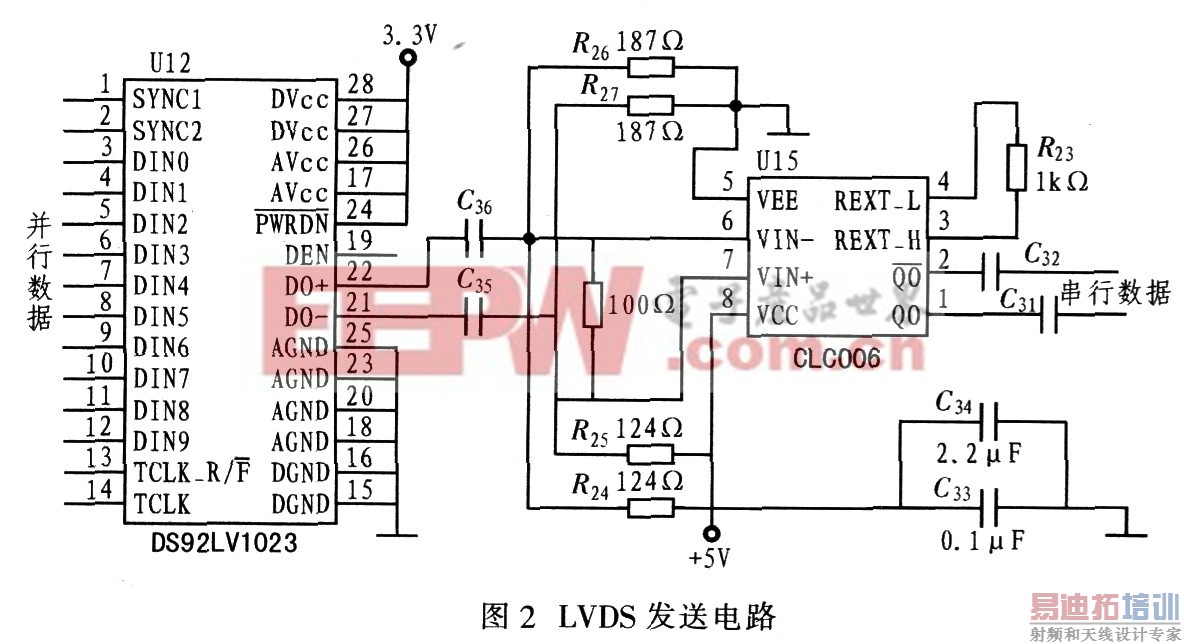

串行器DS92LV1023是将外部并行数据串化成串行数据,此时该串行器输出的差分压差约100 mV,该差分压差传输距离只有几米,加上CLC006电缆高速驱动器,其输出压差可达2V(压差可通过电阻R23调节),这样就可以驱动同轴电缆传输300 m的距离。图2为LVDS发送电路。

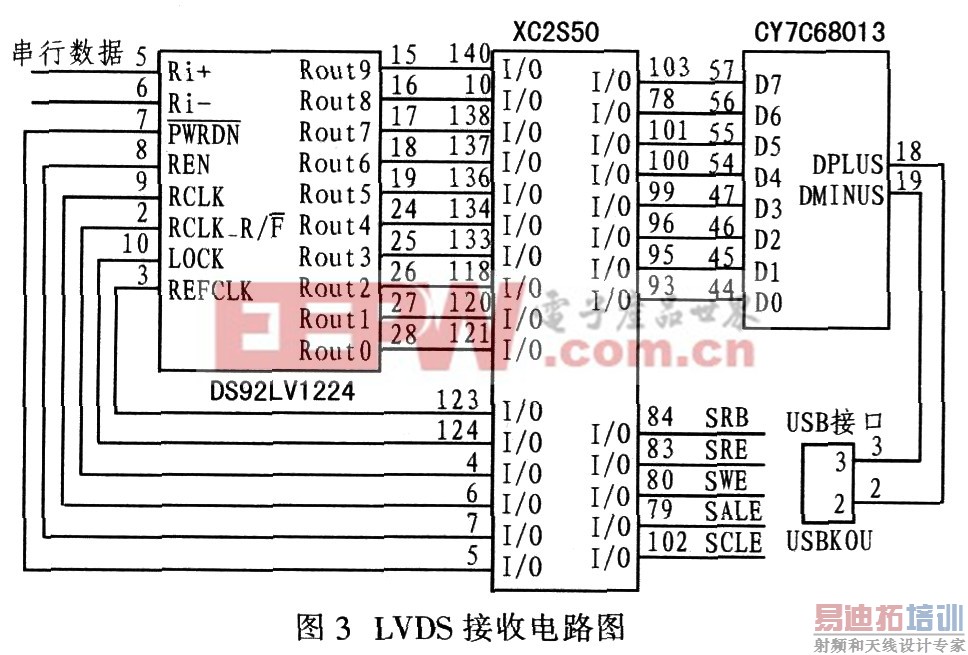

解串器DS92LV1224解串的数据先经FPGA模块传输至存储器,FPGA接收到USB模块命令后,先通过控制解串器DS92LVl224的PWRDN、REN、RCLK、RCLK_R/F及REFCLK引脚使LVDS器件开始解串.同时将解串数据直接施加到FPGA引脚,进一步处理分析。图3为LVDS接收电路。

[p]

[p]

3.2 速度匹配

由于LVDS传输的信号是数据采集系统所采集的数据,该数据的传输速率只有几百KB,而LVDS器件的传输速度范围为10~66 MByte/s,采用间歇式传输,但在传输中断后,再次传输需要500μs的同步时间,所以若LVDS器件采用间歇式传输,将丢失500μs的数据,故不能采用该种传输方式。

串行器DS92LV1023和解串器DS92LV1224有10个数据引脚,数据都是8位,一般有2个数据引脚不同,但这里则采用这两个空数据引脚:先将采集的数据暂存到FPGA的内部FIFO中,当FIF0中数据达到10个字节以上时,通知FPGA模块将数据和时钟赋到串行器DS92LVl023的引脚传输数据,同时FPGA向串行器DS92LV1023的第Data8位赋值为“0”;当所采集的数据传输完成后,增加一些其他数据,使LVDS持续传输,与此同时,FPGA将串行器DS92LV1023的第Data8位赋值为“l”。

数据接收端上传至计算机的速度匹配。USB模块向计算机上传数据也采用间歇式传输方式,即USB模块每传输512个字节,需停止几个μs。所以可利用FPGA的一个内部FIFO,先将数据暂存到内部FIFO中,等到FIFO中数据达到512个字节后通知USB模块读取数据,然后返回到计算机。

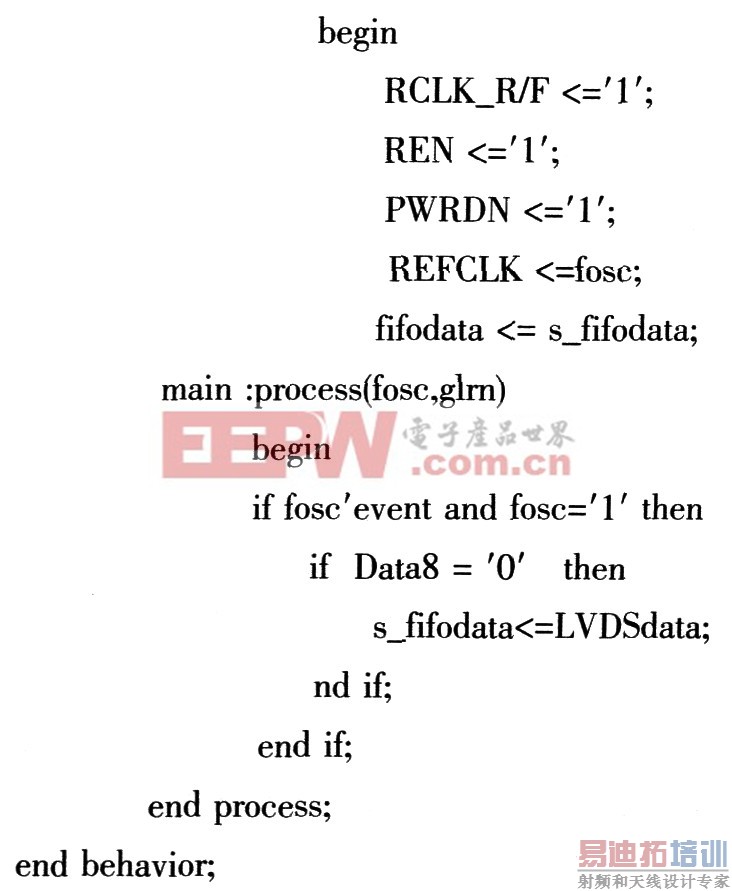

通过FPGA控制解串器DS92LVl224的PWRDN、REN、RCLK、RCLK_R/F及REFCLK引脚使LVDS器件开始解串,由于解串器DS92LV1224解串的数据分为采集的真正数据和用户添加的数据。所以,要先过滤掉添加的数据,再通过FPGA判断DS92LVl224的Data8位,如果Data8为“0”,则将数据存到FPGA的FIFO中,其部分程序代码如下:

4 实验结果

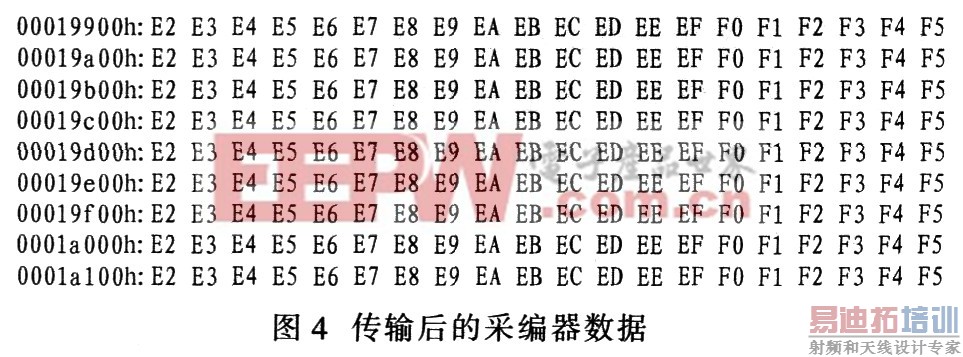

图4是该系统模拟某型号弹上采编器采集自加计数器数据,经300 m传输距离后得到的部分数据,数据准确无误。

5 结论

介绍一种基于LVDS总线的高速数据传输系统的设计方案旧,详细描述了FPGA对LVDS器件工作状态和FPGA与单片机相互之间的工作。该系统设计已投入应用,其性能可靠、稳定,适用性强。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...